# 基于 Hi3559 的多路 HD-SDI 视频传输系统

王 毅, 张 禹, 钱宏文

(中国电子科技集团公司第五十八研究所, 江苏 无锡 214072)

**摘要:** 为了在工业现场和安防监控领域更好地利用 Hi3559 强大的视频图像处理能力实现高清视频的远距离传输和智能算法, 采用 Hi3559+FPGA 硬件架构, 通过高清数字接口(High Definition Digital Interface, HD-SDI)视频均衡器利用同轴线缆传输方式, 设计实现了多路 1080P 的高清视频传输系统。该设计系统方案主要是解决了 Hi3559 虽然支持多种 Sensor 视频接口, 但是没有可以直接支持多路 HD-SDI 摄像头的输入方式和设计方案。该系统利用 Hi3559 实现了 8 路 HD-SDI 视频图像的采集、传输、处理、以及全景显示。相比海思常见的相机串行接口(Camera Serial Interface, CSI)传输方案, 采用 HD-SDI 传输距离更远, 理论可达 200 m。通过测试和验证, 该设计方案可行, 传输距离远, 工作稳定可靠, 对于多路 HD-SDI 视频的采集传输和全景显示等方向具有较高的推广和应用价值。

**关键词:** Hi3559; FPGA; 高清数字接口(HD-SDI); 均衡器; 1080P; CSI

中图分类号: TN941.1

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211439

中文引用格式: 王毅, 张禹, 钱宏文. 基于 Hi3559 的多路 HD-SDI 视频传输系统[J]. 电子技术应用, 2022, 48(3): 83-87.

英文引用格式: Wang Yi, Zhang Yu, Qian Hongwen. Multi-channel HD-SDI video transmission system based on Hi3559[J]. Application of Electronic Technique, 2022, 48(3): 83-87.

## Multi-channel HD-SDI video transmission system based on Hi3559

Wang Yi, Zhang Yu, Qian Hongwen

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** In order to make better use of Hi3559's powerful video image processing capabilities in the field of industrial sites and security monitoring, to achieve long-distance transmission of high-definition video and intelligent algorithms, adopting Hi3559+FPGA hardware architecture, using the coaxial cable transmission method with the high-definition digital interface (HD-SDI) video equalizer, this paper designs and realizes the multi-channel 1080P high-definition video transmission system. This design system solution mainly solves that although Hi3559 supports a variety of Sensor video interfaces, it does not have an input method and design solution that can directly support multiple HD-SDI cameras. The system uses Hi3559 to realize 8-channel HD-SDI video image acquisition, transmission, processing and panoramic display. Compared with HiSilicon's common camera serial interface(Camera Serial Interface, CSI) interface transmission scheme, HD-SDI transmission distance is farther theoretically up to 200 m. Through testing and verification, the design scheme is feasible, long transmission distance, stable and reliable, and has high promotion and application value for the acquisition and transmission of multi-channel HD-SDI video and panoramic display.

**Key words:** Hi3559; FPGA; high definition digital interface(HD-SDI); equalizer; 1080P; CSI

## 0 引言

HD-SDI(高清数字接口)标准最早由电影与电视工程师协会(SMPTE)提出, 协议规定了利用 YCrCb 的色彩空间采用 4:2:2 的采样格式传输高清无压缩的 SDI 视频信息<sup>[1]</sup>, HD-SDI 由亮度和色度两个单元组成, 每个单元分别为 10 bit 的数据信息。SMPTE 通过制定标准的 274M 和 296M<sup>[2]</sup>, 包含了常见的不同速率和分辨率的视频格式。HD-SDI 主要用来传输 1080P 或 720P 的高清视频信息<sup>[3]</sup>, 速率为 1.485 Gb/s 或 1.485/1.001 Gb/s 两种。串行数字接口的特点是采用了无损和非压缩的传输原理, 在同轴线缆上传输高清无损视频, 具有传输原理简

单可靠、视频清晰度高、链路延迟小、实现容易等优点。HD-SDI 视频分辨率高, 动态范围广, 在对比度、亮度、白平衡<sup>[4]</sup>等方面具有显著的优势, 在各种电视广播、监控安防和高清传输领域使用愈加广泛。

Hi3559 作为华为海思推出的一款强大片上系统(System on Chip, SoC)芯片, 不仅具有丰富的视频和各种外围接口, 而且内部集成了很多视频图像处理模块, 处理器支持不同格式视频的编码和解码、图形的畸变校正、去噪, 以及镜像、旋转和色彩的增强等, 可用于多路 Sensor 视频的输入, 内部集成 H.265 编解码处理单元, 能够支持高清的 RAW 原始码流视频的输出, SoC 内部

含有高性能图像信号处理器(Image Signal Processor, ISP)<sup>[5]</sup>, SoC 使用了低功耗的架构和工艺技术, 支持多路全景硬件拼接<sup>[6]</sup>, 为使用者提供了高性能的硬件平台。

近年, 视频监控在国内外发展很快, 已广泛应用于汽车电子、工业现场和安防监控领域。为了解决单个摄像头在获取监控场景时存在的视场不够的问题, 多路摄像头进行视频的采集和传输系统发展越来越重要。多路视频传输系统能够将目标物体四周的场景进行无盲区显示<sup>[7]</sup>, 在车载辅助驾驶、大型活动现场、高清视频监控、全景地图<sup>[8]</sup>等各种视频监控场所和领域有着广泛的需求和应用。

Hi3559 的视频接口虽然支持多种 Sensor 接口, 但 Sensor 大多是基于移动行业处理器接口(Mobile Industry Processor Interface, MIPI)接口, 无法实现长距离传输, 同时也没有现成的可以同时对接多路 HD-SDI 摄像头的输入方式。因此, 本文设计开发了一种基于 Hi3559+FPGA 的硬件设计方案, 通过软硬件的开发和验证, 该设计实现了 8 路 HD-SDI 视频图像的采集、传输和处理, 最终通过使用显示屏实现了 8 路 HD-SDI 视频的实时监控和整体显示。

## 1 系统设计

### 1.1 系统框架和工作流程

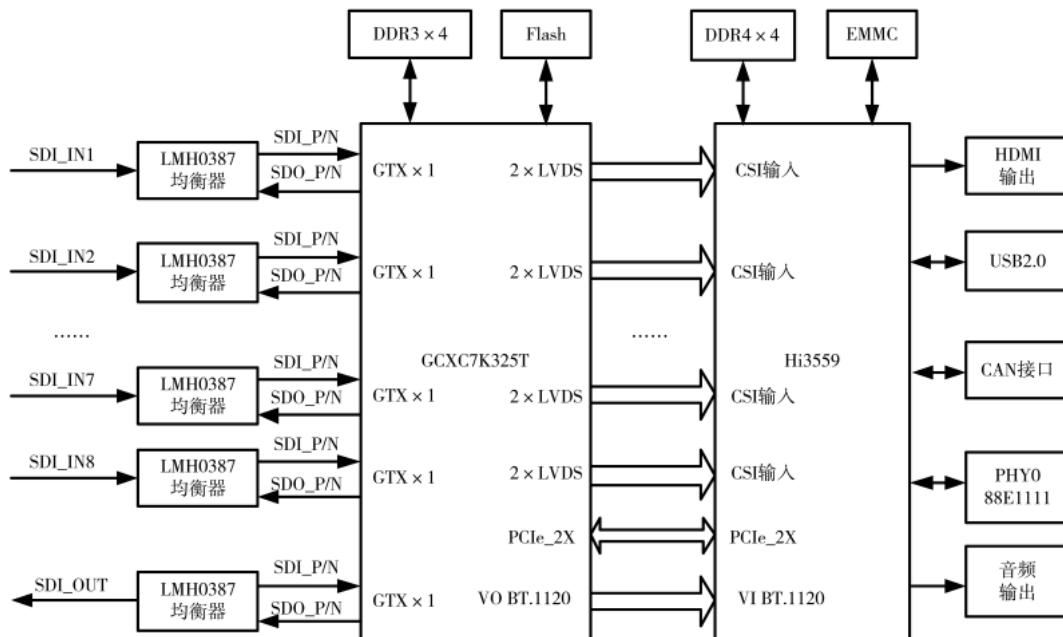

多路 HD-SDI 视采集系统采用 CPU+FPGA 硬件架构实现, 核心器件选用国产化器件, 系统主要由国产化的 CPU、国产 FPGA、SDI 均衡器、DDR4、DDR3、SPI Flash、EMMC 以及时钟和电源组成, 系统整体框图如图 1 所示。

传输系统的主要工作流程如下:

(1) 均衡电路接收外部摄像头的 HD-SDI 格式视频信号后发送给 FPGA 的 GTX 接口;

(2) FPGA 内部通过 IP 核进行解串, 获取到标准的 20 bit 的 HD-SDI 视频数据信息<sup>[9]</sup>;

(3) FPGA 将多路 HD-SDI 视频数据, 通过 LVDS 接口将有效的数据和效应区数据信息统一发送给 CPU(黑白按照 8 bit 传输亮度信息 Y, 彩色时按照 16 bit 传输亮度 Y<sup>[10]</sup>和色度 Cb/Cr<sup>[11]</sup>);

(4) Hi3559 的输入接口通过识别固定的同步码和解析行场信息, 获取到有效的视频流数据和视频的宽和高后, 通过视频处理子系统(Video Process Sub-System, VPSS)抓取相应的视频码流。

(5) VPSS 接收到视频流后通过内部处理或传递给其他硬件单元进行处理, 处理完成后送入视频输出通道, 利用视频输出接口 HDMI 进行输出和显示。

### 1.2 系统硬件构成

CPU 选择华为海思的 Hi3559 处理器, 主要用于完成多路视频的接收和传输, 以及后期的算法处理、视频数据处理后的输出, 并且扩展了 2 路千兆以太网接口用于对外通信和数据的传输。

FPGA 选择国产高性能的 GCXC7K325T, 该器件封装小、资源多, 具有强大、可灵活配置的逻辑编程资源, 含有数字信号处理资源(DSP)、36K 的双端口可配置 RAM、内建 FIFO、10 个时钟管理资源, 内含高精度模数转换单元(ADC), 支持 AES 和 SM4 的加密, 有 16 个 GTX 高速接口<sup>[12]</sup>, 可配置 IO 为 500 个, 可通过软硬件配合选择设置为多种不同的电平接口。本次设计主要通过 GTX 和低电压差分信号(Low-Voltage Differential Signaling, LVDS)进行扩展和传输, GTX 在系统中主要作用是接收均衡电路之后的视频信息然后通过内部 IP 核进行数据的解串, LVDS 接口主要是用于与 Hi3559 之间进行视频数据的

图 1 多路 HD-SDI 视频传输系统框图

传输和交互。

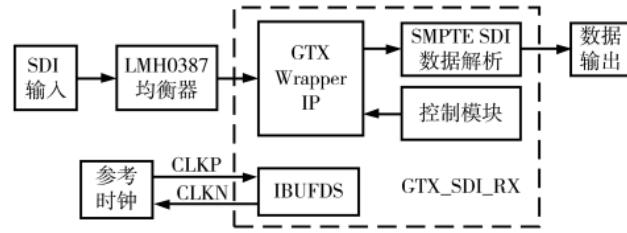

均衡电路<sup>[13]</sup>采用 TI 公司的 LMH0387 均衡芯片,该芯片输入输出方式可配置,通过软件配置既可以作为 SDI 视频输入时的均衡器,又可以作为 SDI 视频输出时的线缆驱动器。本次设计采用 LMH0387 主要是为了用作输入时接收摄像头的 HD-SDI 视频信号,然后发送给 FPGA 的 GTX 的 RX。该电路即实现了单端转差分和电平匹配,也增加了摄像头视频数据的接收距离。LMH0387 与 FPGA 之间的视频信息由高速接口进行接收或发送,数据参考时钟分开,采用交流耦合的方式对接,电平标准为 LVDS (低电压差分信号),本次均衡电路设计原理图如图 2 所示。

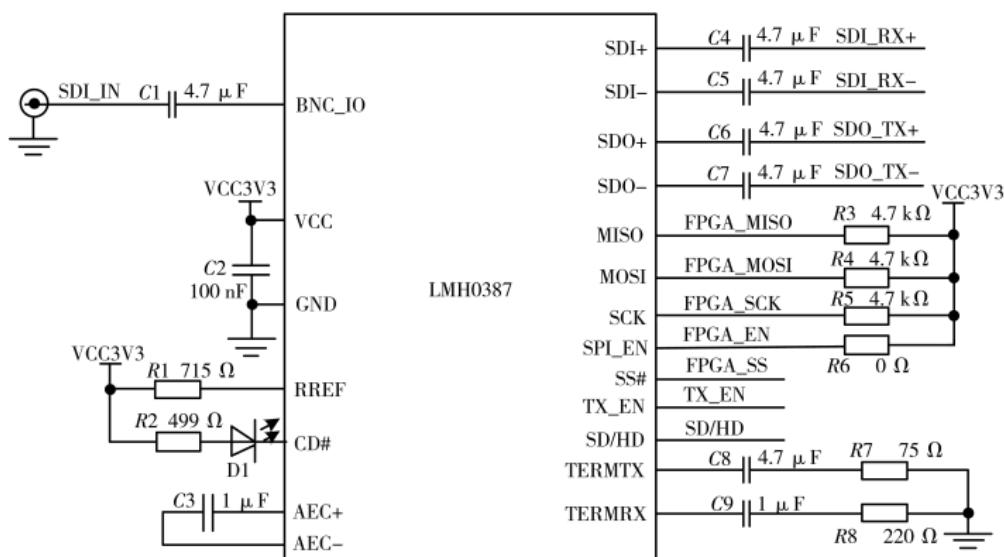

### 1.3 基于 GTX 的 SDI 接收模块

目前在 SDI 视频传输和处理时,主要有两种方式:(1)通过 SDI 视频解串芯片将高速非压缩视频<sup>[14]</sup>信号进行解串,转化为低速并行数字信号,然后发送给 FPGA 或者其他 SoC 系统进行接收和处理;(2)另外一种方式是通过 FPGA 硬件的资源和高速收发器进行解串,直接将不同速率的 SDI 视频信号通过同轴电缆传输,并且利用均衡芯片进行均衡和串并转化后对接到 GTX 的 RX 接收,该设计方法相比解串芯片方式从硬件成本和板卡集成度上具有更大的优势,软件一次开发,后期可以重复多次使用。因此,本次设计采用高速 GTX 接口实现串并转换,GTX 模块设计框图如图 3 所示。

控制模块的主要功能包括 GTX 收发器的主复位、GTX 内部的 PLL 复位、发送器复位、接收器复位以及 HD-SDI 速率识别检测(判断 HD-SDI 接收的数据速率是 1.485 Gb/s 或者为 1.485/1.001 Gb/s)。

根据 HD-SDI 的协议标准,SDI 数据采用 NRZ(归零码)编码格式<sup>[14]</sup>。因为 SDI 的视频数据中不包含时钟信息,因而 NRZ 数据码流中很容易出现连续的“0”或“1”

图 3 GTX SDI 接收模块框图

信息,连续的“0”或“1”会使得数据流信息含有的低频分量所占比例变大,电平跳变的数量减少,以至于时钟信息极少。为避免这种问题出现,HD-SDI 的信道编码方式根据 SMPTE 协议规定,采用了非归零码<sup>[14]</sup>,非归零码主要通过利用多项式对视频的数据流进行加扰处理,加扰之后:

$$G(x) = (x^9 + x^4 + 1)(x + 1) \quad (1)$$

加扰后的串行数据流中连续“0”或“1”就变得很少<sup>[15]</sup>,电平跳变信息变得多样,使得在接收端变得容易提取和获得时钟相关的信息,在调整图像采样后可输出 Y 分量和 C 分量。接着,就是对两个分量进行序列检测<sup>[16]</sup>,即提取分量中的定时基准码(TRS)。最后,利用提取的 TRS 判断视频格式、分辨率及帧频以及数据的稳定性。在稳定后,可从中提取有效的像素数据。这就是 SDI 信号传输的基本原理和解码流程。

### 1.4 视频传输接口设计

Hi3559 使用 MIPI Rx 接口(Mobile Industry Processor Interface Receiver)作为视频传输的数据通道,MIPI Rx 只完成接口的时序转换,不处理图像的数据格式。MIPI Rx 可以支持 MIPI D-PHY、LVDS、HiSPi 等串行视频信号输入,串行视频接口可以提供更高的传输带宽,增强传输的稳定性。为设计使用的广泛性,将 MIPI Rx 配置为 LVDS 功能作为 Hi3559 与 FPGA 之间的多路视频传输的

图 2 均衡电路设计原理图

数据通道。

本次设计采用 LVDS 电路, LVDS 只约束了电气传输规范, 没有时序和数据格式方面的标准协议, LVDS 电路由于相比主流的 MIPI 的 CSI<sup>[17]</sup>具有更大的优势, 它不需要 FPGA 提供额外的 IP 核和其他外围电路, 只需要进行直流或者交流耦合对接, 然后通过利用不同的同步码信息来区别像素的行场消隐区和有效的数据区域。在 LVDS 传输模式中, 行场同步码的信号是集成在视频的数据流信息中进行传输。

LVDS 模式下需要配置 RAW DATA 类型、数据大小端、同步方式、WDR 类型和图像宽高等寄存器。LVDS 模式依靠同步码识别帧的行同步信息, 根据 RAW DATA 类型的不同, 同步码可以分为 8/10/12/14/16 bit<sup>[5]</sup>, 10 bit 的 LVDS 同步码如表 1 所示。

表 1 10 bit 的 LVDS 同步码列表

| 同步位   | SAV 有效行 | EAV 有效行 | SAV 无效行 | EAV 无效行 |

|-------|---------|---------|---------|---------|

| 第 1 位 | 3FFh    | 3FFh    | 3FFh    | 3FFh    |

| 第 2 位 | 000h    | 000h    | 000h    | 000h    |

| 第 3 位 | 000h    | 000h    | 000h    | 000h    |

| 第 4 位 | XXXh    | XXXh    | XXXh    | XXXh    |

在同步码中, 第 4 位由摄像头的厂家决定, 本次设计由 FPGA 采集到 SDI 摄像头为 YUV4:2:2 SP 数据格式, 通过 FPGA 将像素信息按 RAW 数据格式重新排序将 YUV4:2:2 数据伪装成 RWA 数据送海思处理。

根据 SMPTE 292 的标准协议, 在传输 1 路标准的 HD-SDI 视频(1080P@25 Hz)总像素为:  $2640 \times 1125 \times 25 \times 20 \text{ bit} = 1.485 \text{ Gbit}$ , 因此不影响输出效果下, 为了减少数据量并且提高传输的效率, 设计在采用 LVDS 传输通道时, 每个像素由 8 bit 像素(彩色选择 16 bit)来表示, 此时每秒的总像素为:  $2640 \times 1125 \times 25 \times 8 \text{ bit} = 594 \text{ Mbit}$ , 因而采用 2Lane 的 LVDS 数据通道, 在采用 DDR 采样传输时, 参考时钟应该设计为 148.5 MHz, 每 Lane 的数据速率为 297 Mbit 即可实现 8 bit 的 LVDS 数据的传输。因此, 本次设计采用 2Lane 的 LVDS 方案可以满足 HD-SDI 系统传输带宽的需求。其他配置模式下, LVDS 的时钟和数据传输设计已经过验证均可实现, 如表 2 所示。

表 2 时钟和数据传输方式配置

| 比特位/bit | 总数据量       | 时钟设计/MHz | LVDS 模式 | 单 Lane 速率(DDR)/(Mb/s) |

|---------|------------|----------|---------|-----------------------|

| 8       | 594 Mbit   | 148.5    | 2Lane   | 297                   |

| 16      | 1.188 Gbit | 297      | 2Lane   | 594                   |

| 8       | 594 Mbit   | 74.25    | 4Lane   | 148.5                 |

| 16      | 1.188 Gbit | 148.5    | 4Lane   | 297                   |

## 2 系统测试与验证

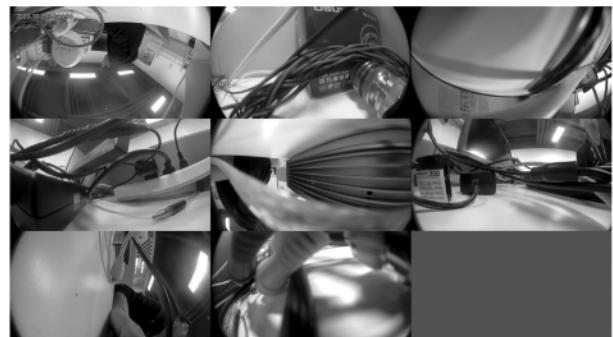

多路 HD-SDI 视频传输系统, 利用 8 路 HD-SDI 摄

像头作为视频源的输入, 将视频采集程序烧录 FPGA 内, 通过逻辑分析和仿真软件可以判断视频信号是否锁定和成功接收。GTX 获得视频信息后进行解析和处理, 然后再利用 FPGA 增入相应的同步码信息进行打包处理, 通过 LVDS 接口将视频数据发送给 CPU, 通过串口调试输入视频同步的命令可以检测 8 路视频的同步和格式, CPU 经过接收和处理后将多路视频采用九宫格的方式输出至 HDMI 接口, 使用显示屏进行显示。

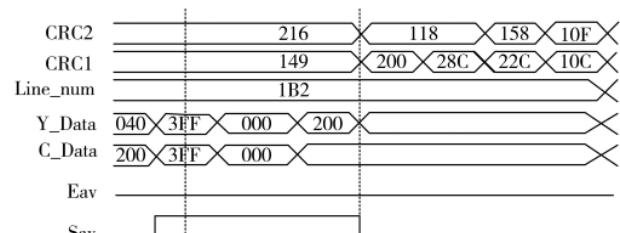

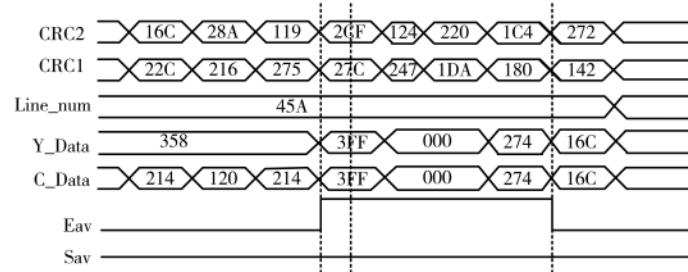

HD-SDI 摄像头按照标准的 SDI 数据格式发送出相应的数据信息, FPGA 接收通过同步码信息识别有效信息的行起始和行结束, 10 bit 同步码的行起始的时序波形如图 4 所示, 行结束时序波形如图 5 所示。

图 4 行起始(SAV=1)时序

图 5 行结束(EAV=1)时序

FPGA 通过 GTX 成功识别和接收 SDI 数据信息后, 解析获取有效的 HD-SDI 视频信息。将 8 路 1080P@25 Hz 的 HD-SDI 摄像头作为输入, 利用本次开发的 Hi3559 的多路 HD-SDI 视频传输系统平台, 验证将 8 路 HD-SDI 视频信号进行同时采集、接收、传输、处理后将接收到的视频图像通过 HDMI 显示器进行图像显示。通过该视频采集系统处理后, 正常 8 路 HD-SDI 视频图像处理后显示结果如图 6 所示。

图 6 8 路 HD-SDI 视频图像处理后显示结果

### 3 结论

本次研究通过采用 Hi3559+FPGA 架构,设计完成了多路 HD-SDI 高清视频传输系统的开发和验证,该系统能够在 Hi3559 上实现 8 路 HD-SDI 视频图像的采集、传输、处理以及全景显示。经过开发和测试验证,该系统能够满足 HD-SDI 视频传输的协议标准和速率要求,能够支持长距离的传输,工作稳定可靠。对于想要利用 Hi3559 实现多路高清视频的采集、远距离传输以及智能算法等方向具有较高的推广和参考应用价值。

### 参考文献

- [1] 唐伟.面向嵌入式图像处理系统的 SOPC 芯片通信接口设计与实现[D].南京:东南大学,2018:51-52.

- [2] 刘旭阳.2013 年电影电视工程学会(SMPTE)电影技术标准发展综述[J].现代电影技术,2014(2):40-43.

- [3] 姜忠兵.基于 SMPTE274M 标准的高清视频发生器设计与实现[J].电子设计工程,2012,20(17):150-152.

- [4] 钱宏文,王毅,刘会.一种基于 FPGA 的多路 HD-SDI 测试系统[J].电子技术应用,2020,46(8):121-125.

- [5] 张泽孜,谭大伦,王冬海.Hi3559A 在视频结构化平台中的应用[J].无线互联科技,2019(12):143-144.

- [6] 薛一哲,吴云,王昭.基于 DSP 串行通信接口开发的研究[J].航空计算技术,2018,18(1):95-97.

- [7] 白金成.基于 FPGA 的多路 Cameralink 数字图像光纤传输系统[J].液晶与显示,2019,34(8):787-792.

- [8] 彭勃,何宾.FPGA 在视频拼接中的应用与实现[J].计算机工程与设计,2013,34(5):1635-1639.

- [9] 付强,杨文豪,倪文龙.基于 FPGA 的 HD-SDI 转 HDMI 接

(上接第 82 页)

- [9] KIRSCH A, MITZENMACHER M. Distance-sensitive bloom filters[C]//2006 Proceedings of the Eighth Workshop on Algorithm Engineering and Experiments(ALENEX).Society for Industrial and Applied Mathematics, 2006: 41-50.

- [10] XYLOMENOS G, VERVERIDIS C N, SIRIS V A, et al. A survey of information-centric networking research[J]. IEEE Communications Surveys & Tutorials, 2013, 16(2): 1024-1049.

- [11] AMADEO M, CAMPOLO C, QUEVEDO J, et al. Information-centric networking for the Internet of Things: challenges and opportunities[J]. IEEE Network, 2016, 30(2): 92-100.

- [12] FANG C, YAO H, WANG Z, et al. A survey of mobile information-centric networking: research issues and challenges[J]. IEEE Communications Surveys & Tutorials, 2018, 20(3): 2353-2371.

- [13] HUA Y, XIAO B, VEERAVALLI B, et al. Locality-sensitive Bloom filter for approximate membership query[J]. IEEE Transactions on Computers, 2011, 61(6): 817-830.

- [14] HUA Y, LIU X. Locality-sensitive Bloom filter for approximate

口设计与实现[J].电子与封装,2018,18(2):37-39.

- [10] 杨晓萍,胡玉,张凯.基于 FPGA 的视频拼接技术研究[J].吉林大学学报,2016,34(6):709-715.

- [11] 吴俊霖.基于 FPGA 的 HD-SDI 信号传输与处理[D].成都:西南交通大学,2011:11-14.

- [12] 张永昊,宋华军,吴玉兴.基于 FPGA+DSP 的 SDI 高清图像处理系统[J].国外电子测量技术,2019,38(09):28-32.

- [13] 孙偲晟.FPGA 的 SD/HD/3G-SDI 的图像环路测试装置设计[J].单片机与嵌入式系统应用,2019(11):69-73.

- [14] 徐大鹏,孙海江.HD-SDI 视频嵌入式图像采集设计[J].计算机测量与控制,2015,23(9):3214.

- [15] 邹亦婷.基于多处理器协同的智能工业相机图像处理系统的设计与实现[D].成都:电子科技大学,2019:8-9.

- [16] 李艳婷,王水鱼.视频图像中动态目标检测系统的 FPGA 硬件设计[J].计算机系统应用,2017,26(3):119-125.

- [17] 马森.嵌入式图像处理平台设计及实现[D].成都:电子科技大学,2018:12-13.

(收稿日期:2021-03-01)

### 作者简介:

王毅(1991-),男,硕士,工程师,主要研究方向:视频图像处理和 FPGA 应用。

张禹(1993-),男,本科,工程师,主要研究方向:DSP 和 FPGA 应用等方面的数据硬件开发。

钱宏文(1975-),男,本科,研究员级高级工程师,主要研究方向:集成电路应用和微系统领域设计。

扫码下载电子文档

membership query[M]//Searchable Storage in Cloud Computing. Springer, Singapore, 2019: 99-127.

- [15] DATAR M, IMMORLICA N, INDYK P, et al. Locality-sensitive hashing scheme based on p-stable distributions[C]// Proceedings of the Twentieth Annual Symposium on Computational Geometry, 2004: 253-262.

- [16] WOLD S, ESBENSEN K, GELADI P. Principal component analysis[J]. Chemometrics and Intelligent Laboratory Systems, 1987, 2(1-3): 37-52.

- [17] BLAKE C, KEOGH E, MERZ C. UCI repository of machine learning databases[Z]. 1999.

(收稿日期:2021-12-13)

### 作者简介:

吴佳雯(1996-),女,硕士研究生,主要研究方向:布鲁姆查询、近似查询。

王宇科(1978-),通信作者,男,硕士研究生,高级工程师,主要研究方向:网络安全、网络测量与分析、数据挖掘,E-mail:wyk@hnu.edu.cn。

裴书玉(1993-),女,硕士研究生,主要研究方向:布鲁姆查询、概率型数据结构。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所