# 基于虚拟仪器的 DRFM 干扰模拟器设计

汪 敏<sup>1,2</sup>,蒋彦雯<sup>1</sup>,范红旗<sup>1</sup>

(1.国防科技大学 自动目标识别重点实验室,湖南 长沙 410000;2.中国人民解放军 94535 部队,江苏 徐州 221000)

**摘要:**为满足雷达对抗数字射频存储(DRFM)干扰的技术验证和系统测试需求,采用矢量信号收发仪结合 DRFM 技术设计了一种模块化、可扩展、轻量便携的干扰模拟器,采用一种流控制器实现对干扰模拟器的控制,并通过雷达和干扰模拟器的注入测试验证了设计的有效性。该设计能根据雷达回波产生包括间歇采样转发干扰在内的多种类型雷达干扰信号,能通过更换、扩展板卡实现多种任务功能,可用于雷达测试环境构建,有力支撑了雷达抗干扰技术的研究与验证。

**关键词:**干扰模拟;数字储频;虚拟仪器;间歇采样;FPGA

中图分类号: TN955+.3

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211901

中文引用格式: 汪敏,蒋彦雯,范红旗. 基于虚拟仪器的 DRFM 干扰模拟器设计[J]. 电子技术应用, 2022, 48(3): 118–122, 128.

英文引用格式: Wang Min, Jiang Yanwen, Fan Hongqi. Design of DRFM jamming simulator using virtual instrument[J]. Application of Electronic Technique, 2022, 48(3): 118–122, 128.

## Design of DRFM jamming simulator using virtual instrument

Wang Min<sup>1,2</sup>, Jiang Yanwen<sup>1</sup>, Fan Hongqi<sup>1</sup>

(1.National Key Laboratory of Science and Technology on Automatic Target Recognition,

National University of Defense Technology, Changsha 410000, China;

2. Unit 94535 of PLA, Xuzhou 221000, China)

**Abstract:** In order to meet the technical verification and system testing requirements of radar countermeasures against digital radio frequency memory(DRFM) jamming, a modular, scalable, lightweight and portable vector signal transceiver combined with DRFM technology is designed. The simulator control part adopts a kind of flow controller to realize, and the effectiveness of the design is verified by the injection test of the radar and jamming simulator. This design can generate various types of radar jamming signals, including interrupted-sampling and repeater jamming according to the radar echo. It can realize multiple mission functions by replacing and expanding the board. It can be used in the construction of radar test environment to support the research and verification of radar anti-jamming technology.

**Key words:** jamming simulation; DRFM; virtual instrument; interrupted-sampling; FPGA

## 0 引言

作为现代电子对抗中的核心技术,数字射频存储(Digital Radio Frequency Memory, DRFM)干扰技术以其调制方式的灵活性、信号相干性等特点,广泛应用于各类自卫式、支援式和投掷式干扰系统中<sup>[1]</sup>。对抗 DRFM 干扰、尤其是来自雷达主瓣的 DRFM 干扰<sup>[2]</sup>,成为了当前各类雷达研制测试中的一项重要课题,因此研制一种能满足技术验证与系统测试需求的 DRFM 干扰模拟器就显得尤为必要。

目前已有的 DRFM 干扰模拟器大多采用定制硬件进行设计,并且产生的干扰样式较为单一、固定。其中文献[3]针对雷达抗拖曳式诱饵干扰设计了一种目标和拖曳诱饵的模拟器,其系统硬件部分采用专用定制设备,用途较为局限;文献[4]设计了一种宽带雷达目标与干

扰模拟器,能够覆盖 L-Ku 波段雷达,但系统各单元均为定制组件,功能扩展性不够;文献[5]针对雷达测试设计了一种多通道回波模拟器,能够产生噪声、假目标等干扰,但每个通道仅能固定产生一种干扰;文献[6]采用通用仪器设计了一款 DRFM 雷达回波模拟器,可以产生多种欺骗干扰,但变更干扰样式需要重启系统,使用上不够灵活。综上所述,有必要研制一种配置更加灵活、通用性更强且易使用的 DRFM 干扰模拟器。

本文基于 NI 公司的 PXI 自动化测试平台,以矢量信号收发仪(Vector Signal Transceivers, VST)为核心<sup>[7]</sup>,采用 DRFM 技术体制进行干扰模拟器设计,设计了一种流控制器实现对干扰模拟器的控制。干扰模拟器可以实现包括全脉冲存储转发、式样脉冲存储转发和间歇采样存储转发在内的三种存储方式<sup>[8]</sup>,通过结合移频、调相等

调制方式,可以实现首尾连续转发干扰、间歇采样移频转发干扰等多种复杂的干扰样式<sup>[9]</sup>。通过更换 VST 板卡,可快速调整干扰模拟器的频段、带宽等指标参数。通过扩展 VST 板卡的数量,可构建更加复杂的电磁信号环境。

## 1 硬件组成

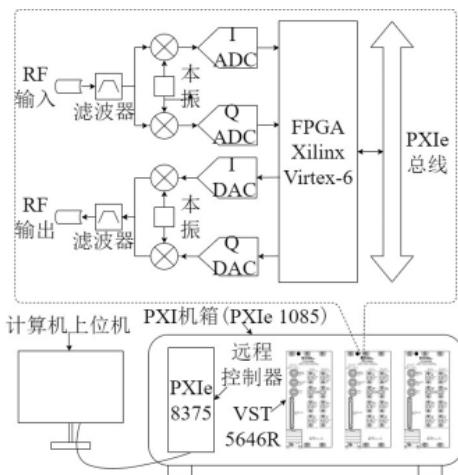

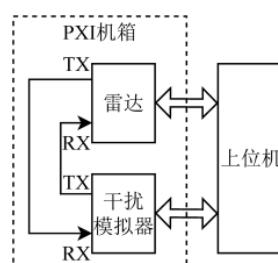

该干扰模拟器系统采用全商用现货(COTS)的 PXI 自动化测试平台搭建,包括 PXI 机箱、远程控制器和 VST 板卡。远程控制器和 VST 模块位于 PXI 机箱内,远程控制器通过光纤连接到计算机上位机,其中 PXI 机箱和 VST 板卡可以根据需求选择不同的型号,不同的 VST 板卡覆盖的频段范围不同,因此干扰模拟器系统不包含收发天线,收发天线需根据具体应用场景单独进行选择。干扰模拟器系统组成如图 1 所示,下面对各部分进行详细说明。

图 1 干扰模拟器系统组成图

VST 是干扰模拟器的核心组件,集成了通用的接收和发射前端以及可用作实时信号处理的 FPGA。通过 VST 完成对雷达信号的接收、存储、调制和转发,其中存储、调制和控制等复杂功能在 FPGA 上实现。VST 根据上位机传递的参数生成不同类型的干扰信号,通过多块 VST 板卡同时工作可产生多路不同类型、不同参数的干扰信号,构建出测试所需的复杂电磁信号环境。当测试需求发生变化时,干扰模拟器可通过更换 VST 板卡快速调整自身指标性能,而不需要改动软件部分,例如频率范围可由 65 MHz~6 GHz 将上限扩展至 40 GHz;瞬时带宽可由 80 MHz 扩展至 1.4 GHz<sup>[7]</sup>。

PXI 机箱为干扰模拟器系统提供电源、散热、通信总线,同时将整个系统集成为一个整体,实现轻量便携。干扰模拟器采用远程控制的方式,通过光纤将上位机和 PXI 机箱进行分离,在保证功能不受影响的同时可以让用户远离辐射源,提升实验的灵活性。干扰模拟器上位机采用 Intel 处理器,运行上位机控制软件。

## 2 软件设计

该干扰模拟器系统硬件部分均采用通用模块,因此

其核心功能依赖软件进行设计,主要包括 FPGA 软件和控制软件。其中,FPGA 软件是干扰模拟器信号检测和干扰生成的核心,运行于 VST 的板载 FPGA 内;控制软件是干扰模拟器的监控终端,为无人机交互提供操控接口和显示界面,运行于上位机内,两者通过 PXIe 总线进行通信。

### 2.1 功能模块设计

干扰模拟器在技术体制上选择 DRFM 架构。DRFM 的原理是通过接收并存储雷达信号,在时域和频域内对存储的雷达信号进行调制,生成相干干扰信号<sup>[1]</sup>。作为一种测试设备而非实际干扰机,DRFM 干扰模拟器带宽大于雷达信号瞬时带宽即可,但为了适应不同的雷达波形体制、灵活产生各种典型样式的 DRFM 干扰,要求干扰模拟器具备存储深度深和实时响应的特点。

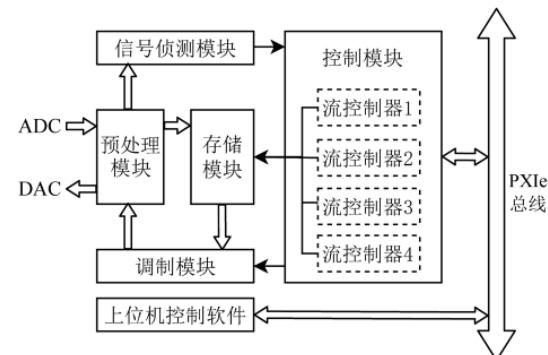

基于上述需求,在 FPGA 中主要实现了五个功能模块,分别为预处理模块、信号侦测模块、控制模块、存储模块和调制模块,由上位机控制软件提供状态参数输入,AD/DA 完成和射频前端的数据交互。干扰模拟器工作原理如图 2 所示。来自 ADC 的输入信号经过预处理模块处理后送给信号侦测模块,完成信号参数测量,控制模块根据来自信号侦测模块的信息和上位机软件的参数对存储模块和调制模块进行控制,调制完的信号再次经过预处理后经由 DAC 送给发射前端。

图 2 干扰模拟器工作原理图

#### (1) 预处理模块

预处理模块实现 I/Q 补偿、分数内插和分数抽取三种功能。I/Q 两路信号在调制或解调时会出现幅相不平衡,通过 I/Q 补偿功能进行解决。另外由于干扰模拟器的存储深度受自身采样频率的影响,为了在雷达信号带宽较小时节省资源,需要降低干扰模拟器采样处理频率,但是 VST 中 ADC/DAC 的采样频率为固定值,比如型号为 PXIe 5646R 的 VST 为 200 MHz,因此在 FPGA 设计中引入分数抽取和分数内插功能来降低有效数据的速率。

#### (2) 信号侦测模块

信号侦测模块实现对雷达信号的侦测与参数测量。通过正交检波方法对输入的复数基带信号进行功率计算<sup>[10]</sup>,输出信号起止时刻,并据此计算信号的脉宽参数

传递到控制模块。为了降低噪声对包络检测的干扰,可以根据信噪比设置合适的门限阈值。

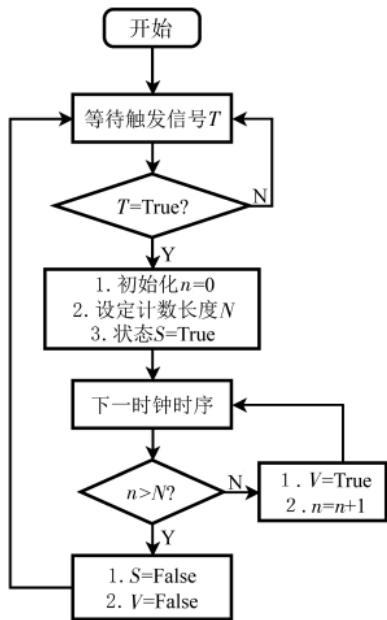

#### (3) 控制模块

控制模块是干扰模拟器功能实现的关键,通过四个结构相同的流控制器完成对信号的存储和收发控制。流控制器包括两个输入信号,分别为计数长度  $N$  和触发信号  $T$ ;以及三个输出信号,分别为信号有效  $V$ 、当前计数值  $n$  和当前状态  $S$ 。流控制器的控制流程如图 3 所示。

图 3 流控制器控制流程图

流控制器在接收到触发信号  $T$  后,根据设定的计数长度  $N$  进行计数,并精确返回当前计数值  $n$  的大小、输出信号  $V$  是否有效以及当前流控制器的状态  $S$ 。照此逻辑顺序通过四个流控制器的紧密配合完成对干扰模拟器存储和转发的控制,具体控制流程在 2.2 节进行介绍。

#### (4) 存储模块

存储模块根据控制模块的命令对预处理模块传入的信号进行选择、存储和转发。存储模块选用块 RAM 进行信号存储,相比查找表,选用块 RAM 的优势是不占用 FPGA 逻辑资源,而相比更大容量的 DRAM,块 RAM 的存取速度更快,仅消耗一个时钟周期。以 VST 5646R 为例,除去其他功能占用后,可供存储模块使用的块 RAM 数量为 300 KB,按最大 200 MHz 的带宽计算,可以存储的信号长度为 1.5 ms,能够满足干扰模拟器的需求。

#### (5) 调制模块

调制模块通过数控振荡器(NCO)对转发信号的频偏和相位进行调制,

产生更加多样灵活的干扰信号<sup>[11]</sup>。在 FPGA 硬件实现中,为了模拟运动的假目标信号,通过将待转发的复数基带信号与数控振荡器(NCO)生成的复频率信号进行复数相乘实现对信号的调制。

#### (6) 上位机控制软件

控制软件采用 LabVIEW 图形化编程语言编写,能够实时与 VST 中的 FPGA 进行通信,监测并显示 PXI 机箱以及各板卡的工作状态信息,方便用户对整个系统的控制与监测。控制软件界面如图 4 所示,界面分为三个功能栏,VST 配置栏中完成对 VST 板卡基本参数的配置;干扰样式选择栏中完成不同的干扰样式和参数的设置;状态监控栏能够在干扰模拟器工作时监控其工作状态。当 PXI 机箱启动后,完成 VST 配置栏和干扰样式选择栏的设置,然后点击启动,即可启动模拟器。

图 4 干扰模拟器控制软件界面

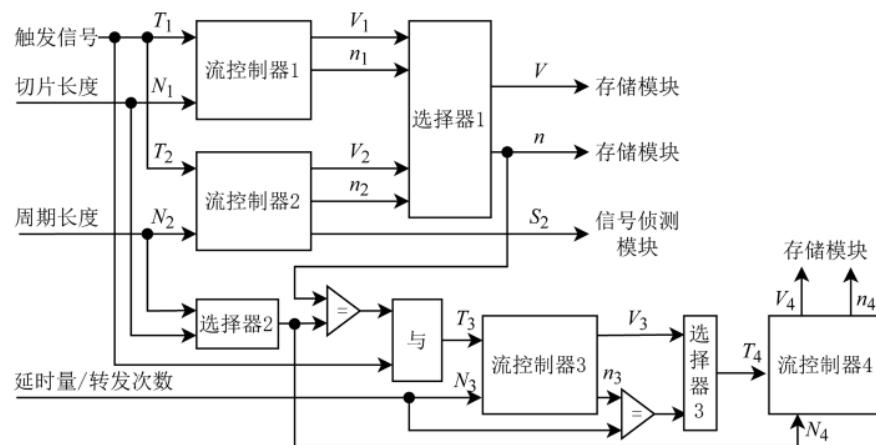

## 2.2 控制流程

对干扰模拟器存储、转发的控制由控制模块中的四个流控制器相互配合完成,下面对照图 5 中的流程图对干扰模拟器产生转发干扰流程进行详细说明。

根据转发脉冲的完整性,转发干扰分为全脉冲转发干扰、式样脉冲转发干扰和间歇采样转发干扰。全脉冲转发包含完整的雷达脉冲信号;式样脉冲转发则只截取

图 5 干扰模拟器控制流程图

部分雷达脉冲信号进行转发,降低了对存储模块深度的要求;间歇采样转发采用交替采样、转发的方式,针对大时宽信号有较好效果<sup>[12]</sup>。

全脉冲转发时,根据信号侦测模块得到的信号脉宽计算图中的周期长度输入,根据信号起始时刻生成触发信号,此时选择器1的输出为流控制器2的输出,存储模块根据计数值n作为地址对信号进行存储,选择器2输入选择周期长度,选择器3选择n<sub>3</sub>的比较值。全脉冲转发和式样脉冲转发时,流控制器3的输入均为延时量,控制存储和转发之间的时间间隔。流控制器4计算读取地址送给存储模块进行信号读取、转发。

式样脉冲转发与全脉冲转发过程基本相同,不同之处在于此时周期长度参数应小于信号脉宽,差值由上位机进行设定。

间歇采样转发时,周期长度为侦测得到的信号脉宽,切片长度由上位机设定的占空比参数确定。此时选择器1的输出为流控制器1的输出,选择器2输入选择切片长度,选择器3选择V<sub>3</sub>,流控制器3的输入为转发次数。在接收到触发信号后,存储器根据切片长度存入信号,然后流控制器4根据流控制器3确定的转发次数重复生成地址送给存储模块读取信号转发,转发完成后流控制器2将状态信息返回信号侦测模块,若此时侦测信号还未结束,继续产生触发信号,重复上一过程,直至信号结束。

间歇采样转发模式下,通过结合调制模块的移频功能可以产生间歇采样移频重复转发干扰。

### 3 系统测试

应用干扰模拟器对单通道雷达进行干扰实验,对系统的功能及部分主要指标进行可行性验证测试,包括产生不同样式干扰的能力,以及动态范围和转发延时等指标。

#### 3.1 验证测试方案

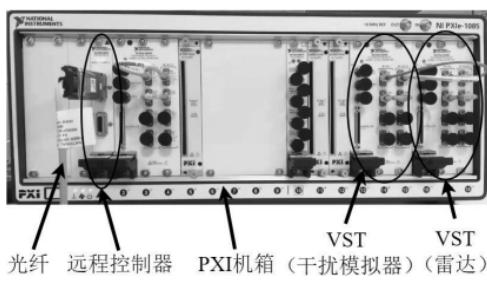

验证测试方案采用第二块VST模拟雷达系统,采用射频注入方式测试DRFM干扰模拟器,设备连接如图6所示,图7为干扰模拟器系统的实物图。

图6 验证方案框图

图7 干扰模拟器实物图

图6中,将雷达系统的发射端与干扰模拟器的接收端直连,接收端与干扰模拟器的发射端直连,形成闭环回路。雷达系统可以实现脉冲波形的发射与回波信号处理,并将结果返回到上位机显示。

验证方案中雷达发射信号的参数如表1所示。

表1 雷达信号参数

| 参数名称      | 参数值   |

|-----------|-------|

| 雷达信号类型    | LFM信号 |

| 脉冲宽度/μs   | 2     |

| 调频带宽/MHz  | 50    |

| 雷达采样率/MHz | 200   |

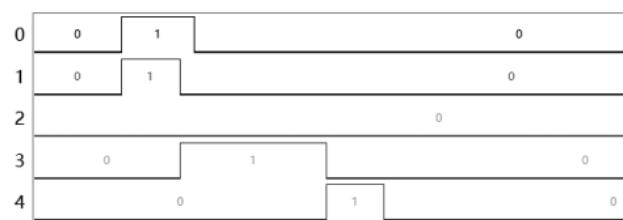

通过在FPGA中脉冲检测模块包络输出处以及四个流控制器的输出处分别放置探针寄存器,从而能够在上位机获得系统运行时的时序图,5个寄存器的名称按顺序分别为0~4。

下面以式样脉冲转发干扰、首尾连续转发干扰和间歇采样移频重复转发干扰三种干扰样式为例来进行干扰模拟器动态范围、转发延迟和干扰种类的验证。

#### 3.2 动态范围

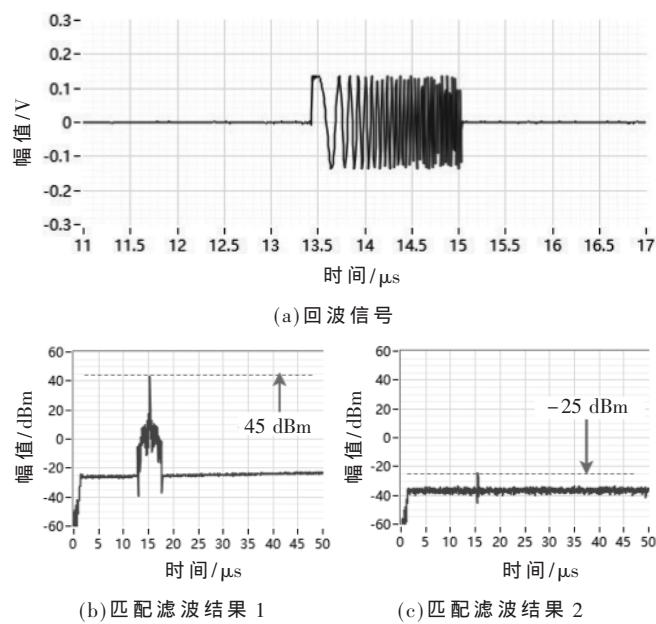

动态范围指干扰模拟器在不产生虚假响应时系统可接收的最大、最小信号功率比。试验采用式样脉冲转发干扰模式,选择的转发长度为雷达脉冲长度的80%,图8为其时序图。

图8 式样脉冲转发干扰时序图

从图8中可以看出,流控制器1只存入了接收信号的部分长度。当雷达脉冲信号较长无法全部存储时,流控制器1控制存储模块只存入雷达脉冲信号的前半部分,可在资源受限的情况下达到需要的干扰效果。

图9(a)为雷达接收端接收到的回波信号图,可以看出接收到回波仅为部分发射脉冲。图9(b)和图9(c)为接收到回波进行匹配滤波之后的结果,分别对应干扰模拟器的最大接收功率和最小接收功率,根据图中的结果,干扰模拟器的动态范围能够满足雷达验证测试的需求。

#### 3.3 转发延迟

干扰模拟器转发延迟指干扰模拟器从接收到雷达脉冲信号到开始转发所需要的最小延迟时间,在DRFM系统中主要取决于数据的存取延迟。

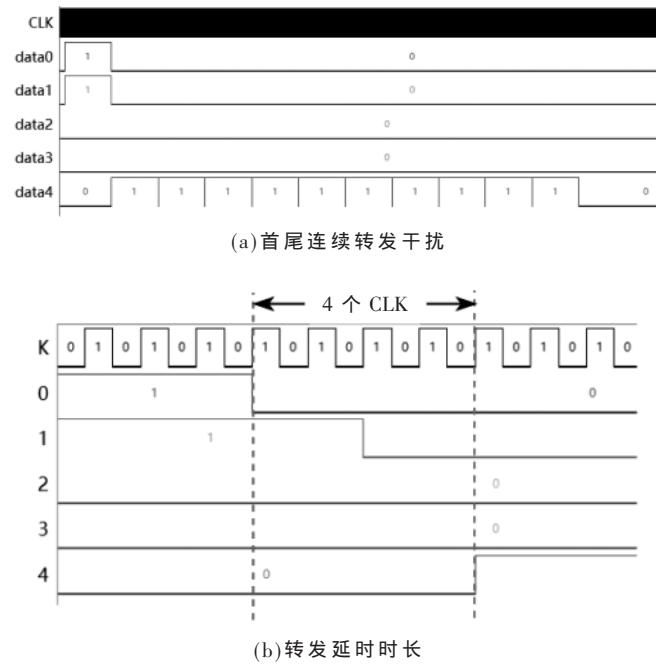

图10为首尾连续转发干扰的寄存器时序图。其中图10(a)为一次转发过程的时序图,图10(b)为存入数据

图 9 式样脉冲转发干扰接收回波

图 10 首尾连续转发干扰时序图

到取出的延迟时长。

从图 10 中可以看出, 流控制器 1 在脉冲检测触发信号 0 产生后被激活开始存入数据, 并且有两个周期的延迟, 触发信号消失后翻转为等待状态, 停止存入数据。存入完毕后直接启动流控制器 4, 开始循环读取数据送往调制模块, 读取时延迟为两个周期, 本文设计的干扰模拟器的最大采样率为 200 MHz, 所以转发延时为 20 ns, 若采用 PXIe-5840 板卡, 干扰模拟器的最大采样率可达到 1 GHz, 转发延迟可以减小到 4 ns, 因此可以通过更换板卡来灵活调整干扰模拟器的系统性能。

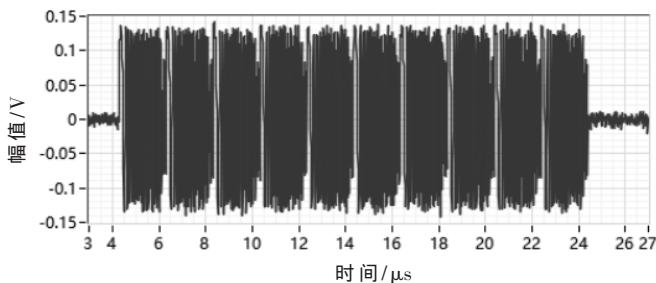

图 11 为雷达接收端接收到的回波信号图, 从图中可以看出, 干扰模拟器在接收到雷达发射信号后成功产生了首尾连续的多个脉冲回波。

图 11 首尾连续转发干扰接收回波

### 3.4 干扰产生验证

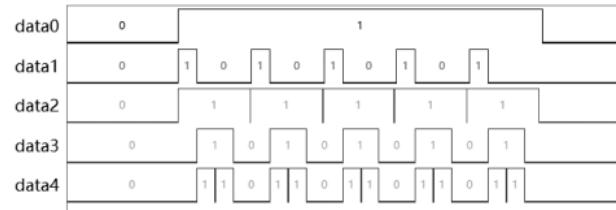

在上面两个试验中已经产生了式样脉冲转发干扰和首尾连续转发干扰, 下面进行间歇采样移频重复转发干扰的验证。图 12 为间歇采样移频重复转发干扰寄存器的时序图, 从图中可以看出, 当脉冲检测触发信号 0 激活后, 流控制器 2 激活, 并根据设定的周期、占空比计算出存入宽度, 然后激活流控制器 1, 在一个周期内, 存入完毕后激活流控制器 3, 间歇采样转发模式下, 流控制器 3 控制的是重复转发次数, 当长度设置为 1 时即为间歇采样直接转发, 大于 1 时即为间歇采样重复转发干扰。

图 12 间歇采样移频重复转发干扰时序图

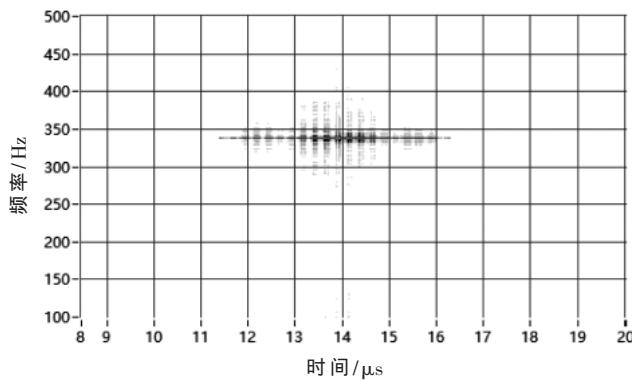

图 13 为雷达接收回波的 RD 图, 从图中可以看出, 干扰模拟器采用间歇采样的方式并结合频移, 成功产生了更加密集的假目标干扰。

图 13 接收回波 RD 谱

(下转第 128 页)

- 方法[J].西安电子科技大学学报(自然科学版),2012,39(4):184-190.

- [4]姬长华,张秀丽.二相编码雷达信号及常见问题处理[J].现代电子技术,2008(5):8-10.

- [5]张恒达,冯西安.二相编码信号性能分析[J].电子设计工程,2014,22(12):138-140.

- [6]孙雪竹.LPI雷达分析及信号处理的DSP实现[D].西安:西安电子科技大学,2011.

- [7]CHENG Y P, BAO Z. Doppler compensation for binary phase-coded waveforms[J]. IEEE Transactions on Aerospace and Electronic Systems, 2002, 38(3): 1068-1072.

- [8]王杰,梁兴东,丁赤飚,等. OFDM SAR 多普勒补偿方法研究[J].电子与信息学报,2013,35(12):3037-3040.

- [9]王毅鹰,苏兮.基于 m 序列信号的多普勒补偿方法[J].现代雷达,2007,29(2):48-51.

- [10]田孝斌.二相编码信号的多普勒特性及其补偿算法研究[J].电子科技,2013,26(9):31-33.

- [11]周鹏,徐若曦,章锦文.几种序列编码在雷达系统中的

应用分析[J].信息通信,2014,139(7):21.

- [12]尹灿斌,贾鑫.复合调频-调相合成孔径雷达信号性能分析[J].电子学报,2012,40(6):405-409.

- [13]林智梅.基于相位编码信号的 SAR 目标成像及抗干扰性能分析[D].秦皇岛:燕山大学,2016.

- [14]郭磊,王宇,邓云凯.基于方位向相位编码技术的方位向多通道 SAR 距离模糊抑制方法[J].电子与信息学报,2015,37(3):601-606.

- [15]刘永坦.雷达成像技术[M].哈尔滨:哈尔滨工业大学出版社,1999.

(收稿日期:2021-04-01)

#### 作者简介:

蔡永俊(1989-),男,博士研究生,工程师,主要研究方向:合成孔径雷达成像与系统。

牛诚翔(1983-),男,硕士研究生,高级工程师,主要研究方向:合成孔径雷达成像与系统。

扫码下载电子文档

(上接第 122 页)

## 4 结论

通过对整个系统进行验证,本文设计的干扰模拟器能够实现对雷达脉冲信号的实时重构转发,性能指标能够满足测试验证的需求,并且模拟器可以根据 FPGA 中设计好的逻辑配合上位机的控制灵活产生多种不同类型的干扰样式,模块化的板卡为干扰模拟器提供了较好的可扩展性,能够适应多种雷达抗干扰性能测试的需求,可为研究人员在雷达波形设计和信号处理算法研制时提供验证测试方案参考。

## 参考文献

- [1]冉宏远,张宏伟,张民国.数字射频存储器发展现状及趋势[J].飞航导弹,2018(6):44-48.

- [2]高霞,全英汇,李亚超,等.基于 BSS 的 FDA-MIMO 雷达主瓣欺骗式干扰抑制方法[J].系统工程与电子技术,2020,42(9):1927-1934.

- [3]张兴利,梁艳青,王建.雷达型导弹抗拖曳式诱饵干扰半实物仿真试验技术[J].航空兵器,2015(6):55-57.

- [4]于卫刚,吴昌松,张德欣,等.一种多功能宽带雷达目标与干扰模拟器设计[J].现代防御技术,2020,48(5):105-112.

- [5]刘亭洲,王海锋,李乐怡.一种雷达回波模拟器的研究与

设计[J].航空兵器,2018(3):73-77.

- [6]张鹏.基于通用仪器的 DRFM 雷达目标模拟器实现[J].现代雷达,2015,37(8):81-85.

- [7]NI 针对高吞吐量应用推出全新的 PXI 远程控制和总线扩展模块[J].电子测量与仪器学报,2017,31(9):1506.

- [8]吴永刚.基于 DRFM 的有源雷达干扰技术研究[D].长春:吉林大学,2013.

- [9]刘巧玲,李文臣,张文明,等.间歇采样移频转发干扰效果仿真分析[J].电子信息对抗技术,2009,24(1):48-50.

- [10]张成发.宽带远距离雷达回波模拟器实现[D].成都:电子科技大学,2018.

- [11]李宝鹏,彭志刚,王艳军,等.基于 VST-FPGA 的雷达侦察与干扰系统设计[J].电子测量与仪器学报,2020,34(11):181-187.

- [12]王雪松,刘建成,张文明,等.间歇采样转发干扰的数学原理[J].中国科学 E 编:信息科学,2006(8):891-901.

(收稿日期:2021-06-28)

#### 作者简介:

汪敏(1993-),男,硕士研究生,主要研究方向:雷达波形对抗。

范红旗(1978-),通信作者,男,博士,主要研究方向:主动感知系统、目标跟踪、信息融合与智能导引等,E-mail:fanhongqi@nudt.edu.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所