# HART 调制解调芯片高速通信接口设计 \*

张立国<sup>1</sup>,李福昆<sup>1</sup>,严伟<sup>2</sup>,刘强<sup>1</sup>,王雪迪<sup>1</sup>

(1.燕山大学 电气工程学院,河北 秦皇岛 066000;2.北京大学 软件与微电子学院,北京 100871)

**摘要:**针对当下工厂设备间设备量以及传输数据量庞大问题,设计了一种新型的HART调制解调芯片接口,通过AXI4总线接口代替传统的UART接口,加速HART调制解调芯片与CPU之间的通信速度。相比于URAT传统接口按位传输,AXI4总线接口可并行传输32位8个字节,数据传输速度可达到纳秒级别。通过AXI4总线模块与CPU的互联,实现结构功能配置与数据的交互。HART调制解调芯片高速通信接口设计基于FPGA平台进行原型验证,结果表明,该架构能有效识别HART通信协议,CPU与HART芯片数据交互达到纳秒级别,调制解调正确率高达100%,满足HART通信协议要求。

**关键词:**通信芯片架构;芯片互联;HART通信协议;通信接口

中图分类号: TN913.3

文献标识码: A

DOI:10.16157/j.issn.0258-7998.211551

中文引用格式:张立国,李福昆,严伟,等. HART调制解调芯片高速通信接口设计[J].电子技术应用,2022,48(4):6-11.

英文引用格式:Zhang Liguo,Li Fukun,Yan Wei,et al. Interface design of HART modulation and demodulation chip[J]. Application of Electronic Technique,2022,48(4):6-11.

## Interface design of HART modulation and demodulation chip

Zhang Liguo<sup>1</sup>, Li Fukun<sup>1</sup>, Yan Wei<sup>2</sup>, Liu Qiang<sup>1</sup>, Wang Xuedi<sup>2</sup>

(1.School of Electrical Engineering, Yanshan University, Qinhuangdao 066000, China;

2.School of Software and Microelectronics, Peking University, Beijing 100871, China)

**Abstract:** In order to adapt to the current factory equipment, aiming at the huge amount of equipment and data transmission, this paper designs a new HART modulation and demodulation core interface, which uses AXI4 bus interface to replace the traditional UART interface to accelerate the communication speed between HART modulation and demodulation chip and CPU. Compared to the traditional URAT interface, the AXI4 bus interface can transmit 32 bits of 8 bytes in parallel, and the data transfer speed can reach the NS level. Through the interconnection of AXI4 bus module and CPU, the structure function configuration and data interaction are realized. The high-speed communication interface design of HART modulation and demodulation chip was verified based on FPGA platform. The results show that the architecture can effectively identify HART communication protocol, the data interaction between CPU and HART chip reaches NS level, and the correct rate of modulation and demodulation reaches 100%, which meets the requirements of HART communication protocol.

**Key words:** communication chip architecture; chip interconnection; HART communication protocol; communication interface

## 0 引言

芯片产业是制造业的上游,被称为“工业粮食”,是制造业必不可少的核心技术<sup>[1]</sup>。我国目前正大力进行制造转型,促进高端制造业的发展,在这个过程中芯片产业成为极其重要的环节。随着物联网互联网的发展,通信技术也迎来了科技变革,通信技术以移动接入、实时通信、宽带传输、泛在计算、传感互联等技术表现形式成为大力发展的技术领域<sup>[2]</sup>。

在现代化工厂中,HART(Highway Addressable Remote

Transducer,可寻址远程传感器高速通道的开放通信协议)转置提供具有相对低的带宽,适度响应时间的通信<sup>[3]</sup>,经过10多年的发展,HART技术在国内外已经十分成熟,并已成为全球智能仪表的工业标准<sup>[3]</sup>。但在工业以太网与工业物联网的大背景下,传统的HART仪器仪表与HART传统芯片面临着变革与挑战,目前HART协议芯片存在设计种类单一、结构简单、所支持的设备和CPU控制设备类型有所局限、传输速率低下等情况,主要面临着以下挑战:

\* 基金项目:国家重点研发计划资助(2020YFB1711001);河北省省级科技计划(199477141G,18211833D);河北省引智项目:基于多源视觉融合的病房智能看护系统

(1) 传统 HART 芯片单一对应 HART 仪器仪表与单一 CPU 控制端, 在大型厂间内布线数量大, 成本高<sup>[4-5]</sup>。

(2) 传统的 HART 芯片无时间同步机制, 数据延迟不可控。

(3) 传统 HART 芯片一个 CPU 对应一个 HART 芯片, 只对所控制的设备进行数据读写单一过程, 智能仪表运行时与控制系统的互动有待提高, 智能仪表间缺乏互操作<sup>[6-7]</sup>。

针对上述问题, 本文提供一种新型的可互联 HART 通信协议芯片的架构。

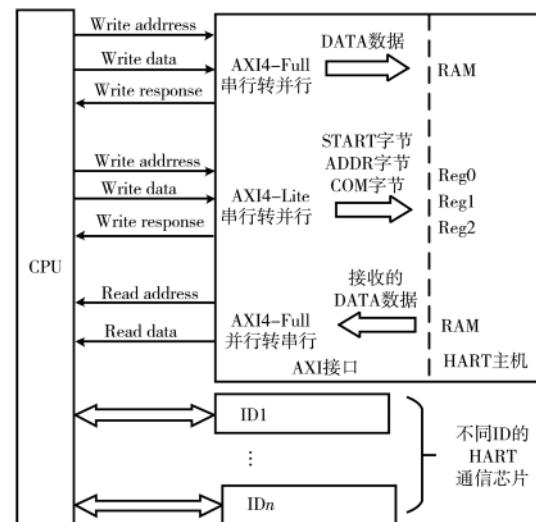

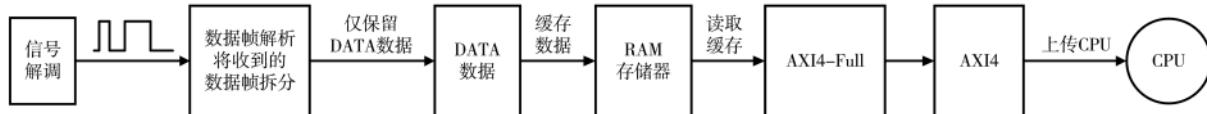

### 1 AXI(Advanced eXtensible Interface)总线模块设计

本文所设计的 AXI4 总线模块是与 CPU(Central Processing Unit)进行数据交互总线接口, 该模块由两部分构成, 分别为 AXI4-Lite 总线接口和 AXI4-Full 总线接口。其中 AXI4-Lite 总线接口用于连接 CPU 和芯片内的寄存器堆栈, 传输 CPU 发出的 START 转态字节、ADDR 设备地址字节与 COM 命令字节以及波特率等控制信息较短的字节, 是 HART 芯片与 CPU 短字节信息交互接口。在 HART 协议规定中, START 转态字节占用一个字节宽度, 决定着 HART 芯片使用的结构是“长”结构模式、“短”结构模式还是“突发模式”。ADDR 地址字节, 则包含了主机地址和从机地址, 可通过 CPU 写入不同的设备地址, 调取所需的设备信息。COM 命令字节, 该字节的范围为 253, 用十六进制 0~FD 表示, 31、127、254、255 为预留值, 用来表示主机需要从机执行的动作<sup>3</sup>。其中 AXI4-Full 总线接口模块实现与 CPU 相连, 用于 CPU 读写片内 RAM 存储器, 实现数据帧结构的信息交互, 其中 AXI4-Full 总线接口用于连接 CPU 和 RAM 存储器, RAM 存储器存储 HART 芯片与 CPU 交互的长字节 DATA 数据。AXI4 总线所特有的握手机制, 使 CPU 与 HART 芯片在数据交互上更加稳定可靠, 大大降低数据传输的错误概率, 通过 CPU 分配 AXI4 多个 ID, 可以实现一个 CPU 挂多个 HART 芯片, 并对不同 HART 芯片所连接的设备节点进行独立的数据交互或者设备命令控制。AXI 总线与 CPU 数据交互流程如图 1 所示。

### 2 增设 RAM 存储器模块

本文增设的 RAM 存储器模块为双端口 RAM, 有两个端口读写, 大大增加了对 CPU 和从机设备数据存储效率。根据寄存器堆栈的 BCNT 位计数器, 确定 CPU 数据字节位宽, 分配出 RAM 存储器地址范围, 按照 RAM 地址递增缓存 CPU 写入的数据字节。RAM 存储器的设计不仅解决了数据存储问题, 而且 RAM 数据存储模块也解决了 CPU 与 HART 芯片通信时钟和 HART 芯片与 HART 设备节点通信时钟不匹配问题, HART 芯片内部模块时钟在 500 kHz 左右, HART 芯片传输速率在 1.2 kb/s<sup>[4]</sup>, 而传统的 HART 芯片不带有缓存模块, CPU 读写 HART 芯片数据也需要同样的时钟速度, 而加入 RAM 数据存

图 1 AXI4 总线与 CPU 数据交互传输流程

储模块之后, CPU 与 HART 芯片时钟模块可以根据需求设定, 使更高效率读取 HART 芯片数据。

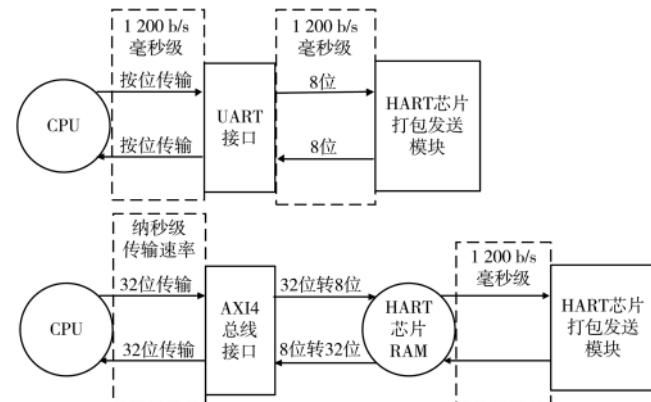

传统 HART 通信芯片与本文所设计的 HART 通信芯片传输速率对比如图 2 所示。

图 2 HART 芯片传输速度对比图

图 2 所示上方为传统 HART 通信芯片传输速率图, 由于没有 RAM 缓存模块, CPU 必须与 HART 通信芯片同步时钟, 这样才可以正常通信, 通信速度为 HART 通信协议所规定的 1 200 b/s, 可到达毫秒级的传输速度<sup>[8]</sup>, 所使用的 UART 接口将 HART 芯片内部并行 8 位数据转成串行 1 位数据与 CPU 进行通信<sup>[9]</sup>。而下方为本文所设计的 HART 芯片架构, 由于新增 RAM 存储器模块, CPU 可直接以纳秒级的速度 32 位数据直接通过 AXI4 总线接口传输给 RAM 存储器缓存, HART 通信芯片再以 1 200 b/s 的通信速度进行调用, 新结构对芯片的通信效率和传输速度的数量级改变显而易见。

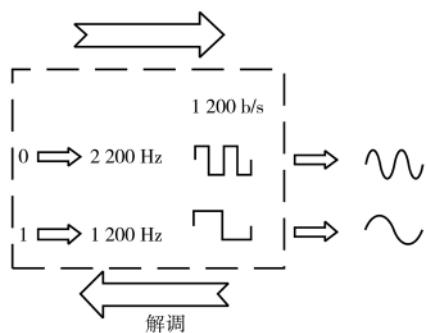

### 3 调制解调模块设计

与 FF 和 Modbus 等数字通信协议不同, HART 通信协议并不是直接发送接收 0、1 数字信息, 而是发送和接

收两种频率的调制和待解调的方波信号,当芯片收到方波频率信号时,需要将其解调成可以处理的二进制0、1数字信号,同理,HART芯片将数据发送给HART仪器仪表之前需要将二进制0、1数字信号调制成两种频率的方波信号。根据HART通信协议的规定,两种方波信号分别为2 200 Hz和1 200 Hz分别代表数字信号0、1<sup>[10-11]</sup>。本文所设计的芯片架构所处理的调制解调过程如图3所示。数据传输波特率为1 200 b/s。

图3 调制解调过程

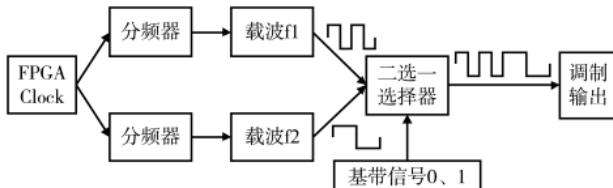

具体调制解调过程如下:首先是调制硬件实现流程如图4所示。

图4 调制硬件实现流程

本文所提出的可互联HART通信协议芯片架构的设计及验证是基于FPGA平台进行的,FPGA输入的时钟为50 MHz,将50 MHz的时钟频率通过所设计的计数器模块降频,分别降为2 200 Hz和1 200 Hz频率,使降频的频率作为载波频率,通过接收RAM存储器的0、1数据,通过二选一选择器将两种频率选择出来并输出。0、1分别对应2 200 Hz方波和1 200 Hz频率<sup>[6]</sup>。

其次,解调硬件实现流程如图5所示。

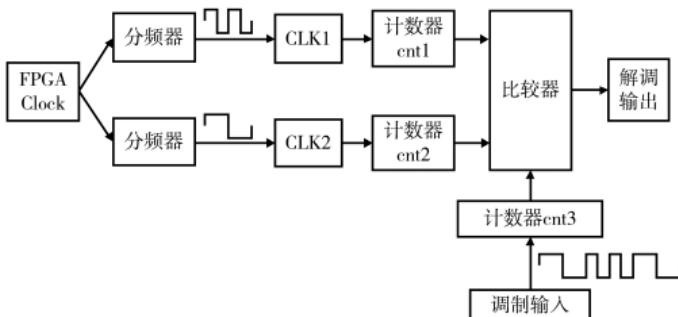

图5 解调硬件实现流程

解调过程主要是将调制好的两种频率的方波信号解调成0、1数字信号进行数据包处理,首先根据FPGA系统时钟50 MHz进行设计处理,因HART通信协议规定传输速度为1 200 b/s,所以设计更新频率为1 200 Hz,将50 MHz系统频率通过计数器分频降为1 200 Hz,并对时钟上升沿进行计数处理,在此同时对输入的待解调信号同样进行脉冲上升沿计数,通过比较器对比两个计数器的数值,若相等则是1 200 Hz信号,若不相等计数值cnt2大于计数值cnt1,则被判定输入频率为2 200 Hz信号,每次比较清空计数器数值,每1 200 Hz更新一次,即每1 200 Hz输出一次解调结果,根据2 200 Hz对应二进制0和1 200 Hz对应二进制1,来输出二进制结果。

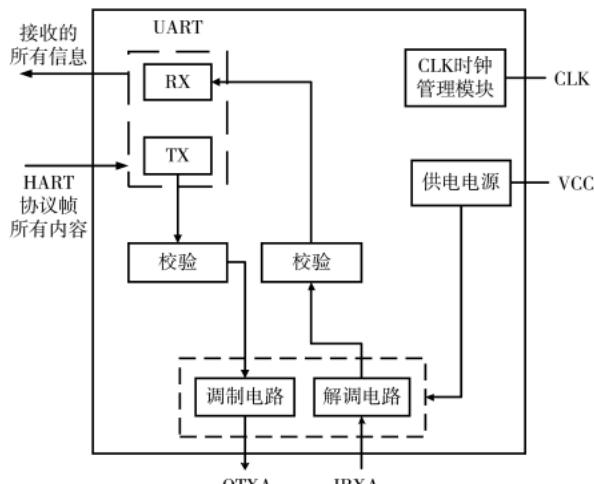

#### 4 可互联HART芯片总体架构及运行流程

现在市场上应用比较多的HART芯片结构如图6所示,主要是通过URAT串口进行数据交换,没有缓存,无法分配芯片地址,结构简单,功能单一<sup>[12]</sup>。

图6 常用HART芯片结构

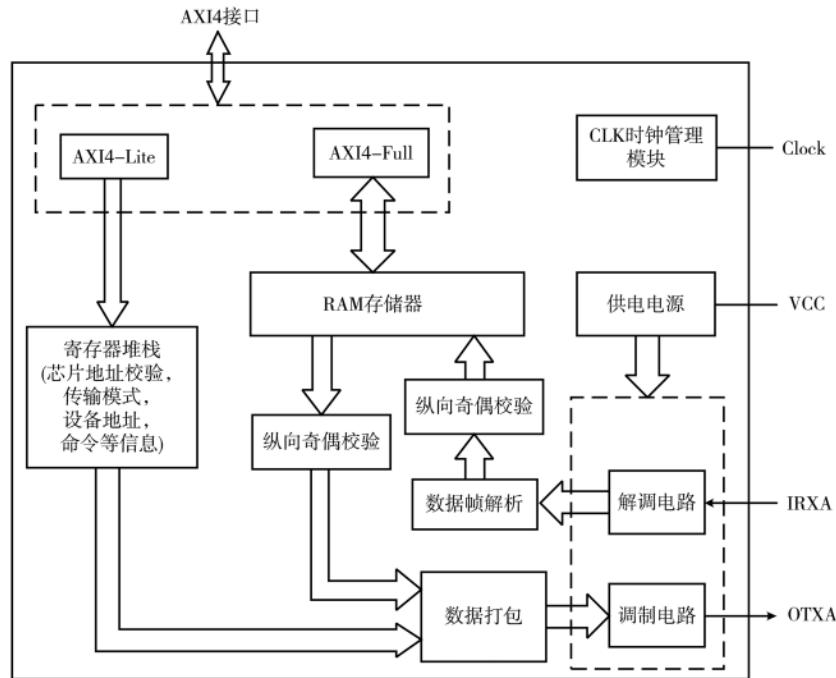

本文所设计的可互联HART芯片总体架构如图7所示,该架构解决了当下HART芯片所面临的问题,配置信息与数据信息独立化,以AXI4总线接口代替UART接口,实现地址分配,多芯片与CPU互联功能,增设RAM存储器,实现数据的缓存功能等。

本文所设计的可互联HART芯片与CPU进行数据交互的读写过程如图8、图9所示,其中图8为数据下行过程,将CPU数据信息传输给下位机。图9为从设备响应上位机过程的数据传输过程。

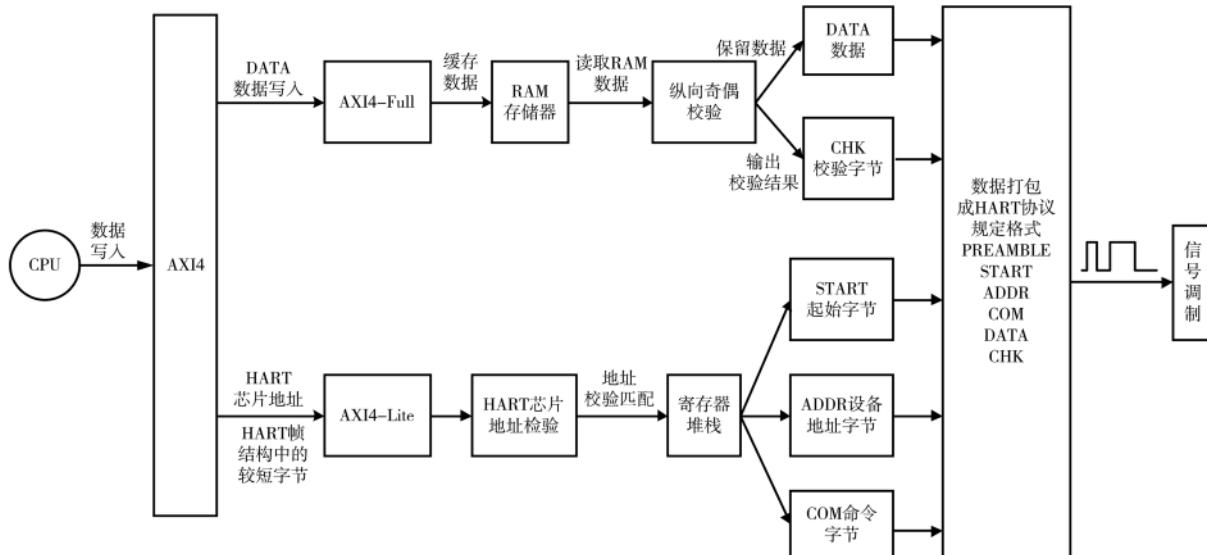

下面以写过程介绍本文芯片架构通信流程。

首先当CPU向从设备写入数据时,以广播的形式发送HART芯片地址和要写入HART芯片的数据,所有HART芯片通过AXI4接口接收数据,并将CPU发送的HART芯片地址与自己已经配置好的地址对比,如果地址一样,则该HART芯片与CPU建立数据交互。

通过AXI4-Full将数据信息写入RAM存储器,通过

图 7 可互联 HART 芯片总体架构

图 8 数据下行过程

图 9 从设备响应过程

AXI4-Lite 将配置信息写入寄存器堆栈，配置信息包括 START 转态字节、ADDR 设备地址字节与 COM 命令字节以及波特率等控制信息。数据信息包括 HART 芯片与 CPU 交互的长字节 DATA 数据。

对从 RAM 存储器中读取的 DATA 数据字节进行纵向奇偶校验，得到的校验结果为 CHK 校验字节。

数据打包模块调用寄存器堆栈已存入的 START 字

节、ADDR 地址字节和 COM 命令字节以及 DATA 数据字节和 CHK 校验字节，并将这些字节按照 HART 协议要求进行打包，并加入 HART 协议 PREAMBLE 导言字节，导言字节由 5~20 个十六进制 FF 所组成，打包完成之后由低位到高位分别为 PREAMBLE 导言字节、START 起始字节、ADDR 地址字节、COM 命令字节、DATA 数据字节、CHK 校验字节，将打包好的数据按位发送到调制模块<sup>[13]</sup>。

调制模块由系统时钟分频出来 2 200 Hz 和 1 200 Hz 载波频率, 通过 0、1 基带信号选择出对应的频率, 当接收到数据信号为 0 时调制成 2 200 Hz 方波信号, 接收数据为 1 时调制成 1 200 Hz 信号作为 HART 芯片输出<sup>[14-15]</sup>。

## 5 FPGA 通信验证

本文所提出的 HART 芯片架构验证平台为 FPGA 平台, 通过搭建主从架构, 验证 AXI4 总线数据的接收、解包、打包、调制、解调等功能, 本次以 CPU 数据传输到从设备端为例进行实验验证。

整体仿真结构框架图如图 10 所示。

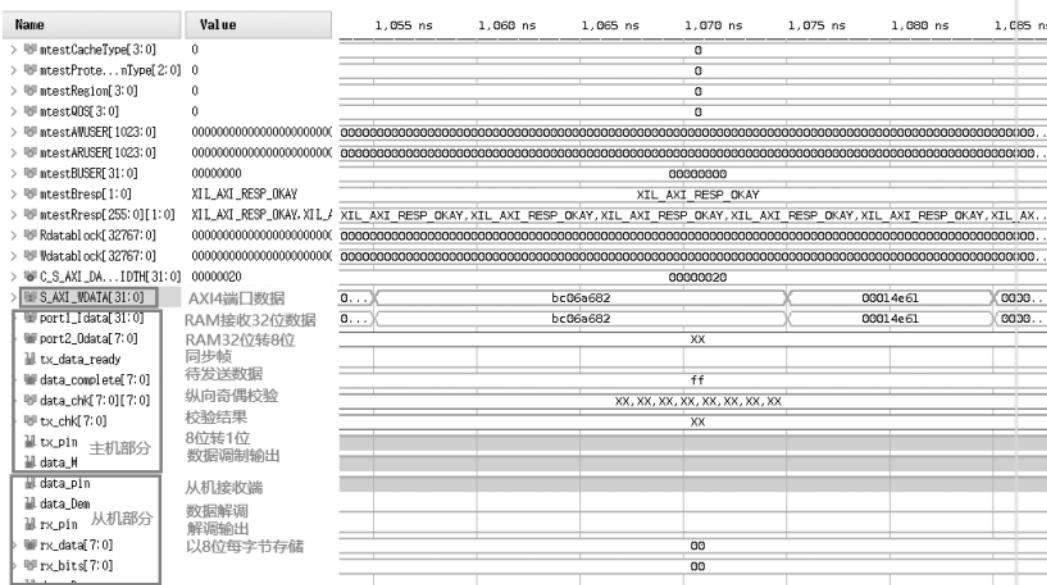

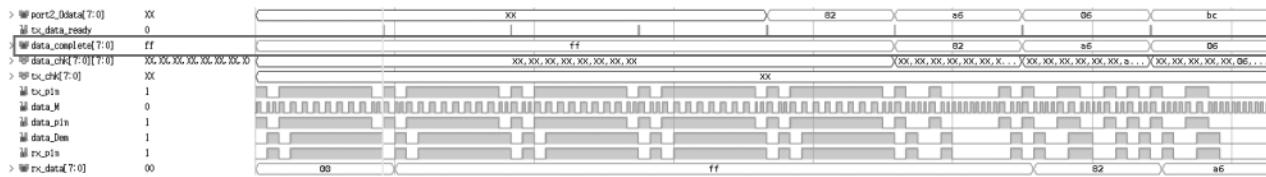

图 10 介绍了 AXI4 端口数据、主机部分以及从机部分, 由图可直观显示运行时间, 在 1 685 ns 时已经将 72 位 9 字节数据写入 RAM 存储, 实现纳秒级别的传输速度。

数据以 32 bit 同时通过 AXI4 总线端口输入, 而芯片内部处理为 8 bit 一个字节的情况处理, 所以输入端搭建 32 bit 转 8 bit 的模块, 使数据按 8 bit 一组缓存到 RAM 存储器中。验证整体波形图, 如图 11 所示。

将 CPU 数据存储到 RAM 存储器并转换成 8 bit 数据之后, 通过 HART 打包模块进行调用, 将数据连续接到导言字节 FF 之后, 如图 12 所示。

port2\_0data <= ram\_data[j][(port2\_addr\*8+7) - 8];

图 11 32 位转 8 位算法

数据打包的同时进行发送, 当数据发送完成之后进行校验, 校验结果再打包到数据帧结尾, 如图 13 所示。

按照 HART 通信协议打包好之后, 由低到高以 HART 协议 1 200 b/s 通信速率按位发送给调制模块, 将二进制 0、1 数据调制成两种频率的方波调制输出。从设备首先通过解调模块接收到调制的数字信号, 通过比较器将频率信号解调成二进制 0、1 数据信号, 上传给从设备接收解包。

本文所设计的 HART 芯片调制解调验证仿真图如图 14 所示。

由图 14 可清晰看出成功调制成两种频率, 通过从设备数据解调之后, 与主设备待调制数据相同, 数据解析成功。

最后将数据进行存储, 完成数据通信过程, 完成实验验证。

## 6 结论

本文介绍了一种 HART 调制解调芯片高速通信接

图 10 仿真结构

图 12 数据打包

图 13 纵向奇偶校验帧打包

图 14 调制解调硬件仿真图

口设计,通过对比现有的 HART 通信芯片,设计了一款全新的 HART 芯片架构。采用 AXI4 总线的特征,可实现单个 CPU 挂载多个 HART 芯片设备,实现多芯片互联功能,搭配 RAM 存储器,实现数据的缓存处理,实现高速接收 CPU 数据的同时,满足 HART 协议规范传输速度,通过 FPGA 平台设计两个 IP 核,实现两个 IP 的数据交互,由此验证了该设计方案的可行性与合理性,可识别和传输满足 HART 协议规范的数据类型。

#### 参考文献

- [1] 段茂强,杨松,刘志峰,等.一种 HART 模拟芯片解调器的实现[J].微计算机信息,2006(20):273-275.

- [2] 丁颖,盛惠兴.一种新型的 HART 信号解调方法[J].河海大学常州分校学报,2004(1):37-39.

- [3] 向晓绎,杨志家.HART 调制解调芯片的设计[J].微计算机信息,2006(31):10-12.

- [4] 盛惠兴,丁颖.HART 调制解调芯片 HT2012 的系统接口设计[J].河海大学常州分校学报,2005(2):35-37,41.

- [5] 卫敏.HART 调制解调器 HT2012 的原理和应用[J].安徽电子信息职业技术学院学报,2004(Z1):280-277.

- [6] 蔡建新,卢爱明.HART 调制解调器 HT2012 的原理和应用[J].电子技术应用,1999(4):43-44.

- [7] 李军.二线制 HART 总线的设计及物理层测试[J].中国仪器仪表,2021(7):69-72.

- [8] 尹亚兰,李琰,徐天奇,等.基于 TDMA 的 wireless HART 网络多路径重传算法[J].云南民族大学学报(自然科学版),2021,30(4):381-386.

- (上接第 5 页)

- [19] 彭瑜.先进物理层——网到底的最后突破[J].自动化仪表,2020,41(4):1-5,10.

- [20] 宋华振.时间敏感型网络技术综述[J].自动化仪表,2020,41(2):1-9.

- [21] 吴欣泽,信金灿,张化.面向 5G TSN 的网络架构演进及增强技术研究[J].电子技术应用,2020,46(10):8-13.

- [22] 关于 TSN,这些内容先了解一下[J].中国仪器仪表,2020(12):41-43.

- [23] 熊伟.OPC UA over TSN 技术路线及分析[J].工业控制计算机,2020,33(2):22-25.

- [24] 苏畅,龚钢军,罗安琴,等.发电系统动态仿真监控平台研究[J].电子技术应用,2017,43(12):65-68.

- [25] 万浩.边缘网关节点中的 OPC UA-TSN 融合技术研究[D].武汉:华中科技大学,2019.

- [26] 李娜.基于 CAN 总线的汽车仪表研究[J].内燃机与配件,

- [9] 周鹏.一种数字 HART 调制解调芯片的设计[J].电子技术与软件工程,2021(13):92-94.

- [10] 钱建康,郑思源.基于无线 HART 协议的蒸汽泄漏监测系统设计[J].控制工程,2021,28(6):1210-1216.

- [11] 方原柏.WirelessHART 基础无线网络设计[J].石油化工自动化,2021,57(3):81-83.

- [12] Anonymous . ADI eyes HART protocol with low power modem[J]. Electronics Weekly , 2012(18).

- [13] ANDORKA F. Wireless HART moves manufacturing forward[J]. Industry Week , 2011 , 260(7).

- [14] REBECCA S , LESLIE M .HART protocol : practical digital communication tool for analog installations[J]. ISHN , 2008 , 42(9) : 57.

- [15] HELSON R B .The HART protocol an enabler for improved plant performance[J]. ISA Transactions , 1996 , 35(2) : 159-164.

(收稿日期:2021-03-23)

#### 作者简介:

张立国(1978-),男,博士,副教授,主要研究方向:机器视觉、虚拟现实、智能机器人、仪器仪表。

李福昆(1996-),通信作者,男,硕士,主要研究方向:工业以太网芯片与系统设计,E-mail:ysulifukun@163.com。

严伟(1966-),男,博士,教授,主要研究方向:集成电路与智能系统、数字集成电路芯片设计、工业以太网芯片与系统、视频编解码芯片设计。

扫码下载电子文档

2022(1):10-12.

- [27] 郭际航.现场总线及其传输介质技术概述[J].光纤与电缆及其应用技术,2020(6):1-6.

- [28] 张奇.在煤矿自动化建设中工业以太网与现场总线技术的运用分析[J].矿业装备,2020(5):126-127.

- [29] 荀庆来,袁韬.工业以太网技术的应用分析[J].科学技术创新,2019(12):72-73.

(收稿日期:2022-02-19)

#### 作者简介:

于会群(1978-),女,博士,副教授,主要研究方向:智能发电自动化、能源互联网。

黄贻海(1997-),男,硕士研究生,主要研究方向:工业通信技术、智能发电技术。

彭道刚(1977-),男,博士,教授,主要研究方向:发电过程自动化、新能源微电网与能源互联网。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所