# 基于 IEC 1158 标准的现场总线芯片设计 \*

张立国<sup>1</sup>, 刘强<sup>1</sup>, 严伟<sup>2</sup>, 李福昆<sup>1</sup>, 吴鹏飞<sup>2</sup>, 王博<sup>2</sup>

(1.燕山大学 电气工程学院, 河北 秦皇岛 066000; 2.北京大学 软件与微电子学院, 北京 100871)

**摘要:** 介绍了一种符合 IEC 1158 标准物理层现场总线芯片架构及其设计实现。芯片设计有曼彻斯特(Manchester)编解码电路、循环冗余校验(Cyclic Redundancy Check, CRC)电路、载波侦测电路、极性纠正电路等功能电路。内置高级可扩展接口(Advanced eXtensible Interface, AXI)电路作为与外置处理器的数据传输总线。完成了此芯片的全部 RTL 代码编写工作, 进行了全面的时序仿真。并以 ZYNQ-7015 为硬件平台, 进行了芯片功能测试, 测试结果表明所设计的芯片达到了设计要求。

**关键词:** 现场总线; IEC 1158; 芯片设计

中图分类号: TN915.04; TN431.2

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211554

中文引用格式: 张立国, 刘强, 严伟, 等. 基于 IEC 1158 标准的现场总线芯片设计[J]. 电子技术应用, 2022, 48(4): 18-23.

英文引用格式: Zhang Liguo, Liu Qiang, Yan Wei, et al. Design of fieldbus chip based on IEC 1158 standard[J]. Application of Electronic Technique, 2022, 48(4): 18-23.

## Design of fieldbus chip based on IEC 1158 standard

Zhang Liguo<sup>1</sup>, Liu Qiang<sup>1</sup>, Yan Wei<sup>2</sup>, Li Fukun<sup>1</sup>, Wu Pengfei<sup>2</sup>, Wang Bo<sup>2</sup>

(1. Institute of Electrical Engineering, Yanshan University, Qinhuangdao 066000, China;

2. School of Software & Microelectronics, Peking University, Beijing 100871, China)

**Abstract:** This paper introduces a kind of physical layer fieldbus chip architecture and its implementation in accordance with IEC 1158 standard. The chip is designed with Manchester codec circuit, Cyclic Redundancy Check(CRC) verification circuit, carrier detection circuit, polarity correction circuit and other functional circuits. The high-speed interface circuit of Advanced eXtended Interface(AXI) is used as the data transmission bus with external processor. The task has completed the RTL code writing of this chip, and carried out a comprehensive time series simulation. The chip function test is carried out on ZYNQ-7015 as hardware platform. The test results show that the chip meets the design requirements.

**Key words:** fieldbus; IEC 1158; chip design

## 0 引言

现场总线(Field bus)是一种工业数据总线, 主要解决工业现场的智能化仪器仪表、控制器、执行机构等现场设备间的数字通信以及这些现场控制设备和高级控制系统之间的信息传递问题<sup>[1-6]</sup>。

IEC 1158 标准定义的现场总线通信模型由物理层、数据链路层、应用层、用户层四部分构成<sup>[7]</sup>。其中, 物理层负责数据传输并可为现场设备供电, 总线数据采用曼彻斯特编码技术进行编码<sup>[8-15]</sup>。本文所设计的现场总线芯片主要实现物理层功能以及部分数据链路层功能, 实现现场设备与总线连接。并内置 AXI4 总线接口, 实现与 CPU 高速、安全的数据交互。

目前已有的符合 IEC1158 标准的现场总线芯片有中

科博微的 FBC0409、美国 Smar 公司的 FB3050、日本 Yamaha 公司的 YTZ420 等。但上述芯片均不具备协议扩展能力, 仅能应用于符合 IEC 1158 标准的特定现场总线系统中, 应用领域单一。且由于与 CPU 交互时均使用私有协议, 导致通用性较差。此外, 受私有协议带宽限制, 以及这些私有协议不具备突发传输能力, 导致芯片与 CPU 进行数据交互的时延较大。

为了解决上述问题, 本文设计了一种符合 IEC 1158 现场总线标准的现场总线芯片。采用标准 AXI 总线接口与 CPU 进行数据交互, 总线位宽为 32 位, 总线频率 100 MHz, 提供 3.2 Gb/s 总线带宽, 实现芯片与 CPU 的高速且安全数据传输。同时, 芯片内置丰富的控制寄存器和状态寄存器, 可通过 AXI 总线配置芯片工作模式或

\* 基金项目: 国家重点研发计划资助(2020YFB1711001); 河北省省级科技计划(199477141G, 18211833D); 河北省引智项目: 基于多源视觉融合的病房智能看护系统

监控芯片运行状态,包括实现协议扩展。此外,对于使用双绞线作为现场总线传输介质的现场总线协议,本芯片设计有极性纠正电路,可自动侦测双绞线载波变化,并在必要情况下进行实时极性纠正,使得现场设备接入总线时,即使正负极颠倒也能正常工作。

### 1 IEC 1158 现场总线模型

IEC 1158 标准的通信模型基于 ISO(International Organization for Standardization, 国际标准化组织)的 OSI(Open System Interconnection Reference Model, 开放式系统互联通信参考模型)7 层模型,取其物理层、数据链路层、应用层,并增加用户层<sup>[9-13]</sup>。

其中,物理层为现场设备供电,且采用 Manchester 编码技术对数据进行编码传输,支持点对点、总线型、菊花链型、树型拓扑结构,数据传输速率为 32.25 kb/s。

数据链路层为系统管理内核和总线访问子层访问总线媒体提供服务,负责链路活动调度、数据的接收与发送、活动状态的探测与响应以及总线上各设备间的链路时间同步。

应用层定义在设备间交换数据、命令、事件信息以及请求应答中的信息格式。

用户层组成用户所需的应用程序,如规定的功能块、设备描述,实现网络管理、系统管理等。

目前符合 IEC 1158 标准的现场总线协议主要有基金会现场总线(Foundation Fieldbus, FF)和 PROFIBUS-PA 等。

### 2 芯片架构设计

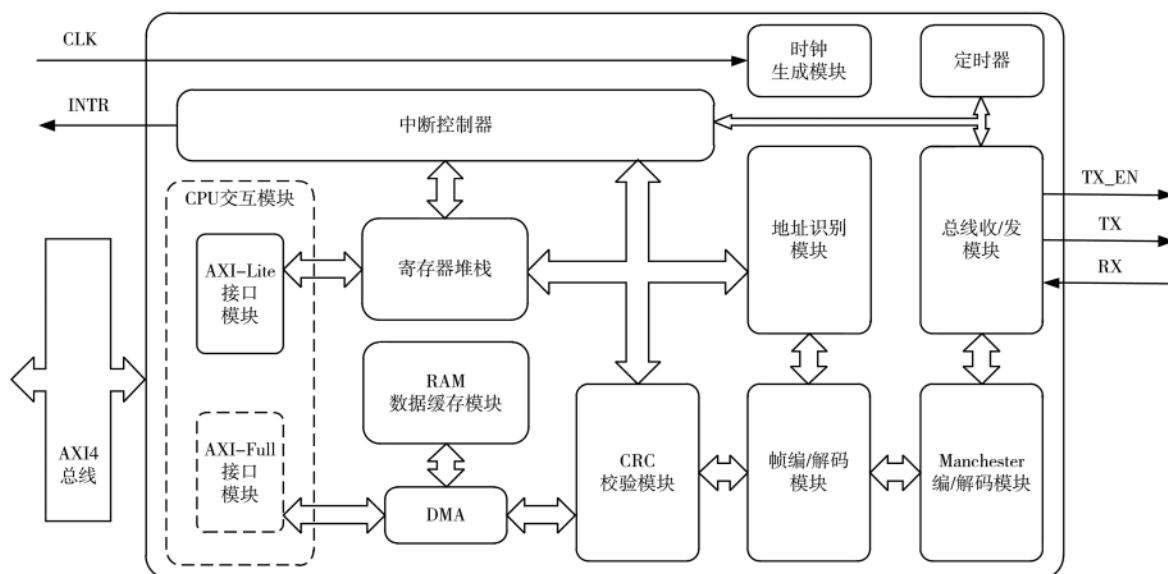

本文所设计的芯片架构如图 1 所示,实现了 IEC 1158 物理层规范及部分链路层功能,如 CRC 校验等。

芯片结构主要包括 AXI 总线接口模块、中断控制器、直接存储器访问控制器(Direct Memory Access, DMA)、随机存取存储器(Random Access Memory, DMA)、寄存器

堆栈、CRC 校验模块、地址识别模块、帧编解码模块、曼彻斯特(Manchester)编解码模块、总线收发模块以及时钟模块。

### 3 CPU 交互方式

AXI 总线协议是 ARM 公司提出的先进微控制器总线体系结构(Advanced Microcontroller Bus Architecture, AMBA)总线协议中最重要的部分。AXI 总线协议由 AXI-Full、AXI-Lite、AXI-Stream 协议构成。其中 AXI-Full 适用于大量数据随机读写,且支持突发传输;AXI-Lite 用于数据量较小的随机读写,适用于操作寄存器;AXI-Stream 适用于无地址的顺序读写。

AXI 总线有 5 个独立传输通道,分别是地址通道(写地址通道、读地址通道)、数据通道(写数据通道、读数据通道)以及应答通道。每次进行数据传输之前,CPU 先通过地址通道告知 AXI 从机设备需要操作的存储器地址,随后 CPU 或 AXI 从设备将数据传输数据通道。在传输完成后,接收方通过应答通道回复发送方,从而确保数据透明传输。

本课题芯片采用 AXI-Full 总线进行数据传输、使用 AXI-Lite 总线进行芯片配置和状态反馈。

其中,AXI-Full 总线通过双通道 DMA 控制器挂载发送缓存 RAM 和接收缓存 RAM,缓存 RAM 与 AXI-Full 总线的总线位宽均为 32 位,AXI 总线工作频率为 100 MHz,提供 3.2 Gb/s 带宽,保证 CPU 与芯片间高速低时延的数据传输。AXI-Full 总线地址通道为 10 位,拥有 1 KB 的 RAM 寻址能力。

AXI-Lite 总线位宽同样为 32 bit,与芯片内部的控制寄存器和状态寄存器相连,用于配置芯片的地址、工作模式、中断响应、测试模式等功能,并将芯片的工作状态如地址信息、所处的工作模式、中断屏蔽信息等传输给

图 1 芯片架构设计图

CPU, 以便实时监控芯片工作状态。

#### 4 现场总线数据传输

符合 IEC 1158 协议规范的现场总线的数据帧一般由前导码、数据和特征码(起始符、结束符)构成<sup>[8]</sup>, 其中, 前导码由 8 位二进制数 10101010 构成, 接收端通过检测前导码进行判断数据传输起始; 起始符表示帧数据开始, 数据帧中的数据紧跟在起始符之后; 结束符标志着一帧的结束, 芯片检测到结束符后复位接收状态。

考虑到符合 1158 规范的现场总线协议的特征码各不相同, 因此, 本文所设计的芯片设计有特征码寄存器, CPU 可配置相应寄存器以使芯片能够识别不同现场总线协议的特征码, 实现协议扩展。

##### 4.1 数据发送过程

发送数据时, CPU 将需要发送的数据编码成位宽为 32 位的数据, 随后通过 AXI-Full 总线发送给芯片内部的发送缓存 RAM。通过 32 位 AXI 总线传输数据到 RAM 中后, 将有效数据字节数写入芯片内部相应寄存器, 芯片可根据寄存器值将 RAM 中相同字节的数据发送到总线。配置完数据字节数后, CPU 配置芯片内部控制寄存器的发送使能位使能芯片发送。芯片若侦测到发送使能信号, 则向 DMA 请求数据, DMA 根据发送数据总量寄存器的值从发送缓存 RAM 中读取相应字节的数据, 之后数据进入数据处理流水线, 为数据添加特征码、计算 CRC 校验码、添加 CRC 帧尾, 对数据进行 Manchester 编码以及数据串行化发送等。

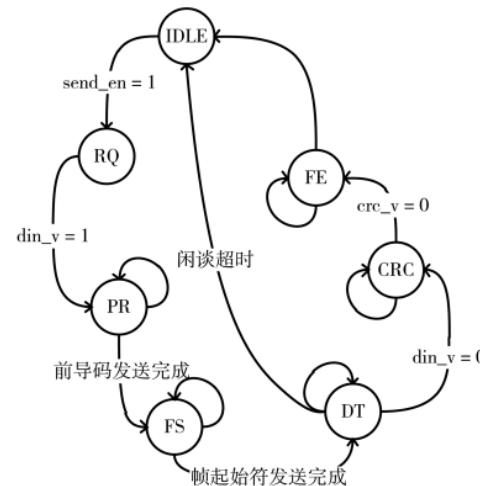

发送行为由发送状态机控制, 发送状态机各状态符号及说明如表 1 所示。

表 1 发送状态机符号说明

| 状态符号 | 功能       | 说明         |

|------|----------|------------|

| IDLE | 空闲状态     | 发送电路空闲     |

| RQ   | 数据请求状态   | 向 DMA 请求数据 |

| PR   | 前导码发送状态  | 编码前导码并发送   |

| FS   | 帧起始符发送状态 | 编码起始符并发送   |

| DT   | 数据发送状态   | 编码数据并发送    |

| FE   | 帧结束符发送状态 | 编码结束符并发送   |

发送状态机状态转移图如图 2 所示。状态机输入信号有发送使能信号 send\_en、DMA 控制器输出的数据有效信号 din\_v、CRC 帧尾计算模块输出的 CRC 有效信号 crc\_v。

IDLE 状态下, 若收到来自 CPU 的发送使能信号, 状态机进入 RQ 状态; 在 RQ 状态下, 发送器向 DMA 控制器发送数据请求信号, 并进入 PR 状态。在 PR 状态下, 若侦测到输入数据有效信号为高电平, 则将来自 DMA 的数据及数据有效信号延迟 2 个时钟周期; 并读取前导码寄存器值, 对其进行 Manchester 编码后传输到现场总线上, 发送完成后进入 FS 状态。在 FS 状态下, 读取起始

图 2 发送状态机状态转移图

符寄存器, 进行 Manchester 编码后将起始符传输到现场总线上, 随后进入 DT 状态。在 DT 状态下开始发送经过延时的数据, 同时启动闲谈定时器。数据发送完成则进入 FE 状态, 或闲谈定时器溢出后, 恢复到 IDLE 状态; FE 状态下发送经过 Manchester 编码的帧结束符, 发送完成后回到 IDLE 状态。

##### 4.2 数据接收过程

芯片的总线数据接收模块侦测现场总线的载波变化, 若侦测到电平变化为 10101010, 则认为现场设备与总线为正接状态, 则直接将接收到的数据输入到后续处理模块; 若侦测到 01010101, 则认为现场设备与现场总线反接, 芯片将接收到的数据输入到极性纠正电路。然后对纠正后的数据进行 Manchester 解码, 进行地址识别以及 CRC 校验, 并将数据输送给 DMA 控制器。DMA 控制器将 8 位数据封装成 32 位数据写入接收缓存 RAM, 同时, 将接收到的字节数写入接收数据总量寄存器中, 并在数据全部写入 RAM 后, 根据目的地址匹配结果和 CRC 校验结果判断是否为本机数据以及数据是否正确。符合判断要求则产生中断信号, 并将中断类型写入中断类型寄存器, 否则不产生中断信号。CPU 检测到中断后读中断类型寄存器的值, 若为数据就绪中断, 则 CPU 读接收数据总量寄存器, 并将字节数转化为 AXI 总线读取次数, 将数据读取到内存, 并还原数据。

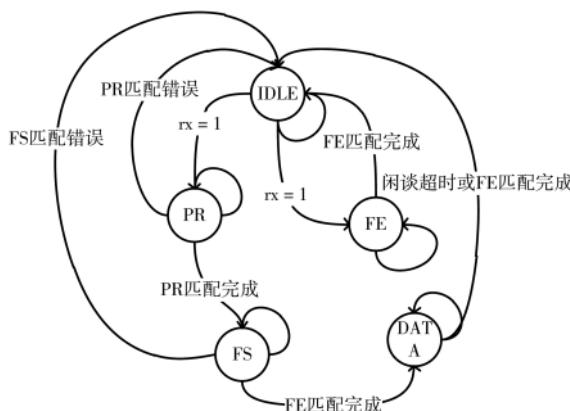

数据接收过程由接收状态机控制, 接收状态机各状态符号及说明如表 2 所示。

表 2 接收状态机符号说明

| 状态符号 | 功能       | 说明           |

|------|----------|--------------|

| IDLE | 空闲状态     | 接收电路空闲       |

| PR   | 前导码接收状态  | 侦测前导码并判断总线极性 |

| FS   | 帧起始符接收状态 | 接收并解码起始符     |

| DT   | 数据接收状态   | 接收并解码总线数据    |

| FE   | 帧结束符接收状态 | 接收并解码结束符     |

接收状态机状态转移图如图 3 所示。状态机输入信号为接收引脚电平信号 rx。

图 3 接收状态转移图

系统启动后状态机处于 IDLE 状态, 当侦测到接收引脚 rx 有载波时, 接收状态机和结束符状态机分别进入 PR 状态和 FE 状态。在 PR 状态下, 对接收的数据进行 Manchester 编码并与前导码比较并判断是否极性反接。若极性反接, 则将后续数据数据极性纠正电路后进行解码, 若所有位全部与前导码匹配, 则结束符状态机进入 FS 状态, 接收状态机进入 FE, 否则, 均回到 IDLE 状态。FE 状态下, 状态机匹配帧结束符, 若匹配错误回到 IDLE 状态, 否则在匹配完成后恢复到 IDLE 状态。在 FS 状态下, 状态机按位匹配帧起始符, 若全部匹配, 则进入 DT 状态, 否则, 回到 RX 状态。在 DT 状态下, 当检测到闲谈超时、结束符匹配状态机已检测到结束符和检测到数据帧的目的地址与本机地址不符, 都恢复到 IDLE 状态, 否则继续接收数据。

考虑到不同现场总线协议帧格式不同, 无法对全部现场总线协议进行地址识别, 因此, 本芯片仅支持对基金会现场总线(Foundation Fieldbus, 简称 FF)协议进行数据帧类型识别与地址识别, 对于其他符合 IEC 1158 标准的现场总线协议, 芯片将数据提交给 CPU 后由 CPU 进行地址识别, 数据帧丢弃与否由 CPU 裁决。

## 5 关键技术实现

### 5.1 Manchester 编码技术的硬件实现

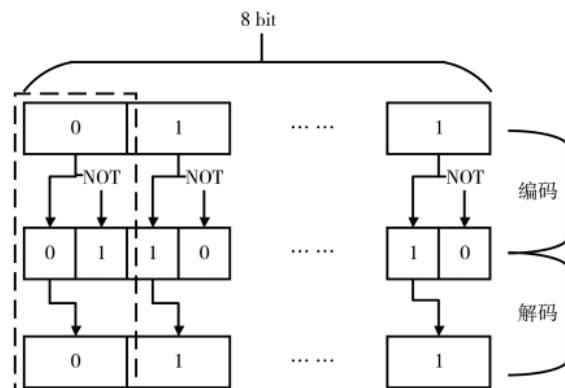

IEC 1158 协议规定物理层数据需要使用 Manchester 编码技术进行编码及解码, 本文芯片设计有全双工 Manchester 编码及解码电路, 如图 4 所示。采用双相 L Manchester 编码方式, 由 8 路并行非门电路及插值电路负责数据编码, 单周期可完成 1 字节数据编码工作。16 位采样电路负责对接收端的数据进行解码, 单周期可解码 2 字节 Manchester 码。

### 5.2 CRC 校验的硬件实现

现场设备所处的电磁环境复杂, 影响现场总线上的数据传输, 导致接收方接收到的数据发生错误, 为了确

图 4 Manchester 编、解码电路原理图

保接收方能对数据准确性做出正确的判断, IEC1158 规定发送方需在数据之后添加 16 位 CRC 校验码。因此, 本文芯片设计有 8 位并行模 2 运算电路, 单周期即可完成 1 字节数据的 CRC 计算任务。为发送的数据计算 16 位 CRC 校验码, 为接收到的数据进行 CRC 校验。

### 5.3 极性纠正

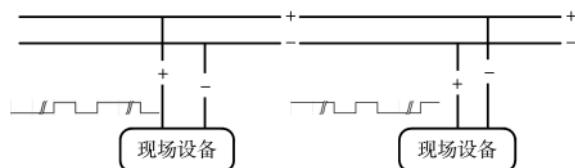

所谓的极性纠正是指, 当现场总线以双绞线作为传输介质时, 芯片有能力通过侦测双绞线上的信号载波变化判断现场设备是否与双绞线反接, 若判断为反接, 芯片须具备对双绞线传输的数据进行实时电平纠正的能力, 实现不论现场设备如何挂载于双绞线上, 设备都能从总线上正确地接收并解析数据。如图 5 所示, 左侧为正接, 右侧为反接。

图 5 现场设备挂载情况示意图

当现场设备与现场总线极性反接时, 现场设备从总线上接收到的电平为正接时的取反, 因此, 本芯片内置极性侦测电路, 当侦测到数据帧前导码为 10101010 时判断为正接。当侦测到前导码为 01010101 时判断为反接, 此时调整门控电路, 将芯片的数据输入端口接入同步反相电路进行极性纠正。

此外, 本文芯片设置有极性纠正测试模式寄存器控制位, CPU 可通过 AXI-Lite 总线配置此控制位, 使能极性纠正测试模式, 芯片接收到的数据将两次通过极性纠正电路, 模拟反接情况, 以便进行芯片功能测试。

### 5.4 协议扩展

对于符合 IEC 1158 规范的各种现场总线协议, 区别主要在数据链路层、应用层和用户层, 而物理层的数据编码方式及传输速率均相同。各现场总线协议在物理层的差异仅在于数据帧的特征码(起始符和结束符)不同,

以及数据的长度不同。为使本芯片通用于符合 IEC 1158 规范的各现场总线系统, 芯片内部设置有可配置的特征码寄存器。用户可根据所使用的现场总线协议规定, 配置特征码以实现对不同现场总线协议的支持, 同时可通过闲谈寄存器配置满足不同协议的总线占用时间要求。

## 6 FPGA 原型验证

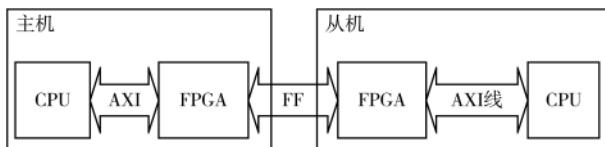

验证平台硬件选用黑金基于 FPGA 芯片的 ZYNQ-7015 开发板, 软件环境为 Vivado 以及 Vivado SDK, 图 6 为芯片测试架构图, 芯片运行在 FPGA 上, CPU 为 ARM 处理器, 验证所用现场总线协议为基金会现场总线协议(FF)。

图 6 芯片测试架构

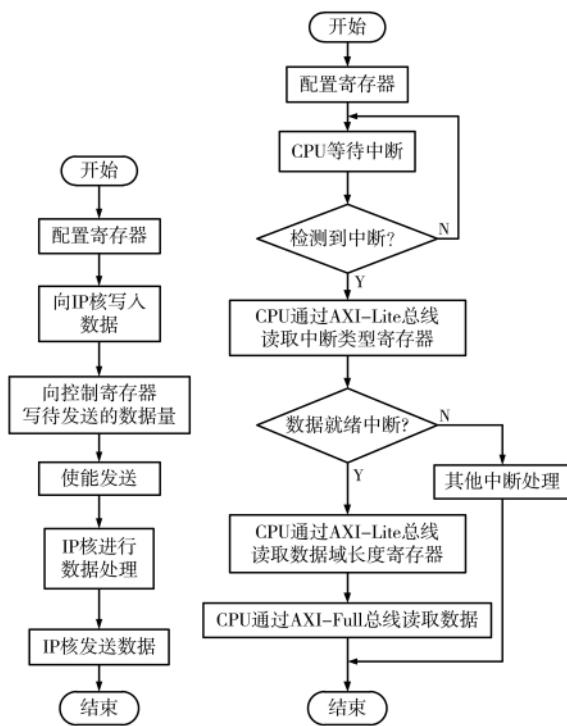

测试流程如图 7 所示, 左侧为 CPU 驱动现场总线芯片发送数据的流程图, 右侧为 CPU 等待现场总线芯片中断信号进行相应数据处理流程图。系统启动后, 主站及从站 CPU 通过 AXI-Lite 总线配置现场总线芯片工作模式, 主站 CPU 将指令通过 AXI-Full 总线发送给现场总线芯片并使能发送, 现场总线芯片侦测到使能信号后采用流水线模式对数据进行数据处理并发送到现场总线上。从站现场总线芯片侦测到载波后进行数据解码等处理后产生中断信号, CPU 响应中断后通过 AXI-Lite 总线读取现场总线芯片的中断类型寄存器。若为数据就绪

图 7 芯片测试流程图

中断, 则通过 AXI-Full 总线读取现场总线芯片内部的数据缓存。从站 CPU 进行裁决后采用与主站相同的工作流程驱动从站现场总线芯片发送回复数据。

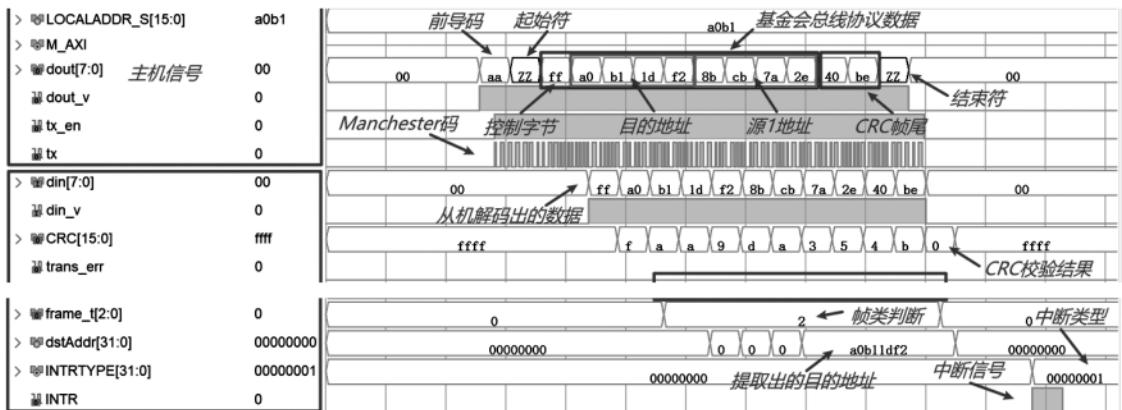

测试所用协议为符合 IEC 1158 标准的基金会现场总线(FF)协议, 通过 CPU 配置芯片为内部回环模式后采集到的发送(主机)与接收(从机)时序。图 8 为测试过程中上位机软件的部分打印信息, 包括读取的芯片配置信息、工作模式和发送(TX)及接收(RX)的数据。图 9 为芯片测试时抓取的部分波形图。

```

-----FF Master回环测试-----

/*

中断配置:

使能数据就绪中断; 使能CRC校验错误中断; 使能闲谈超时中断;

最大闲谈时间: 4096字节

回环模式: 开

极性纠正测试模式: 关

*/

TX      RX

TD0:b5  RD0:b5

TD1:b1  RD1:b1

TD2:1d  RD2:1d

TD3:f2  RD3:f2

TD4:8b  RD4:8b

TD5:cb  RD5:cb

TD6:7a  RD6:7a

TD7:6e  RD7:6e

-----/

```

图 8 上位机打印的测试过程信息

## 7 结论

本文介绍了一种支持在 IEC 1158 现场总线标准范围内进行协议扩展的现场总线芯片架构, 拥有 AXI 高速 CPU 接口、Manchester 编解码电路、CRC 校验电路、极性侦测及纠正电路。拥有丰富的控制寄存器及状态寄存器, 可配置芯片运行模式, 如中断屏蔽模式、回环模式, 极性纠正测试模式等。并基于 ZYNQ-7015 开发板进行了芯片功能验证, 验证结果显示本文所设计的芯片达到了设计要求。

## 参考文献

- [1] 胡超志.火力发电厂电气控制系统中现场总线技术的应用及故障排除探索[J].应用能源技术,2021(10):33-35.

- [2] 郭景辉.现场总线在发电厂全厂控制系统中的应用[J].大众用电,2021,36(6):83-84.

- [3] 刘艳.基于现场总线技术的智能低压配电系统[J].电工技

图 9 芯片测试波形图

- 术, 2021(16): 105–106, 108.

- [4] 梁利军. 现场总线技术及其在纺织机械上的应用探讨[J]. 轻纺工业与技术, 2021, 50(9): 35–36.

- [5] 韩东阳. 现场总线通信控制器的优化设计[D]. 沈阳: 沈阳工业大学, 2019.

- [6] 石泽宇. 现场总线对自动化仪表与系统的影响及其发展路径探索[J]. 无线互联科技, 2017(4): 72–73.

- [7] 缪学勤. IEC1158 现场总线技术概况[J]. 仪器仪表标准化与计量, 1998(5): 2–8.

- [8] 杨程, 张焕欣, 姜智锐, 等. 应用于核电站 DCS 的 PROFIBUS-PA 现场总线接口电路设计[J]. 自动化与仪表, 2020, 35(9): 93–96.

- [9] 王冬, 冷强. DCS 本地总线通信协议与 FF H1 设备互操作技术研究与实现[J]. 仪器仪表用户, 2021, 28(10): 43–47.

- [10] 叶宁, 杜策, 李启峰, 等. 基于 FF 型总线标准化功能块的应用分析[J]. 电工技术, 2021(15): 116–118, 121.

- [11] 刘振民. PROFIBUS-PA 总线技术在工程项目中的应用[J]. 有色冶金设计与研究, 2021, 42(4): 21–23.

- [12] 王晓斌. PROFIBUS PA 总线在炼钢连铸控制系统中的应用与研究[J]. 工业仪表与自动化装置, 2021(4): 122–

(上接第 17 页)

- 子世界, 2013(21): 6–7.

- [4] 肖军方, 彦军. 嵌入式现场总线协议转换网关开发[J]. 计算机工程, 2006(12): 255–257.

- [5] LOU G, CAI H, LI S. Research and implementation of ARM-based fieldbus protocol conversion method[C]//International Conference on Computer and Communication Technologies in Agviculture Engineering, 2010.

- [6] RONG Y, FENG Z, MIN L, et al. Communication model of embedded multi-protocol gateway for MRO online monitoring system[C]. IEEE 19th International Conference on Computer Supported Cooperative Work in Design, 2015.

125.

- [13] 张浩龙, 刘威, 孔德伟, 等. FF 与 Profibus 现场总线在火电厂应用中的故障诊断及处理[J]. 自动化仪表, 2020, 41(7): 102–106.

- [14] 裴坤. 面向炼油化工的基金会现场总线主控系统[Z]. 浙江中控技术股份有限公司, 2018-11-18.

- [15] HOSKE M T. FieldComm group collaborates on foundation fieldbus, HART technologies, FDI[J]. Control Engineering, 2015, 62(3): 28.

(收稿日期: 2021-03-24)

## 作者简介:

张立国(1978-), 男, 博士, 副教授, 主要研究方向: 机器视觉、虚拟现实、智能机器人、仪器仪表。

刘强(1996-), 通信作者, 男, 硕士, 主要研究方向: 工业以太网芯片与系统设计, E-mail: 894675331@qq.cpm。

严伟(1966-), 男, 博士, 教授, 主要研究方向: 集成电路与智能系统、数字集成电路芯片设计、工业以太网芯片与系统、视频编解码芯片设计。

扫码下载电子文档

(收稿日期: 2022-03-08)

## 作者简介:

王雪迪(1996-), 男, 硕士研究生, 主要研究方向: 工业以太网、集成电路设计。

王博(1996-), 男, 硕士研究生, 主要研究方向: 工业以太网、集成电路设计。

时广轶(1979-), 男, 博士, 教授, 主要研究方向: MEMS 惯性器件、碳纳米管传感器设计与应用技术。

严伟(1966-), 通信作者, 男, 博士, 教授, 主要研究方向: 视频编解码、无线通信电路设计, E-mail: yanwei@ss.pku.edu.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所