# 基于 FPGA 的大功率压电陶瓷数字驱动电源设计

康玉宽<sup>1</sup>, 郑翰琳<sup>2</sup>, 黄 巧<sup>2</sup>, 申 伟<sup>2</sup>

(1.西南科技大学 城市学院, 四川 绵阳 621000; 2.西南科技大学 信息工程学院, 四川 绵阳 621000)

**摘要:** 目前叠堆型压电陶瓷最高能够产生 70 kN 的推力,且具有纳米级的精密定位。为提高压电陶瓷驱动电源的输出性能和精确度,提出了一种基于 FPGA 的大功率高精度压电陶瓷数字驱动电源的设计,具有 100 倍固定输出增益。该驱动电源以 FPGA 作为控制核心,采用半桥逆变的电路拓扑,同时引入闭环控制调节输出电压。在等效电容为 5  $\mu\text{F}$  的压电陶瓷负载下,该驱动电源的输入带宽为 10 Hz~800 Hz,输出功率可达 1 kW,电压纹波小于 30 mV,输出精度高达 99.3%。实验结果表明,该驱动电源可应用于振动台、六足控制平台等叠堆型压电陶瓷应用领域中,具有良好的驱动性能。

**关键词:** 压电陶瓷; 驱动电源; FPGA; 大功率; 高精度

中图分类号: TN86; TN384

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.212146

中文引用格式: 康玉宽, 郑翰琳, 黄巧, 等. 基于 FPGA 的大功率压电陶瓷数字驱动电源设计[J]. 电子技术应用, 2022, 48(4): 39~43.

英文引用格式: Kang Yukuang, Zheng Hanlin, Huang Qiao, et al. Design of high power piezoelectric ceramic digital drive power based on FPGA[J]. Application of Electronic Technique, 2022, 48(4): 39~43.

## Design of high power piezoelectric ceramic digital drive power based on FPGA

Kang Yukuang<sup>1</sup>, Zheng Hanlin<sup>2</sup>, Huang Qiao<sup>2</sup>, Shen Wei<sup>2</sup>

(1. City College, Southwest University of Science and Technology, Mianyang 621000, China;

2. School of Information Engineering, Southwest University of Science and Technology, Mianyang 621000, China)

**Abstract:** At present, the stacked piezoelectric ceramics can generate a thrust of up to 70 kN, and have nanometer-level precision positioning. In order to improve the output performance and accuracy of piezoelectric ceramic drive power, a design of high-power and high-precision piezoelectric ceramic digital drive power based on FPGA is proposed, which has a fixed output gain of 100 times. The driving power supply uses FPGA as the control core, adopts a half-bridge inverter circuit topology, and introduces closed-loop control to adjust the output voltage. Under a piezoelectric ceramic load with an equivalent capacitance of 5  $\mu\text{F}$ , the input bandwidth of the drive power supply is 10 Hz~800 Hz, the output power can reach 1 kW, the voltage ripple is less than 30 mV, and the output accuracy is as high as 99.3%. The experimental results show that the driving power supply can be used in the application fields of stacked piezoelectric ceramics such as vibrating table and hexapod control platform, and has good driving performance.

**Key words:** piezoelectric ceramics; driving power supply; FPGA; high power; high precision

## 0 引言

随着国内科技的迅速发展,国内大部分领域对大推力、高精度的位移装置产生了迫切的需求。压电陶瓷具有逆压电效应的特性,而压电陶瓷叠堆由多片压电陶瓷组成,它们在机械上串联,在电路上并联,总推力相当于所有陶瓷片推力的总和<sup>[1]</sup>。叠堆型压电陶瓷具有体积小、响应速度快、推力大、精度高等优点,在国内外已经得到了广泛的应用<sup>[2]</sup>。

压电陶瓷的使用离不开驱动电源,而压电陶瓷的工作性能大部分由驱动电源的性能好坏决定,因此对压电陶瓷驱动电源有了更高的要求。目前压电陶瓷驱动电源主要分为电荷驱动型和电压驱动型两类<sup>[3]</sup>,电荷型的驱

动方式存在低频稳定性差,静态工作下具有电荷泄露大、非线性、零点漂移严重的缺点;电压型的驱动方式结构简单、可靠性高、纹波小,在静态、低频应用中得到普遍的应用<sup>[4]</sup>。

因此本文在电压型半桥逆变拓扑<sup>[5]</sup>的基础上,基于 FPGA 设计了一款数字控制的大功率、高精度、低纹波的压电陶瓷驱动电源。

## 1 系统结构设计

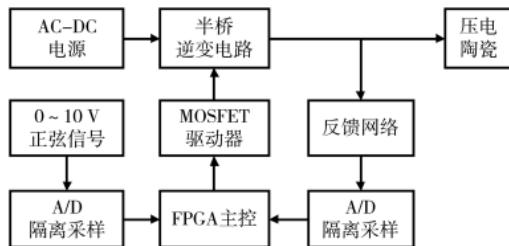

压电陶瓷驱动电源系统结构如图 1 所示。该系统以现场可编程逻辑门阵列(FPGA)作为控制核心,通过 18 位的隔离采样 A/D 将输入带宽 10 Hz~800 Hz、幅值 0~5 V 的正弦模拟信号和输出端反馈网络所采集到的模拟信

图 1 系统结构图

号转换为数字信号,系统采用 PID 控制算法将该两种数据以单周期的调节方式计算输出 PWM 占空比,再通过 MOSFET 驱动电路来精准地控制半桥逆变电路的输出,在经过巴特沃斯滤波器之后输出到压电陶瓷,实现对压电陶瓷的精确驱动。半桥逆变电路的电源电压由 AC-DC 电源提供。

## 2 硬件电路设计

### 2.1 半桥逆变电路

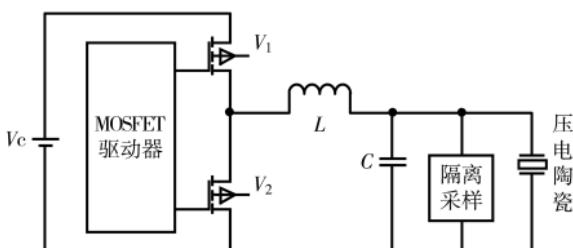

半桥逆变电路如图 2 所示, $V_1$  和  $V_2$  分别为半桥逆变电路的上桥臂 MOSFET 和下桥臂 MOSFET,由驱动器提供开关频率  $f$  为 100 kHz 的互补 SPWM 低压信号,为防止上下两个桥臂的互导通使电路短路,需要在互补的两路 SPWM 之间加入一定的死区时间。AC-DC 电源  $V_c$  输出高压直流经过半桥逆变电路斩波后,经过由电感  $L$  和电容  $C$  所构成的巴特沃斯低通滤波器<sup>[6]</sup>得到低纹波、高精度的电压,用于驱动压电陶瓷。

图 2 半桥逆变电路

### 2.2 滤波电路

为保证压电陶瓷驱动电源输出的纹波小,需要合理地设计滤波器参数。巴特沃斯滤波器的幅度平方函数定义为:

$$|H(j\lambda)|^2 = \frac{1}{1+C^2\lambda^{2N}} \quad (1)$$

式中  $C$  为常数,  $N$  为滤波器的阶次,  $\lambda$  为归一化低通截止频率。

因此巴特沃斯滤波器在频带内的衰减定义为:

$$\alpha = 10 \lg \frac{1}{|H(j\lambda)|^2} = 10 \lg (1 + C^2 \lambda^{2N}) \quad (2)$$

由式(2)可得滤波器的阶数  $N$  为:

$$N = \frac{\lg a}{\lg \lambda_s} \quad (3)$$

$$\text{式中, } a = \sqrt{\frac{10^{\frac{\alpha_s}{10}} - 1}{10^{\frac{\alpha_p}{10}} - 1}}, \lambda_s = \frac{\Omega_s}{\Omega_p}.$$

本文所设计的压电陶瓷驱动电源的输出带宽为 10 Hz~800 Hz,因此通常截至频率  $\Omega_p$  为 800 Hz,通常衰减  $\alpha_p$  为 3 dB,根据压电陶瓷叠堆的特性,其工作频率在 5 000 Hz 以上的高频信号时,陶瓷不响应,因此阻带起始频率  $\Omega_s$  为 5 000 Hz,阻带衰减  $\alpha_s$  为 30 dB。由式(3)可计算出巴特沃斯滤波器的阶数  $N$  为 1.88,向上取整后滤波器的阶数为 2。

查表后可得到 2 阶巴特沃斯低通滤波器的归一化 LPF 基准滤波器参数  $L_1=1.41421 \text{ H}$ ,  $C_1=1.41421 \text{ F}$ 。

因此本文所设计的电感值为:

$$L' = \frac{K \cdot L}{M} \quad (4)$$

电容值为:

$$C' = \frac{C}{M \cdot K} \quad (5)$$

其中  $M$  为待设计滤波器截止频率与基准滤波器截止频率的比值,  $K$  为待设计滤波器特征阻抗与基准滤波器特征阻抗的比值。由式(4)和式(5)计算出待设计的电感  $L'$  为 3 000  $\mu\text{H}$ , 电容  $C'$  为 0.2  $\mu\text{F}$ 。

### 2.3 MOSFET 驱动电路

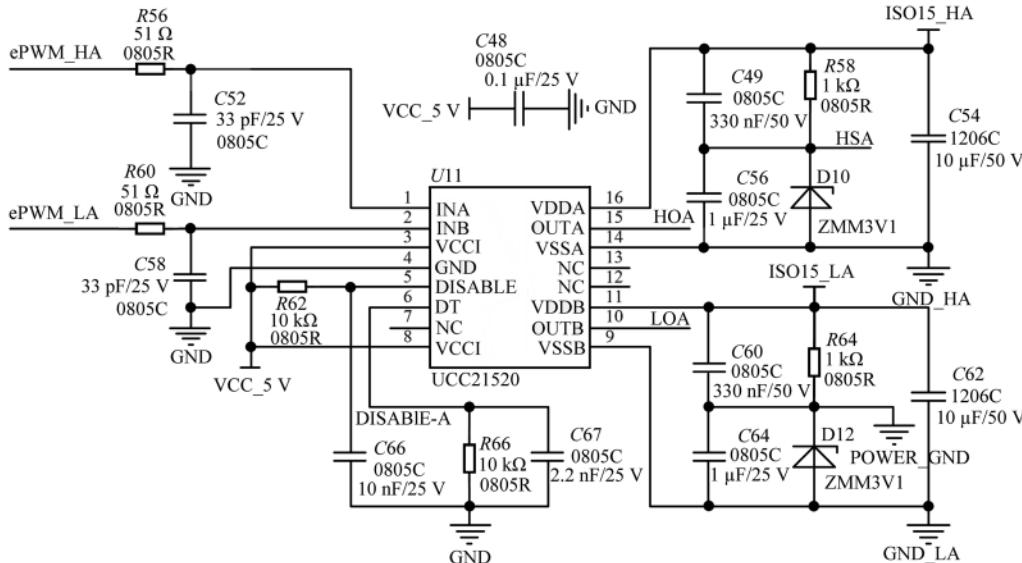

由于开关频率高,要求驱动电路具有更快的响应速度、更强的驱动能力并具有稳定性<sup>[9]</sup>,同时需要减少开关损耗<sup>[10]</sup>。设计采用了 UCC21520A 隔离式双通道栅极驱动器,尺寸小、功率密度大、具有增强隔离用于保护。其开关延迟仅有 19 ns,保证了控制信号的实时性,共模瞬态抗扰度的最小值为 100 V/ns,确保了高精度的控制半桥的开断。

PWM 信号输入设计了 RC 滤波器可以用来滤除由非理想布局或长 PCB 轨迹引入的干扰。禁用引脚在设为高电平时可同时关断两个输出,在悬空或接地时允许器件正常运行。作为一种故障安全机制,一次侧逻辑故障会强制两个输出为低电平,用于保护半桥逆变电路中的 MOSFET。由于寄生电感可能导致功率晶体管的门源驱动电压出现振荡现象,如果超过了阈值电压,就有可能误开启甚至出现击穿,因此在栅极驱动上加上齐纳二极管保证振荡低于阈值,从而保护半桥和驱动电路。

### 2.4 采样电路

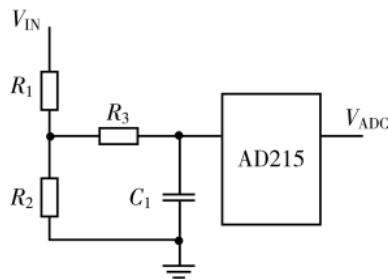

为了使压电陶瓷在不同频率下,能够稳定输出 100 倍增益的电压,系统采用了电压闭环控制的方式,采用反馈采样电路获取输出电压,电路如图 4 所示。其中  $R_1$  和  $R_2$  采用精密电阻构成了分压电阻<sup>[11]</sup>,将压电陶瓷驱动电源输出两端的电压缩小 100 倍,得到模数转换芯片能够采集的电压信号,同时为了减少分压过后电压信号的纹波干扰,需要对分压后的电压进行滤波,由于输出

图 3 MOSFET 驱动电路

图 4 反馈采样电路

的频率在 10 Hz~800 Hz, 因此采用  $R_3$  和  $C_1$  构成了低通滤波器对分压后的电压进行滤波, 为保证隔离采样的精度, 这里选用了 ADI 公司的 AD215 线性隔离运放, 该芯片具有  $\pm 10$  V 的信号输入范围, 高输入阻抗, 且在 1 kHz 的时候具有  $-80$  dB 的低谐波失真。最终通过 18 位高精度的 A/D 采样芯片将 AD215 输出的隔离采样电压  $V_{ADC}$  转换为数字信号到 FPGA。

### 3 FPGA 控制算法设计

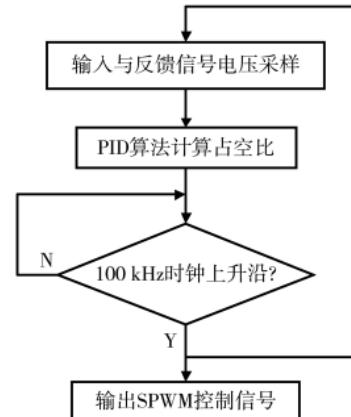

为保证压电陶瓷驱动电源具有高精度、稳定的驱动性能, 在系统中引入了电压闭环控制<sup>[12]</sup>, 以载波频率为单周期的控制方式调节驱动电源的输出电压, 其控制框图如图 5 所示。FPGA<sup>[14]</sup>驱动 18 位 A/D 采样芯片在  $T_0$  时刻对输入电压信号  $AD_1$  和反馈电压信号  $AD_2$  进行采样, FPGA 可以在一个采样周期中同时对输入和输出信号进行采集, 减少了反馈信号与原信号的相位差, 也提高了系统对数据处理的速度。系统将计算其偏差和偏差的变化, 将这两个参数代入 PID 算法中计算得到输出的占空比  $D$ , 等待下一个  $T_1$  时刻到来后, 立刻输出占空比  $D$  到 MOSFET 驱动器, 然后重复  $T_0$  时刻的步骤。

输出占空比  $D$  的计算:

$$D = P \cdot [e(i) - e(i-1)] + I \cdot e(i) + \frac{AD_1}{M} \cdot \frac{AD_1}{2^{18}} \quad (6)$$

图 5 FPGA 控制框图

其中  $P$  为比例参数,  $I$  为积分参数,  $e(i)$  为当前输入电压信号与反馈电压信号的误差(即  $e(i) = \frac{F}{M} \cdot \frac{AD_1 - AD_2}{2^{18}}$ ),  $F$  为 FPGA 中 SPWM 生成模块的主频频率,  $M$  为载波频率,  $AD_1$  为输入电压信号。

其中 PID 控制算法<sup>[15]</sup>中的核心参数是让闭环控制稳定的关键, 如果采用不断地实验去调节参数, 工作量将十分巨大, 因此需要先确定开关频率为 100 kHz, PID 的计算也按此频率进行, 确保系统稳定运行, 使用数学公式解算出 PID 控制参数, 在此参数基础上, 进行试验对参数进行微调, 使其达到预期的效果。

### 4 仿真与实验测试

通过 Simulink 仿真软件平台对本设计的压电陶瓷驱动电路进行仿真, 先采用理论计算的参数和模型进行仿真, 再根据仿真的结果对参数进行细微调整后, 仿真得到适合的参数, 输出波形也达到预期效果, 并做了一台输出功率可达 1 kW、输入信号带宽为 10 Hz~800 Hz、增益 100 倍的压电陶瓷驱动电源, 并对静态容值为 5  $\mu$ F

的压电陶瓷进行各项性能测试。

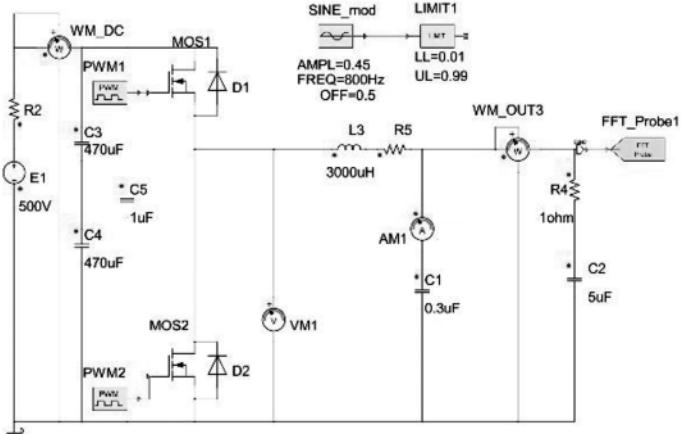

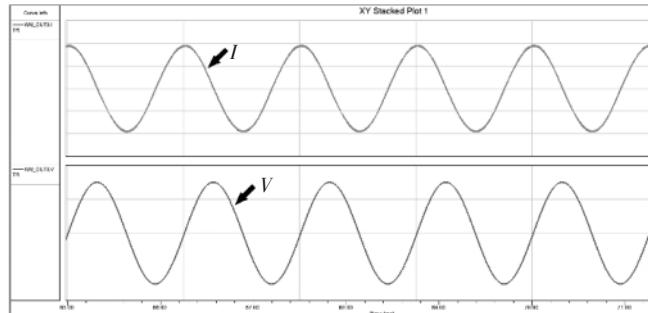

#### 4.1 电路仿真

为了验证驱动电源的稳定性和精确性,对压电陶瓷驱动电路进行仿真分析,仿真电路如图 6 所示,其仿真结果如图 7 所示。

图 6 压电陶瓷驱动仿真电路

图 7 仿真驱动波形

该仿真电路的输入电压  $E_1=500\text{ V}$ , MOS1 和 MOS2 分别为半桥电路的上桥臂和下桥臂, 其开关频率为 100 kHz, 控制信号为互补 SPWM 信号, 死区时间为 100 ns, 输出电感  $L_1=3\text{ }000\text{ }\mu\text{H}$ , 电容  $C_1=0.2\text{ }\mu\text{F}$ , 负载为与压电陶瓷等效容值为 5 μF 的电容。

在仿真电路中, 输入信号幅值为 0~5 V、频率为 800 Hz 的正弦信号, 其输出波形如图 7 所示, 第一个为电流输出波形, 第二个为电压输出波形, 其幅值为 498 V, 输出增益约为 100 倍。

#### 4.2 驱动能力测试

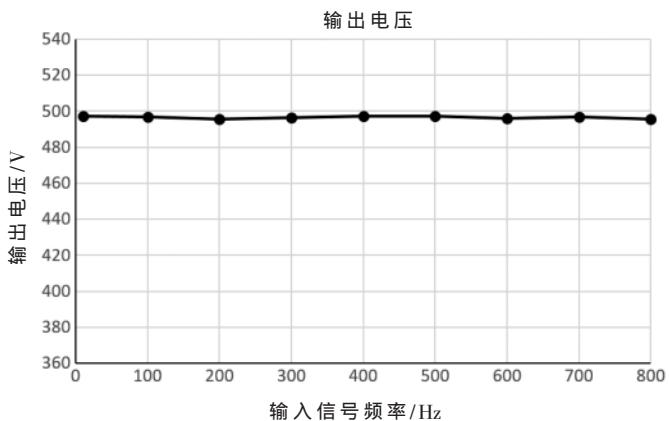

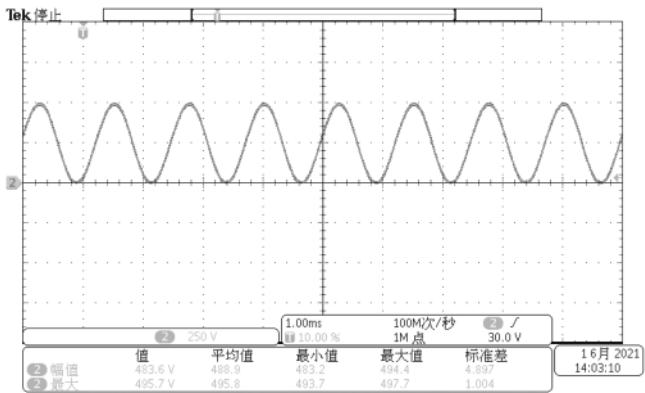

测试条件为: AC-DC 电源输出设置为 500 V, 输入信号为 0~5 V 正弦信号, 为测试不同频率下的驱动能力, 将输入信号频率分别设定为 10 Hz~800 Hz 中 9 个频点进行输出能力的测试, 通过示波器得到不同频率下压电陶瓷驱动电源输出的电压、电流波形。如图 8 所示, 在输入信号为 10 Hz~800 Hz 的条件下, 输出电压稳定在 500 V 左右, 在各频率下的输出电压没有明显的波动, 该压电陶瓷驱动电源输出稳定, 输出能力强。

图 9 为输入 800 Hz 的小信号时驱动电源的输出波

图 8 频段内电压输出实验数据

图 9 输入信号 800 Hz 时驱动电源输出波形图

形, 输出电压最大值为 495.7 V, 电压输出经过巴特沃斯滤波器滤波之后, 电压波形平滑、纹波小、没有畸变, 实现了电压输出的高精度控制。

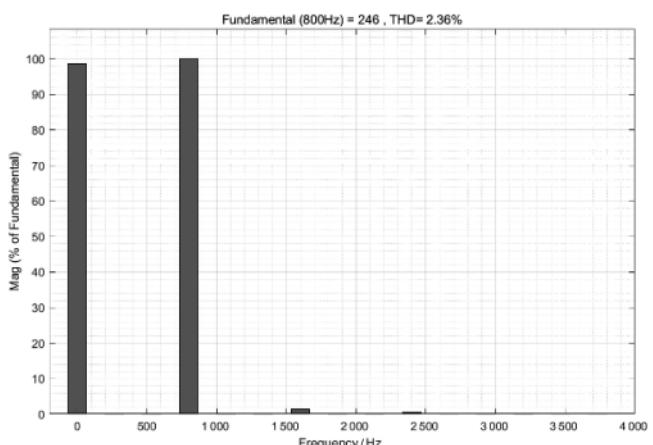

对 800 Hz 下的输出波形进行 FFT 分析, 输入信号为含有 2.5 V 的直流分量、频率为 800 Hz、幅值为 5 V 的交流信号, 分析结果如图 10 所示, 可以看出直流信号和 800 Hz 信号的基波幅值的比例接近 100%, 800 Hz 的基波幅值为 246, THD(畸变率)为 2.36%, 结果表明, 电压输出波形由直流分量和 800 Hz 组成, 其他频率的信号幅

图 10 输出波形的 FFT 分析

值接近于0,输出波形畸变很小。

表1为负载 $C_L=5\mu F$ ,输入信号为0~5V、800Hz时压电陶瓷驱动电源实验数据表。由此表可知,在不同输入电压下,驱动电源的实际输出与理论输出相差无几,输出增益能稳定在99以上,电压输出纹波只有几十毫伏,可以看出压电陶瓷驱动电源输出增益稳定,驱动能力强,性能稳定可靠。

表1 压电陶瓷驱动电源实验数据

| 理论输出/V | 实际输出/V | 误差/V | 增益    | 输出纹波/mV |

|--------|--------|------|-------|---------|

| 100    | 99.2   | 0.8  | 99.2  | 23      |

| 200    | 198.7  | 1.7  | 99.35 | 25      |

| 300    | 298.2  | 1.8  | 99.4  | 22      |

| 400    | 397.4  | 2.6  | 99.35 | 30      |

| 500    | 495.7  | 4.3  | 99.14 | 31      |

## 5 结论

本文提出了一种基于FPGA的大功率高精度压电陶瓷数字驱动电源的设计方案,电路中采用巴特沃斯低通滤波器设计,并使用以FPGA作为运算核心的单周期PID控制算法,提高了系统的稳定性、精确性和驱动能力。根据仿真和测试结果可以得到以下结论:

(1) 经过理论分析和实际测试后,可以看出该驱动电源在10Hz~800Hz的频率范围内驱动压电陶瓷等效容值为5μF电容时,压电陶瓷驱动电源的输出电压保持稳定,输出功率高。

(2) 根据FFT分析结果和测试数据,可知压电陶瓷驱动电源的输出电压增益稳定、误差小,电压波形畸变小、纹波低,满足叠堆型压电陶瓷的驱动需求。

## 参考文献

- [1] 靳宏,金龙,徐志科,等.压电叠堆位移放大致动器的动态特性[J].振动与冲击,2012,31(21):146~151.

- [2] 郭珂,金龙,徐志科,等.叠层型压电驱动器技术及实验

(上接第38页)

- 下头部姿态估计[J].传感技术学报,2021,34(1):57~63.

- [13] 刘建国,纪郭,颜伏伍,等.基于视差优化的立体匹配网络[J].计算机工程,2022,48(3):220~228.

(收稿日期:2021-05-12)

研究[J].微电机,2008(5):80~82.

- [3] 王盼,张威.电压驱动型开关式压电陶瓷驱动电源的设计[J].科技视界,2020(5):75~78.

- [4] 天津科技大学.一种基于FPGA的超声导波压电陶瓷驱动电源:CN201910400243.7[P].2019-08-06.

- [5] 苏宇隆.电压型逆变电路控制方法的分析[J].电气传动自动化,2020,42(1):15~17,11.

- [6] 赵晓群,张洁.巴特沃斯低通滤波器的实现方法研究[J].大连民族学院学报,2013,15(1):72~75.

- [7] 朱思浩,罗显志.可配置八阶巴特沃斯低通滤波器的设计[J].湖北大学学报(自然科学版),2021,43(3):276~281.

- [8] 汪其锐,王桂华,王永军.巴特沃斯数字低通滤波器设计及应用[J].山东工业技术,2016(24):251.

- [9] 阎治安,赵发明,冯宝文,等.一种功率MOSFET半桥驱动电路设计[J].防爆电机,2016,51(1):22~25.

- [10] 卢乙,李先允,王书征,等.改善SiC MOSFET开关特性的有源驱动电路研究[J].电气传动,2021,51(16):21~26.

- [11] 王震,董健年,张军.一种用于高压测试的电阻分压器研究[J].科学技术与工程,2016,16(7):60~64,99.

- [12] 宋崇辉,徐涛,王振环,等.单相逆变电源电压双闭环矢量控制方法[J].电工技术学报,2019,34(16):3386~3395.

- [13] 胡域,朱玉玉.一种高压压电陶瓷驱动电源的设计[J].压电与声光,2020,42(1):71~76.

- [14] 李显亮,李明鑫,吴定祥,等.基于ARM和FPGA超声波压电陶瓷数字变频驱动[J].单片机与嵌入式系统应用,2018,18(7):59~64.

- [15] 左顺文,苏晋涛,宋仕涛.Buck电路电流闭环的控制设计与仿真[J].电子制作,2021(17):16~19.

(收稿日期:2021-09-11)

## 作者简介

康玉宽(1989-),通信作者,男,硕士,讲师,主要研究方向:机械电子,E-mail:1173021032@qq.com。

扫码下载电子文档

## 作者简介

杨戈(1974-),男,博士,副教授,主要研究方向:人工智能技术、计算机视觉技术。

王震尧(1999-),男,本科,主要研究方向:计算机视觉、双目立体视觉技术。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所