# 先进工艺芯片填充冗余金属后的时序偏差分析及修复

王秋实, 孟少鹏, 吴宏强

(安徽芯纪元科技有限公司, 安徽 合肥 230031)

**摘要:** 在芯片物理设计的完成阶段,为了满足设计规则中金属密度要求,需要填充冗余金属。增加的金属层会产生额外的寄生电容,导致芯片的时序结果恶化。40 nm 以上的工艺节点中,这些额外增加的寄生电容对于时序的影响在 0.12% 左右,这个时序偏差甚至比静态时序分析与 SPICE 仿真之间的误差还小,在芯片设计时通常忽略它。然而在使用 FinFET 结构的先进工艺节点中,这个时序偏差必须要进行修复。以一款 FinFET 结构工艺的工业级 DSP 芯片为实例,使用 QRC 工具对比了芯片填充冗余金属前后寄生电容的变化;使用 Tempus 工具分析了芯片时序结果发生偏差的原因;最后提出了一种基于 Innovus 平台的时序偏差修复方法,时序结果通过签核验证,有效提高了时序收敛的效率。

**关键词:** 先进工艺; 物理设计; 冗余金属; 寄生电容; 时序修复

中图分类号: TN47

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.212353

中文引用格式: 王秋实, 孟少鹏, 吴宏强. 先进工艺芯片填充冗余金属后的时序偏差分析及修复[J]. 电子技术应用, 2022, 48(6): 42–44, 49.

英文引用格式: Wang Qiushi, Meng Shaopeng, Wu Hongqiang. Analysis and repair of timing deviation caused by filling dummy metal in advanced process chip[J]. Application of Electronic Technique, 2022, 48(6): 42–44, 49.

## Analysis and repair of timing deviation caused by filling dummy metal in advanced process chip

Wang Qiushi, Meng Shaopeng, Wu Hongqiang

(Anhui Silieepoch Technology Co., Ltd., Hefei 230031, China)

**Abstract:** In the finish stage of the chip physical design, in order to meet the metal density design rules, dummy metal fill needs to be added. The dummy metal fill generates external parasitic capacitances, which will deteriorate chip timing results. In process nodes above 40 nm, timing deviation caused by these external parasitic capacitances is about 0.12%, even smaller than the mismatch between STA and SPICE simulation, we usually ignore it. However, this timing deviation must be repaired in advanced process nodes with FinFET structure. Taking a industrial DSP process chip with FinFET structure as an example, this paper uses QRC to compare the parasitic capacitance changes before and after adding dummy metal fill; uses Tempus to analyze the reasons for the timing deviation of the chip; finally proposes a method for repairing timing deviation based on Innovus, the timing result is verified by signoff. This method effectively improves the efficiency of timing closure.

**Key words:** advanced process node; physical design; dummy metal fill; parasitic capacitance; timing repair

## 0 引言

冗余金属填充是一种可制造性设计(Design For Manufacturing, DFM)手段,目的是为了减小芯片制造过程中化学机械抛光(Chemical Mechanical Polishing, CMP)带来的工艺偏差,提高芯片的成品率<sup>[1-2]</sup>。在金属互连线平坦化过程中,同时包含了化学作用和机械作用<sup>[3]</sup>,金属和介质材料本身的研磨速率不同以及金属密度的不均匀就会造成金属层的高低起伏,可能导致互连线短路、断路等异常结果,从而导致整个芯片失效<sup>[4]</sup>。由于 CMP 工艺对图形密度极为敏感,业界通过添加冗余金属图形使芯

片各个位置的金属密度均匀分布,以改善平坦化效果<sup>[5]</sup>。

在先进工艺中,版图的密度梯度对芯片可制造性的影响越来越突出,因此在冗余金属填充过程中不仅需要考虑密度约束,也需要同时考虑密度梯度以及密度均匀性问题<sup>[6]</sup>。在工艺进入 FinFET 时代后,冗余金属填充还需要满足双曝光工艺的特点,即所有的冗余金属图形需要均匀地被拆分到两张不同的掩膜版上<sup>[7-8]</sup>。

在完成设计的时序、功耗和功能收敛后,芯片的物理设计流程进入 DFM 阶段<sup>[9]</sup>。此时的版图中不论金属密度还是图形线宽都不均匀,无法保证晶圆表面的平坦

性。此时,可以通过自动布局布线工具、物理验证工具以及工程师手工添加等手段实现冗余金属的填充。填充有两种形式:浮空填充和接地填充。大部分设计采用的都是浮空填充,只在金属低密度区填充冗余金属,不连接地,不占用布线资源,相对接地填充,有易实现的优点<sup>[10]</sup>。

冗余金属在改善芯片良率的同时,也会恶化已经收敛的时序结果。互连线和填充的冗余金属之间相互耦合,产生额外的寄生电容,增大信号线的延迟<sup>[11]</sup>。由于此时的版图已接近固化,为了保证整体的设计周期,完成投片,必须有一种行之有效的时序修复方法。本文从工程实践的角度出发,以本公司中一款使用 12 nm 工艺设计的工业级 DSP 芯片(芯片代号 WhiteWhale01)为实例,系统地分析 12 nm 工艺下冗余金属对时序结果产生影响的原因,并提出了一种时序偏差修复方法。

## 1 冗余金属填充

在 12 nm 工艺的后端物理设计流程中,通过自动布局布线工具填充的冗余金属无法通过设计规则的检查,必须使用代工厂提供的自动填充包(Auto-fill utilities)结合物理验证工具填充冗余金属。填充过程将整个设计分成一个个窗格(如 50 μm×50 μm),然后计算每个窗格中图形密度,最后根据相邻窗格的图形密度决定冗余金属的填充量<sup>[12]</sup>。窗格式的填充,通过循环算法来使得填充的冗余金属量最小,同时各个相邻窗格之间的密度梯度差也最小<sup>[13]</sup>。

12 nm 工艺的冗余金属包括不需要光学邻近效应修正(Optical Proximity Correction, OPC)<sup>[14-15]</sup>修正的 DMn(n 代表不同的金属层)以及需要 OPC 修正的 DMn\_O。对于需要双曝光的金属层,DMn 和 DMn\_O 还需要区分成不同的 color。与此同时,该工艺也要求必须插入冗余的通孔 DVIA<sub>n</sub>(n 代表不同的通孔层),以连接上下相邻的冗余金属层。

使用物理验证工具 PVS 对 WhiteWhale01 芯片完后自动填充后,冗余金属类型如表 1 所示。每种冗余金属包含 6 个参数:Width/Length 是指冗余金属的长度和宽度;Run/End Space 分别指在宽度方向和长度方向冗余金属图形的间距;Run/End Offset 分别指在宽度方向和长度方向相邻冗余金属图形之间的偏移量。

填充的冗余通孔类型如表 2 所示,每种冗余通孔只包含宽度和间距两个参数。

## 2 冗余金属的影响

对完成冗余金属填充的 WhiteWhale01 芯片重新进行完整的寄生参数提取,再读入新的寄生参数进行静态时序分析,对比时序报告发现内核主频从 1.5 GHz 退化到 1.2 GHz,性能下降 20%,这个时序偏差显然无法接受。

本节从填充冗余金属前后寄生参数的变化和路径延迟的变化两个方面,分析 WhiteWhale01 芯片发生时序偏差的原因。

表 1 WhiteWhale01 芯片中的填充的冗余金属

(μm)

| 冗余金属     | Width/Length | Run/End Space | Run/End Offset |

|----------|--------------|---------------|----------------|

| DMx_B    | 0.106/1.16   | 0.106/0.12    | 0/0            |

| DMx_S    | 0.106/0.3    | 0.106/0.12    | 0.053/0.21     |

| DMx_O    | 0.06/0.24    | 0.08/0.09     | 0/0.165        |

| DMxa_B   | 0.106/1.16   | 0.106/0.12    | 0/0            |

| DMxa_S   | 0.106/0.3    | 0.106/0.12    | 0.053/0.21     |

| DMxa_O   | 0.06/0.24    | 0.08/0.09     | 0/0.165        |

| DMxd_B   | 0.106/1.16   | 0.106/0.12    | 0/0            |

| DMxd_S   | 0.108/0.45   | 0.108/0.108   | 0.054/0.279    |

| DMxd_O_R | 0.06/0.3     | 0.08/0.12     | 0/0            |

| DMxd_O_R | 0.12/0.24    | 0.12/0.12     | 0/0            |

| DMxe_B   | 0.106/1.16   | 0.106/0.12    | 0/0            |

| DMxe_S   | 0.108/0.45   | 0.108/0.108   | 0.054/0.279    |

| DMxe_O_R | 0.06/0.3     | 0.08/0.12     | 0/0            |

| DMxe_O_R | 0.12/0.24    | 0.12/0.12     | 0/0            |

| DMy_M    | 0.27/1.8     | 0.27/0.45     | 0.068/0.113    |

| DMy_S    | 0.18/0.9     | 0.27/0.36     | 0.068/0.09     |

| DMy_O    | 0.09/0.244   | 0.09/0.09     | 0.023/0.023    |

| DMr_B    | 1.8/1.8      | 0.8/0.8       | 0.18/0.18      |

| DMr_M    | 1.2/1.2      | 0.8/0.8       | 0.18/0.18      |

| DMr_S    | 0.8/1.8      | 0.8/0.8       | 0.18/0.18      |

表 2 WhiteWhale01 芯片中的填充的冗余通孔

(μm)

| 冗余通孔                       | Width | Space |

|----------------------------|-------|-------|

| DVIAx/DVIAxa/DVIAxd/DVIAxe | 0.09  | 0.334 |

| DVIAy                      | 0.106 | 0.18  |

### 2.1 寄生参数的变化

在温度 125 °C、RC Corner 为 cworst\_CCworst\_T 条件下,使用 QRC 工具分别对填充冗余金属前后的全芯片进行寄生参数提取,使用 Ostrich 工具对全芯片中约 302 万条互连线的寄生参数进行对比。

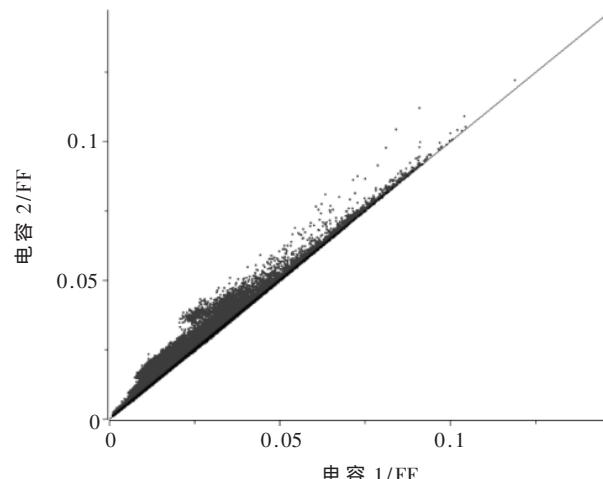

互连线寄生电容的变化结果如图 1 所示。图 1 中,

图 1 WhiteWhale01 芯片寄生电容的变化

大部分互连线处于中心斜线的上方,说明其寄生电容都有一定程度的增大。互连线的寄生电容增大的比例越大,在图1中越是远离中心斜线。统计发现,总体的寄生电容增加在3%,部分互连线寄生电容的增加甚至会达到70%~100%。

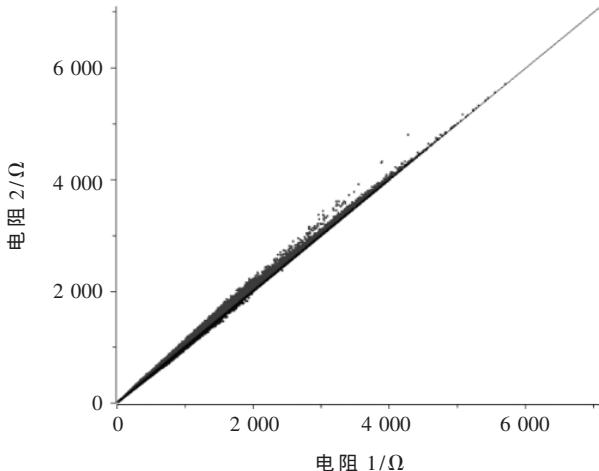

互连线寄生电阻的变化结果如图2所示。图2中,互连线基本分布在中心斜线的附近,说明其寄生电阻的变化很小,统计发现,总体的平均偏差在0.2%以内,标准偏差在0.7%以内。

图2 WhiteWhale01芯片寄生电阻的变化

寄生参数对比的结果表明,WhiteWhale01芯片中填充的浮空冗余金属对信号线的电阻没有影响,只会恶化寄生电容。

## 2.2 路径延迟的变化

在Library PVT为SSGNP/0.72v/125C条件下,使用Tempus工具对建立时间slack变化较大的5000条时序路径逐条对比分析发现,路径延迟的变化主要集中在两个方面:

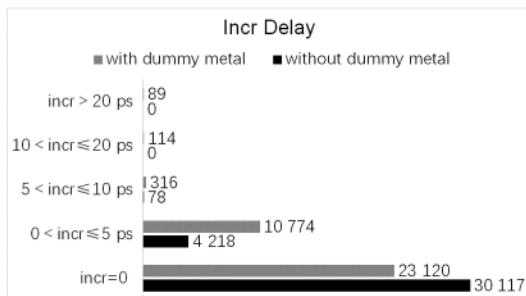

(1)串扰延时增大,体现在时序报告中Incr Delay增大。图3为填充冗余金属前后时序报告中34 413条数据信号线Incr Delay数值对比,20.3%的信号线串扰延时明显增大。分析表明,由于浮空填充的冗余金属使不同信号线之间的耦合电容增大,加剧了串扰,导致信号完整性问题。

图3 时序路径中Incr Delay的变化

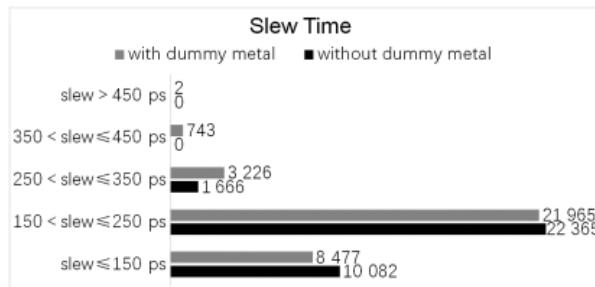

(2)信号转换时间增大,体现在时序报告中Slew增大。图4为填充冗余金属前后数据信号线Slew Time数值对比,745条信号线甚至出现了max transition(350 ps)违例。分析表明,由于寄生电容增加使标准单元的负载增大,导致信号的转换时间增大,进一步导致路径中下一级标准单元的延迟增大。

图4 时序路径中Slew Time的变化

路径延迟分析的结果表明,串扰延时和单元新增延迟相互叠加,在时序路径上产生时序违例,严重破坏WhiteWhale01芯片的时序性能。

## 3 时序偏差修复方法

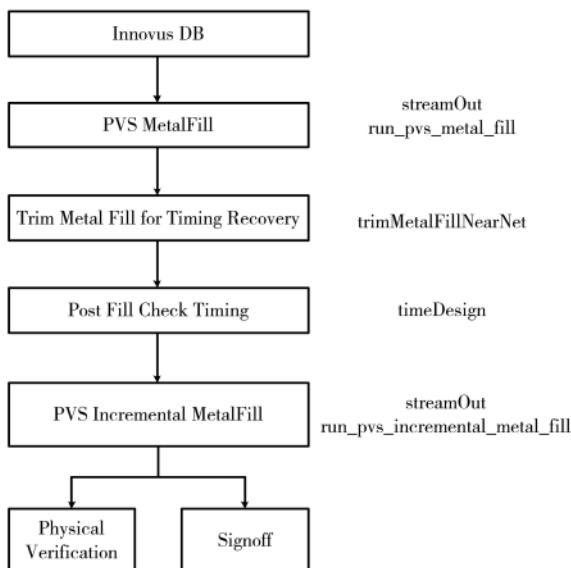

基于以上的分析,本文提出一种基于Innovus平台的时序偏差修复方法,该修复方法不需要对设计进行功能上的改动,只对添加的冗余金属进行修剪,拉大关键路径上信号线与冗余金属的缓冲距离,减小相应的寄生电容。具体分为5个步骤:

(1)在完成功能设计及时序收敛的database基础上,使用Innovus调用PVS引擎,进行signoff级别的冗余金属填充。

(2)分析冗余金属对时序结果的影响,修剪时序发生变化的互连线周围的冗余金属。可以通过参数控制修剪互连线同层、上层或者下层的冗余金属,也可以控制修剪的间距范围。

(3)查看修复效果。如果时序结果无法接受,改变相应参数并重复步骤(2)。

(4)调用PVS引擎进行增量冗余金属填充。

(5)进行最终的物理验证及签核验证。

该修复方法的流程及所用到的命令如图5所示。

WhiteWhale01芯片使用该修复方法不同阶段的时序结果对比如表3所示(注:MF=metal fill)。从表中可以看出,使用该修复方法后,全新的时序结果基本恢复到未填充冗余金属的状态。

## 4 结论

先进工艺芯片填充冗余金属后引起时序偏差是物理设计流程中不可避免的难题。本文通过对12 nm工艺填充的冗余金属进行研究分析,发现串扰延时和信号转换时间增大是恶化时序的关键原因;并提出一种快速高

(下转第49页)

- [9] 柯洋.柔性膜卷绕纠偏控制机理与算法研究[D].武汉:华中科技大学,2017.

- [10] 惠先刚.带式输送机全自动纠偏系统研究[D].秦皇岛:燕山大学,2018.

- [11] 孙智娟.自动纠偏控制系统的设计与开发[J].机械工程与自动化,2010(4):138-140.

- [12] 赵松善,宗绍中,毕磊,等.纠偏系统在轮胎成型机中的应用[J].轮胎工业,2015,35(10):629-631.

- [13] 姚敏.数字图像处理[M].北京:机械工业出版社,2006.

- [14] 张棣,赵建新,梅梦瑶,等.自动纠偏控制系统设计[J].

(上接第44页)

图5 时序偏差修复流程图及所用命令

表3 WhiteWhale01芯片不同阶段的时序结果对比

|                 | Without MF | With MF | Trim MF |

|-----------------|------------|---------|---------|

| WNS/ns          | -0.005     | -0.164  | -0.007  |

| TNS/ns          | -0.332     | 207.181 | -0.446  |

| Violating Paths | 272        | 5 041   | 288     |

效的时序偏差修复方法,时序结果对比证明了该方法的有效性。

本文提出的时序修复方法在单独的 Innovus 平台即可实现,迭代速度快,时间开销小,能够很方便地应用到其它芯片设计项目当中。

#### 参考文献

- [1] 代永平,耿卫东,孙钟林,等.CMP平坦化技术在LCoS显示器中的应用[J].光电子技术,2003(1):41-45.

- [2] 王延鹏.基于边界元法的矩形冗余填充耦合电容提取方法[D].西安:西安电子科技大学,2012.

- [3] 姜霖.化学机械研磨(CMP)对电特性影响的分析与优化[D].上海:复旦大学,2011.

- [4] SURYADEVARA B.Advances in Chemical Mechanical Pla-

山东工业技术,2019(11):163.

(收稿日期:2021-09-09)

#### 作者简介:

苏铭(1996-),通信作者,男,硕士研究生,主要研究方向:机器视觉,E-mail:2677073937@qq.com。

范文强(1965-),男,硕士生导师,副教授,主要研究方向:机器视觉。

肖东(1993-),男,硕士研究生,主要研究方向:机器视觉。

扫码下载电子文档

- narization(CMP)[M].Cambridge:Woodhead Publishing,2016.

- [5] CHEN Y, KAHNG A, ROBINS G, et al. Area fill synthesis for uniform layout density[J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2002, 21(10): 1132-1147.

- [6] 文鼎童.纳米时代基于CMP平坦化工艺的可制造性研究[D].北京:中国科学院微电子研究所,2009.

- [7] 李金鑫.双曝光工艺中冗余金属填充的物理实现[D].西安:西安电子科技大学,2019.

- [8] 张芸.双重图形技术在后端设计中的解决方案[D].上海:复旦大学,2013.

- [9] 史峰.亚波长光刻条件下集成电路可制造性设计与验证技术研究[D].杭州:浙江大学,2005.

- [10] 张尤磊.一种优化的冗余金属填充方法研究[D].上海:上海交通大学,2019.

- [11] 杨飞.冗余金属填充对电特性的影响研究[D].合肥:合肥工业大学,2010.

- [12] WILSON R. Why chip designers need to know about CMP modeling: Mentor's Calibre SmartFill [EB/OL]. (2009-03-18)[2021-11-18].https://www.edn.com/electronics-blogs/practical-chip-design/4309111/Why-chip-designers-need-to-know-about-CMP-modeling-Mentor-s-Calibre-Smart-Fill.

- [13] ELKADER A S, LARSEN C M. Model-based fill: US 862-1402 B2[P]. 2013-12-31.

- [14] 朱忠华.版图光刻工艺热点快速检测及修复技术研究[D].上海:上海交通大学,2016.

- [15] 刘娟.先进节点逻辑集成电路光学临近效应修正中工艺窗口提高研究[D].上海:上海交通大学,2016.

(收稿日期:2021-11-18)

#### 作者简介:

王秋实(1989-),男,硕士研究生,高级工程师,主要研究方向:SoC芯片后端物理设计。

孟少鹏(1982-),男,硕士研究生,正高级工程师,主要研究方向:SoC芯片后端物理设计。

吴宏强(1989-),男,硕士研究生,工程师,主要研究方向:SoC芯片后端物理设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所