# 基于 PCIe Gen5 的低成本 Coupon 设计

刘 涛, 宗艳艳, 王乾辉, 秦玉倩, 田民政, 余华国

(浪潮电子信息产业股份有限公司, 山东 济南 250101)

**摘要:** 数字技术发展日新月异, 新一代服务器产品中, PCIe Gen5 信号速率已经达到 32 Gb/s, 为了确保其信号完整性设计, 单板损耗监控必不可少, 优良的 Coupon 设计因此显得尤为重要。传统 Coupon 多采用 Litek 探头技术, 以折线方式布线, 尽管技术成熟, 但存在占用空间大, 数据稳定性差等问题。从产品设计的低成本需求出发, 对 PCIe Gen5 信号的低成本 Coupon 设计展开研究, 结合差分绕线理论分析以及仿真数据, 对几种不同绕线方式进行分析对比, 选择了一种低空间占有率且高可靠性的 Coupon 布线方式, 并对测试治具进行了改进。实验结果表明, 提出的 Coupon 设计方法不仅比传统方法占用空间少, 而且数据稳定性更高, 更加有利于 Coupon 的低成本、高可靠性设计。

**关键词:** PCIe; 32 Gb/s; Coupon; 相位差; 测试验证

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.211960

中文引用格式: 刘涛, 宗艳艳, 王乾辉, 等. 基于 PCIe Gen5 的低成本 Coupon 设计[J]. 电子技术应用, 2022, 48(6): 116–120.

英文引用格式: Liu Tao, Zong Yanyan, Wang Qianhui, et al. Low-cost Coupon design based on PCIe Gen5 signal[J]. Application of Electronic Technique, 2022, 48(6): 116–120.

## Low-cost Coupon design based on PCIe Gen5 signal

Liu Tao, Zong Yanyan, Wang Qianhui, Qin Yuqian, Tian Minzheng, Yu Huaguo

(Inspur Electronic Information Industry Co., Ltd., Jinan 250101, China)

**Abstract:** The development of digital technology is changing rapidly. In the new generation of server products, the PCIe Gen5 signal rate has reached 32 Gb/s. In order to ensure its signal integrity design, single-board loss monitoring is essential, and a good Coupon design is therefore particularly important. Traditional Coupons mostly use Litek probe technology, and wiring in a broken line. Although the technology is mature, there are still many problems such as large space occupation and poor data stability. Based on the low-cost requirements of product design, this paper researches on the low-cost Coupon design of PCIe Gen5 signal. Different wiring methods are analyzed and compared through theoretical analysis and simulation. Then the high-reliability Coupon wiring method is selected which can also takes up less space. The test fixture is also optimized which can also improve data stability. Experimental results show that the Coupon design method proposed in this paper not only takes up less space than traditional methods, but also has higher data stability. Therefore, this method is more conducive to the low-cost and high-reliability design of Coupons.

**Key words:** PCIe; 32 Gb/s; Coupon; phase difference; test verification

## 0 引言

互联网技术飞速发展, 万物高速互连早已成为不可逆转的发展趋势, 为了满足日益增长的数据存储、传输与交换需求, 信号速率也正在以前所未有的速度进行升级换代, 以服务器系统中代表性的 PCIe 总线为例, 信号经历了从第一代产品的 2.5 Gb/s 速率, 到如今主推的第五代 32 Gb/s 速率, 乃至即将发行的第六代 64 Gb/s 速率的飞速革新<sup>[1]</sup>。尽管速率提升可以有力推动数字技术发展, 却也带来了一系列的困难和挑战, 对于 SI 工程师来说, 如何在高度集成的复杂电子系统中保证高速信号质量, 完成信号完整性设计, 成为了越来越突出的重点问题。

所谓信号完整性设计, 就是要对引起高速信号失真的各种因素进行优化, 尽量减少信号失真, 保证其能准确传递信息。引起信号失真的因素主要包括信号网络之间产生的串扰问题, 以及信号自身传输媒介引起的反射和损耗问题<sup>[2]</sup>。因为传输路径存在等效串联和并联电阻, 信号在此媒介中传输时必然会有一定的能量损耗, 通常高频分量损耗比低频分量大, 导致了信号上升边退化现象, 引起符号间干扰(ISI)和眼图塌陷等一系列问题<sup>[3]</sup>。新一代服务器产品中, PCIe Gen5 信号速率高达 32 Gb/s, 损耗引起的上升边退化问题尤为严重, 必须进行优化设计。

板材优化是改善上述损耗问题的有效途径之一, 但损耗性能更好的板材必然会带来更高的研发成本, 因此

进行板材选择时,既要满足损耗指标要求,又要避免板材过优造成资源浪费,在这种裕量较小的情况下,须对板厂加工的PCB损耗进行监测<sup>[4]</sup>,避免因为工艺问题带来损耗波动,达不到损耗指标。

常用的PCB损耗测试技术包括频域法、有效带宽法、根脉冲能量法、短脉冲传播法和单端TDR差分插入损耗法五种<sup>[5]</sup>,无论使用哪种技术,都需要设计对应的loss测试Coupon,Coupon设计的好坏,例如其测试夹具和绕线方法等,都将会直接影响到监测准确度。AFR、Delta-L和SFD等都是常用的Coupon测试夹具<sup>[6]</sup>,其中Delta-L因具有操作简便、测试精度较高且能去嵌等优势,当前应用最为广泛,但此技术需要使用额外过孔,容易带来阻抗不连续问题,对此,Lee J等人提出了一种焊盘过孔镀覆(VIPPO)技术,可以最小化路径不连续性,有效提高Coupon测试精度<sup>[7]</sup>;针对高频下测试和去嵌引入误差大的问题,Hsu J等人从数据后处理角度进行优化,提出了一种ARO拟合数据平滑算法,使测试更具抗错性<sup>[8]</sup>;绕线方式同样影响测试准确度,Coupon条常以折线方式走线,但因为占用空间大,不利于产品低成本设计,如果为了节省空间进行绕线,对于差分信号而言又容易出现对内不等长问题,需要进行鼓包补偿,许志辉等人通过仿真对Accordion(手风琴)、Sawtooth(锯齿)和Trombone(长号)等不同鼓包方式进行了比较,发现手风琴结构为时序控制下最优的差分信号绕线方式<sup>[9]</sup>;WBWC<sup>[10]</sup>和ABD<sup>[11]</sup>等新型补偿方式还可以效降低走线EMI影响,是小空间绕线设计的优良选择。

本文重点对PCIe Gen5信号的低成本Coupon设计开展研究,结合理论分析、仿真数据,对不同绕线方式进行比较,选择了一种低空间占有率为时序控制下最优的差分信号绕线方式<sup>[9]</sup>;WBWC<sup>[10]</sup>和ABD<sup>[11]</sup>等新型补偿方式还可以效降低走线EMI影响,是小空间绕线设计的优良选择。

## 1 差分绕线理论分析

为了提高抗干扰能力,高速信号都采用差分传输线进行信号传输,如果两个单端信号分别为 $V_p$ 和 $V_n$ ,差分信号和共模信号可以分别表示为:

$$V_{\text{diff}} = V_p - V_n \quad (1)$$

$$V_{\text{comm}} = \frac{1}{2} (V_p + V_n) \quad (2)$$

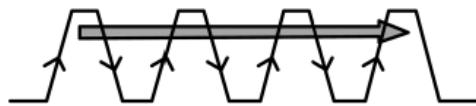

保持差分线对称设计是提高其抗干扰能力的关键<sup>[12]</sup>,传统Coupon设计中,为了减小玻纤效应<sup>[13]</sup>,以如图1所示的折线方式布线,尽管对称性良好,但因为占用空间大,不利于Coupon低成本设计,本文希望对其进行改进。

图1 传统折线布线方式

如果为了节省空间进行绕线,因为拐角等物理结构的存在,可能会造成差分对内不等长的问题。根据式(1)

和式(2),两条传输线中的信号也可以用差分和共模信号进行表示:

$$V_p = V_{\text{comm}} + \frac{1}{2} V_{\text{diff}} \quad (3)$$

$$V_n = V_{\text{comm}} - \frac{1}{2} V_{\text{diff}} \quad (4)$$

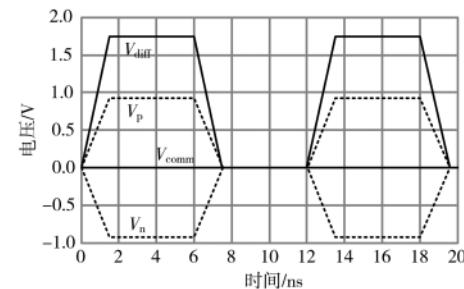

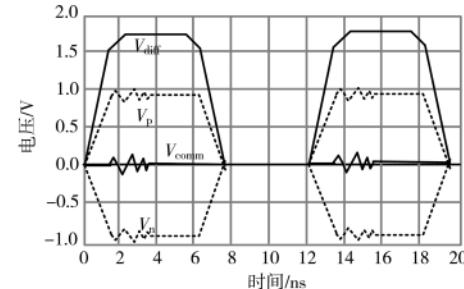

理想状况下,两条单端信号线完全对称,几种信号的相对关系如图2(a)所示,但如果出现差分对内不等长,电压波形则会如图2(b)所示出现波动,这是模态转换问题造成的<sup>[14-15]</sup>,不仅会使差分信号高频分量能量损失,出现信号上升边畸变,而且没有共模端接时,还会因为反射,产生图示的振铃效应。

(a)理想状况下的电压波形图

(b)走线不对称情况下的电压波形图

图2 差分共模信号与其单端信号电压波形图

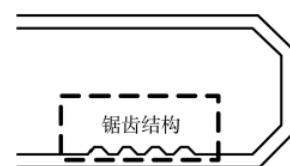

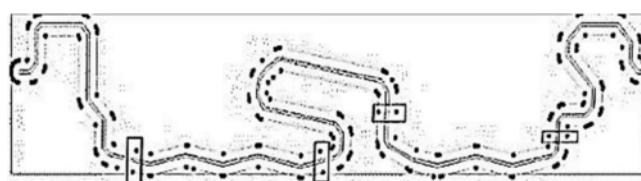

为了避免上述问题,常使用如图3所示锯齿结构,对长度较短的走线进行鼓包补偿处理,但从不对称产生位置,到补偿完成位置的中间过程,模态转换依旧存在,难以消除。

图3 锯齿补偿结构

同时,对于速率高达32Gb/s的PCIe 5.0信号,使用锯齿结构进行长度补偿时,在绕线部位,信号并不只会沿着传输线传输,如图4所示,还有一部分能量将沿绕线间的耦合电容直接传输,导致信号的等效传输长度减小,因此补偿过后 $V_p$ 和 $V_n$ 依旧存在相位差,且随着频率升高,相位差逐渐变大,如果在某一频点相位差累计到180°,信号将会出现谐振问题。

因此,为了进一步提高Coupon测试数据可靠性,本文希望在不使用锯齿结构情况下完成绕线对称性设计,

图 4 锯齿结构下的高频信号传输模式

这需要根据 Coupon 实际空间大小 , 对测试线长度进行调整 , 通过减小走线线长 , 使绕线有足够的空间及时改变拐角方向 , 快速抵消因拐角引起的对内错位 , 从而避免额外的锯齿补偿。

## 2 绕线方式仿真验证

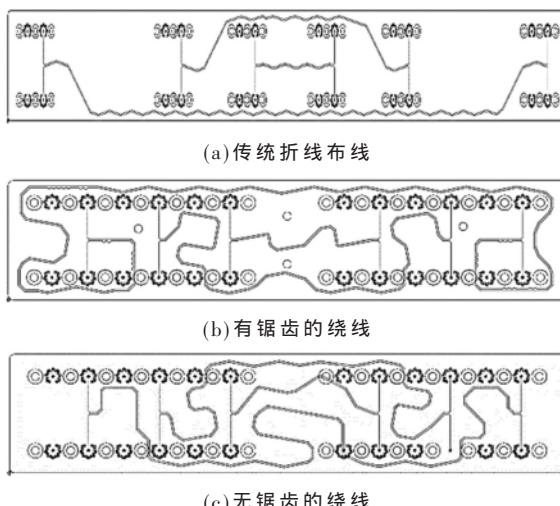

为了对比上述传统折线布线方式、带有锯齿的绕线方式以及没有锯齿的绕线方式 , 对几种绕线进行了 layout 设计 , 并使用 Cadence 公司 Clarity 3D 电磁场求解器对走线模型进行提取 , 通过仿真对比验证其信号质量。

图 5 所示为几种绕线下的 Coupon layout 设计图 , 表 1 列出了它们的一些基本信息 , 相对于图 5(a) 的传统折线方式 , 图 5(b) 和图 5(c) 通过绕线可以明显减小 Coupon 尺寸 , 按标准大料尺寸进行评估 , 两者的 SET 净利用率分别为 56.21% 和 72.56% , 进一步证实了绕线方式可以有效降低 Coupon 设计成本。三个 Coupon 采用统一叠层 , 统一线宽线距 , 且均在表层走线 , 图 5(a) 和图 5(b) 走线长度为 2/5/10 inch , 其中图 5(b) 的 10 inch 长走线存在锯齿结构 , 根据 Coupon 实际尺寸 , 将图 5(c) 的走线长度调整为 2/5/7 inch 。

使用 Clarity 软件对上述走线进行 S( 散射 ) 参数提取 ,

图 5 Coupon layout 设计图

表 1 Coupon 信息表

|       | 传统折线                   | 有锯齿绕线           | 无锯齿绕线 |

|-------|------------------------|-----------------|-------|

| 板材    | Very low loss material |                 |       |

| PP 厚度 | 2.7 mil                |                 |       |

| 线宽线距  | 5/8 mil                |                 |       |

| 走线线长  | 2/5/10 inch            | 2/5/7 inch      |       |

| 尺寸    | 25.29 cm×2.4 cm        | 11.19 cm×2.4 cm |       |

与现有的 3D 解决方案相比 , Clarity 基于分布式处理技术 , 提供近乎无限的求解容量和 10 倍以上的求解速度 , 能够充分利用多核计算机资源 , 在保证测量级精准度的同时 , 高效地解决庞大复杂的系统问题 , 在速度、容量以及测试精度方面都表现出了极大的优越性。因此 , 基于仿真效率及可靠性考虑 , 本文选择此软件进行不同绕线方式的模型提取。

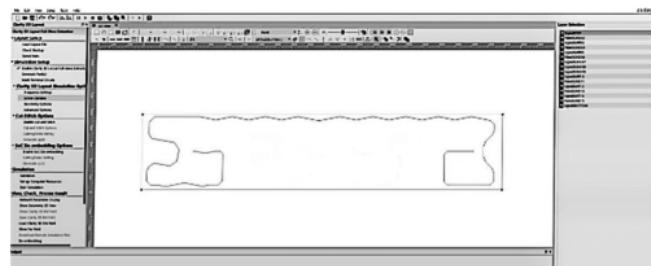

图 6 所示为导入了 PCB 文件之后的 Clarity 主界面。首先要对金属层 / 介质层材料、厚度、介电常数、损耗角、刻蚀角、粗糙度等叠层参数进行定义 , 随后对走线进行端口设置 , Clarity 当前设有 coaxial 和 vertical 两种模式端口 , 本文的走线选择 vertical(lump) 端口 , 并对端口尺寸、参考层等信息进行完善。

图 6 导入版图的 Clarity 主界面

接下来需要对待提取模型的走线进行边框剪切 , 如图 7 所示 , 边框尺寸由布线层与相邻介质层的间距决定。为了提高仿真效率 , 还可以通过 Cut & Stitch 模式对剪切框进行区域划分 , 根据区域内结构选择不同的 solver 。

图 7 Clarity 剪切框界面

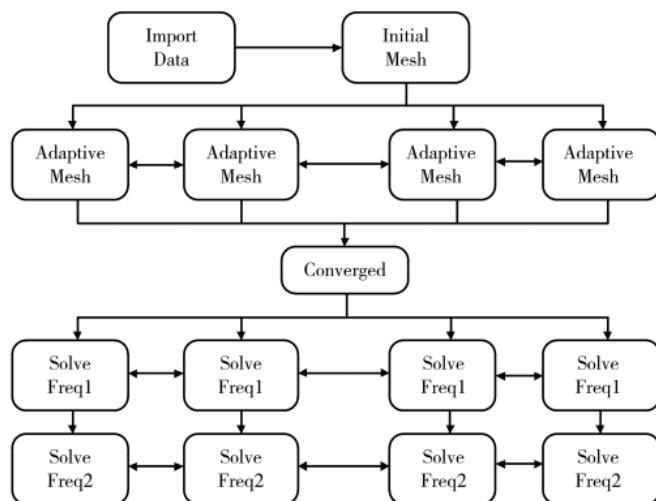

最后要对仿真频率、仿真引擎以及网格结构等仿真相关参数进行设置 , 确认设置无误后 , 即可提交仿真任务 , Clarity 将会基于分布式处理技术运行如下流程 , 先后进行结构的网格化处理和频率扫描计算 , 最终生成 S 参数模型。Clarity 分布式处理技术流程如图 8 所示。

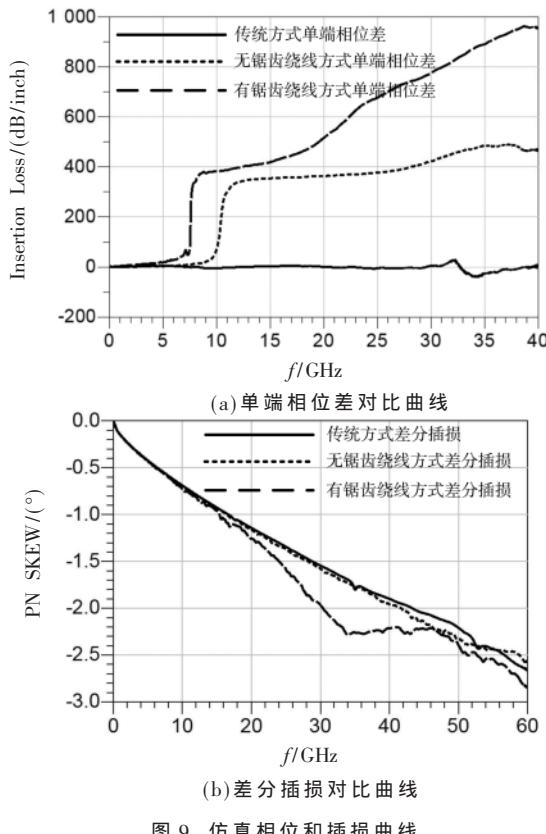

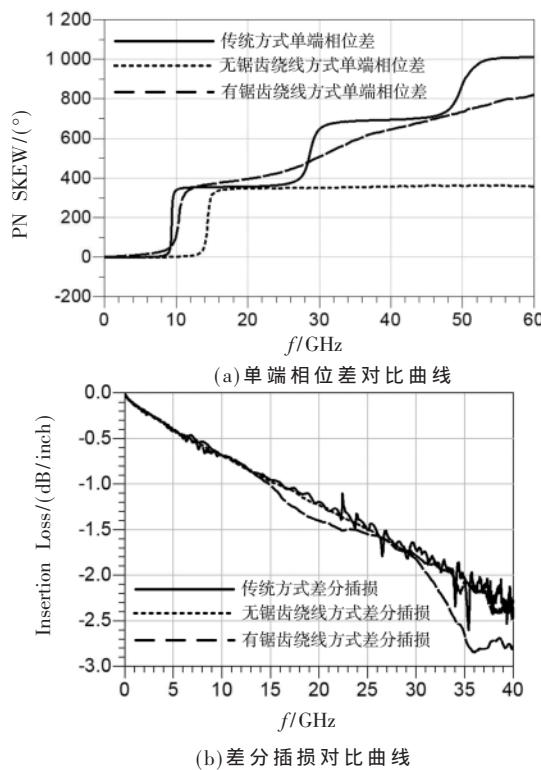

通过单端相位差和差分插损数据对比三种走线下的 PCIe Gen5 信号质量 , 最长走线的对比结果如图 9 所示。

图 9(a) 中 , 锯齿绕线方式最早在低频处出现相位差 , 随着频率升高 , 三种方式都会出现 360° 的相位差跳变 , 这是因为对应位置出现了单端信号的谐振 , 而没有锯齿结构的绕线下 , 谐振频点明显高于另外两种 , 说明此走线方式对单端信号谐振有一定优化作用。相位差跳变的频点处 , 对应到图 9(b) 图的插损曲线上 , 都会出现小的

图 8 Clarity 分布式处理技术流程图

图 9 仿真相位和插损曲线

谐振回沟,这是由于两个单端信号谐振程度不同导致的。

第一次相位差跳变之后,有锯齿结构的绕线下,相位差持续增大,到达 540°左右时,两个单端信号同相,导致在图 9(b)所示的插损曲线中出现了一个大的谐振点,说明锯齿结构在高频下的确不能有效实现长度补偿,本文提出的没有锯齿绕线方式则有效避免了这一问题。

### 3 测试结果与结论

基于上述理论分析和仿真数据,本文进一步通过测试验证方案的可行性和优越性。

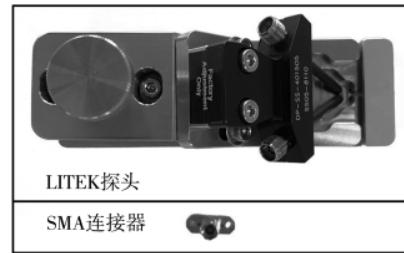

传统 Coupon 多使用如图 10 所示的 LITEK 探头,测

图 10 LITEK 探头和 SMA 连接器

试结果对操作手法的依赖性强,数据稳定性较差。本文创新性将此探头换成了 SMA 连接器,一方面 SMA 连接器可以更好地固定,测试数据的稳定性更高;另一方面,SMA 比 LITEK 探头的带宽更宽,更加适用于 PCIe Gen5 等高速信号的测试。

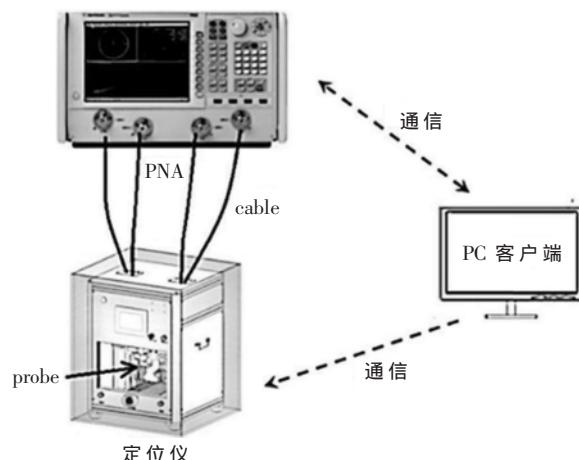

鉴于 SMA 连接器固定方式繁琐,本文为了提高测试效率,研发了一套如图 11 所示的自动化测试系统,将 SMA 连接器固定在可以移动的探头上,用机械臂替代螺丝固定连接器,可以有效避免反复安装拆卸工作。

图 11 基于 SMA 连接器的自动化 Coupon 测试系统

为了验证本文方案的优化效果,对传统的折线走线和 LITEK 探头的 Coupon,使用锯齿结构绕线和 SMA 连接器的 Coupon,以及没有锯齿结构绕线和 SMA 连接器的 Coupon 进行了测试,并对测试数据进行了治具去嵌,相位和插损结果如图 12 所示。

与仿真结果类似,三种方式中,使用锯齿结构的走线出现了谐振现象,而传统走线的 Coupon 因为使用了带宽窄的 LITEK 探头,数据的稳定性很差,在高频范围内抖动明显。综合来说,本文没有锯齿结构绕线并使用 SMA 连接器的方案,在减小 Coupon 尺寸,降低研发成本的同时,还可以有效提高数据稳定性,是一种可靠的低成本 Coupon 设计方案。

### 4 结论

本文提出了一种 PCIe Gen5 信号的低成本 Coupon 设计方案,分别通过理论分析、仿真数据对传统折线布

图 12 实测相位和插损曲线

线方式、带有锯齿结构的绕线方式以及没有锯齿结构的绕线方式进行对比验证,得出了没有锯齿结构的绕线方式比传统折线布线方式占用空间更小,比带有锯齿结构的绕线方式数据可靠性更高的结论。实验测试表明,设计 PCIe Gen5 信号 Coupon, 使用没有锯齿结构的绕线方式,在保证数据可靠性的前提下,比传统方法占用空间更少,数据稳定性更高,更加有利于 Coupon 的低成本,高可靠性设计。

#### 参考文献

- [1] 李实.从 1.0 到 6.0 的飞跃之路 PCIe 总线技术发展解析[J].微型计算机,2019(24):6.

- [2] Eric Bogatin,李玉山,刘洋.信号完整性与电源完整性分析[M].北京:电子工业出版社,2015.

- [3] 高斌,朱兴华,陈正清,等.PCB 信号完整性影响因素探讨[J].印制电路信息,2010(S1):512–523.

- [4] 刘丰,苏新虹,胡新星.PCB 信号完整性测试技术研究[J].

(上接第 115 页)

- [15] PUNZMANN H,FRANCOIS N,XIA H,et al.Generation and reversal of surface flows by propagating waves[J].Nature Physics,2014,10(9):658 – 663.

(收稿日期:2021-10-12)

#### 作者简介:

张新建(1980-),男,硕士,教授,主要研究方向:电磁

印制电路信息,2014(1):30–34.

- [5] 葛鹰,朱泳名.高频高速覆铜板介电性能项目的测试技术发展综述(下)——印制电路板高频插入损耗的测试技术现状分析[J].覆铜板资讯,2019(4):36–42.

- [6] 程柳军,李艳国,陈蓓.Delta L 损耗测试技术研究[J].印制电路信息,2018,26(z1):411–419.

- [7] HSU J,SU T,KAI X,et al.Printed circuit board insertion loss measurement metrology comparison[C]// Microsystems, Packaging, Assembly & Circuits Technology Conference.IEEE, 2015.

- [8] YE X,BALOGH M.Physics-based fitting to improve PCB loss measurement accuracy [C]// 2017 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity(EMCSI), 2017: 516–521.

- [9] 许志辉,冯立,汤茂林.时序同步下差分信号绕线方式的信号完整性研究[J].印制电路信息,2018,26(8):6–9.

- [10] FAN H,ZHOU X,BHOBE A U,et al.Localized skew compensation technique for reducing electromagnetic radiation : US2013 0118790A1[P], 2014.

- [11] LOU J,GARG J,BHOBE A,et al.Intra-pair length matching by asymmetric dual bend to reduce mode conversion[C]// 2020 IEEE International Symposium on Electromagnetic Compatibility & Signal/Power Integrity(EMCSI).IEEE, 2020.

- [12] 景芳,俞茂超.差分信号线的技术原理及设计要求[J].电讯工程,2007(1):10–13.

- [13] 陈蓓,程柳军,王红飞.玻纤效应对高速信号的影响[C]// 2015 中日电子电路秋季大会暨秋季国际 PCB 技术/信息论坛,2015.

- [14] 王锋.基于信号完整性差分信号等长绕线的研究[J].电脑迷,2018,112(11):173–175.

- [15] 经纬.不同差分传输线线形对信号完整性的影响[J].印制电路信息,2007(9):37–41.

(收稿日期:2021-07-19)

#### 作者简介:

刘涛(1983-),男,硕士,高级工程师,主要研究方向:服务器架构设计。

宗艳艳(1982-),通信作者,女,本科,工程师,主要研究方向:服务器架构设计。

王乾辉(1991-),男,本科,初级工程师,主要研究方向:信号完整性。

扫码下载电子文档

场、机器人技术等。

毕艳(1983-),女,硕士,副教授,主要研究方向:机械设计、有限元分析。

范娟(1978-),通信作者,女,硕士,副教授,主要研究方向:智能系统控制及优化技术,E-mail:jounko@qq.com。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所