# Yolo 神经网络在集成电路焊盘布局规则检测上的应用研究\*

林纯熙<sup>1</sup>,粟 涛<sup>2</sup>

(1.北京邮电大学 国际学院,北京 100001;2.中山大学 电子与信息工程学院,广东 广州 510006)

**摘要:**为探索深度学习在集成电路设计自动化上的应用,以电源和接地焊盘的排列规则作为检查案例,研究了 Yolo v3 神经网络在版图检查上的可行性。采用 Python 脚本批量生成版图样本图片,并使用 LabelImg 进行标签标记。使用 TensorFlow 框架编写了基于 Yolo v3 的版图检查器。结果显示,版图检查器在判断焊盘布局正确性上实现了高精确率与高召回率。此外,还通过调整版图的大小、形状、对称性与焊盘数目方式对检查器进行了进一步测试。检查器仍表现卓越,体现出良好的扩展性。研究表明 Yolo v3 可以很好地找出焊盘布局的错误。深度学习在集成电路版图检查中的潜力大,值得继续探索。

**关键词:**集成电路;电子设计自动化;版图检查;深度学习;神经网络

中图分类号: TN402

文献标识码: A

DOI:10.16157/j.issn.0258-7998.212288

中文引用格式:林纯熙,粟涛.Yolo 神经网络在集成电路焊盘布局规则检测上的应用研究[J].电子技术应用,2022,48(7):40-43,48.

英文引用格式:Lin Chunxi,Su Tao. Rule check of pad placement in IC layout with Yolo[J]. Application of Electronic Technique,2022,48(7):40-43,48.

## Rule check of pad placement in IC layout with Yolo

Lin Chunxi<sup>1</sup>, Su Tao<sup>2</sup>

(1. International College, Beijing University of Posts and Telecommunications, Beijing 100001, China;

2. School of Electronics and Information Engineering, Sun Yat-sen University, Guangzhou 510006, China)

**Abstract:** The application of deep learning on electronic design automation of integrated circuits is an interesting topic. This paper investigates the possibility of using Yolo v3 neural network to perform layout checks, which uses the arrangement rules between power and ground pads as inspection cases. In order to generate a training picture set, we use a custom Python script to generate layout sample pictures in batches and utilize LabelImg to label. The Yolo v3 layout checker is written under the TensorFlow framework. Evaluations demonstrate that the proposed layout checker achieves both high accuracy and high recall rate when judging the correctness of the pad layout. Additionally, the inspector is further tested by adjusting the size, shape, symmetry, and number of pads of the layout. Under such circumstances, the inspector still possesses an outstanding performance, showing great scalability. Our research reveals that the Yolo v3 neural network is able to find out errors in pad layout efficiently. Deep learning has great potential in integrated circuit layout inspection, which is worthy of further exploration.

**Key words:** integrated circuits; electronic design automation; layout check; deep learning; neural network

## 0 引言

从 2015 年以来,产业界研发了多种神经网络处理器<sup>[1-2]</sup>,并使用这些处理器制造了许多服务器,在多个城市大规模地部署了计算中心<sup>[3-5]</sup>。这些服务器具有强大的计算力。大量的个人携带的移动终端也嵌入了带神经网络处理器的芯片,形成一种随处可用的算力。如果这些算力也可以参与到集成电路的自动化设计中来,那会使设计工作变得更加方便。比如说,只需要下载相应的权值,就可以使用手机进行集成电路设计版图的检查,

这对管理人员也是一种帮助。

神经网络在图像分析上获得了巨大的成功。这些成功的案例有:目标分类<sup>[6-8]</sup>、目标检测<sup>[9-12]</sup>、目标识别<sup>[13-14]</sup>。除了单目标分析,神经网络还可以进行多目标分析<sup>[15-16]</sup>,比如在一张图中找到所有汽车<sup>[17]</sup>。然而当前成功的深度学习神经网络对于集成电路设计是否仍然有效,还有待研究。

集成电路设计分为前端和后端。后端的核心任务就是版图设计。版图设计分为绘制和检查两个环节。每次绘制完总要进行检查来判断绘制是否合规。芯片版图分为内核和 IO 两部分。首先探索神经网络是否可以用于

\* 基金项目:广东省科技项目(2019B010140002)

IO 焊盘摆放的合规性检查。

最近学术界在使用神经网络辅助集成电路设计上也开展了一些工作,主要有:采用 ANN 技术辅助微波电路设计<sup>[18]</sup>;利用人工神经网络设计、优化、模拟集成电路<sup>[19]</sup>;利用神经网络进行数字电路的分层测试<sup>[20]</sup>等。

上述这些工作存在诸多问题,并且也没有针对 IO 布局进行的研究。检查 IO 布局涉及目标的检测和识别,除了检测多个目标,还要分析目标之间关联,判断是否违规。此外还要对整个布局的态势做出分析。这种版图分析比人脸识别之类的分析要更加复杂,有可能带来一些对神经网络算法和应用的新认识。

综上所述,研究神经网络在 IO 布局上的应用有实际用途,与已有的工作不重复,并且具有一定的学术价值。

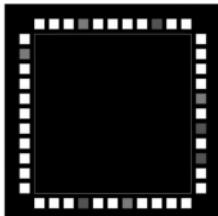

### 1 焊盘布局

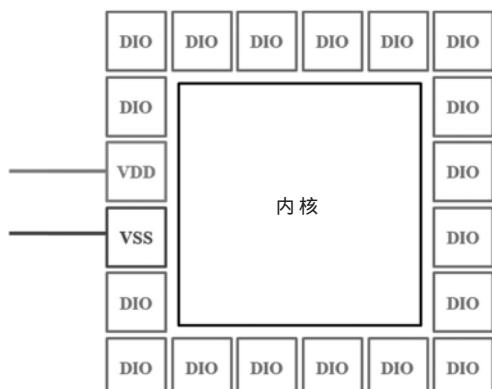

图 1 给出了一种芯片版图,IO 焊盘围绕内核排布。在这个布局中,电源引脚 VDD 和接地引脚 VSS 的焊盘被放在相邻的位置。这种布局的好处是,在封装和电路板上 VDD 和 VSS 的互连线可以紧紧靠在一起,既减少了供电网络的寄生电感,又能降低电源互连线上的电磁辐射,因此是有利的。

图 1 焊盘布局(有利)

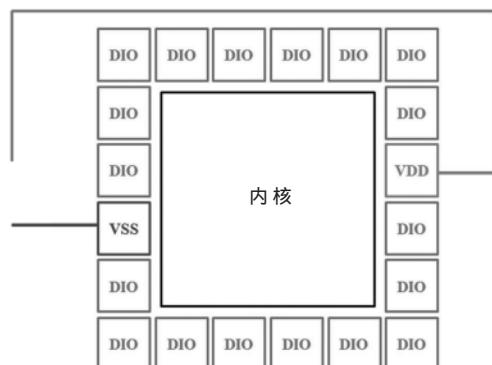

图 2 给出了一种不利的芯片版图。电源引脚 VDD 和接地引脚 VSS 的焊盘分别被放在两边。这种布局的电源网络连线会出现一个较大的环路,降低电源网络的快

图 2 焊盘布局(不利)

速响应能力,并导致较大的电磁辐射。

如果芯片版图中缺少 VDD 或 VSS 引脚,那很可能是一种错误,也是不能通过检查的。根据以上分析,确定本文要实现的检查目标为:给定芯片版图,分析 VDD 和 VSS 的相对位置,(1)如果两者相邻,就报正确;(2)如果两者不相邻,就报错误;(3)如果缺少其中一种或全部,也报错误。下面将验证神经网络是否能够完成这样的检测。

### 2 检测算法

深度卷积神经网络的模型有很多,其中用于目标检测并进入实用的主要有 Faster R-CNN、SSD 和 Yolo<sup>[21]</sup>。本文采用 Yolo 的 v3 版本<sup>[22]</sup>进行版图检查。

Yolo v1 是 Redmon 等人针对两阶段网络效率低、实时性差的问题提出的首个单阶段目标检测网络。即只需要对输入图像进行一次处理,即可同时得到目标位置和类别的优化网络,相比于其他几种目标检测算法,主要有目标检测速度快、背景错误少、泛化性能好等优点。

Yolo v3 在小目标的检测上表现出了比 Yolo v1 更卓越的性能。同时,在目标框位置检测和物体定位方面也更精确、更稳定。在检测速度方面,Yolo v3 仅用 1/3 的时间就可以达到与 SSD 相当的精度。Yolo v3 在边界框大小的预测上采用与 Yolo v2 相同的 K 均值聚类算法,最终从预测出的三个初始尺寸不一的边界框中选出与真实值的 IOU 最大的边界框来预测该目标。因此,在同尺寸的样本检测中,Yolo v3 生成的边界框大小几乎一致,并且更加接近于目标物的真实大小。Yolo v3 用 bx、by、bw、bh 表示预测得到的边界框的中心坐标和尺寸。

综合考虑,选用 Yolo v3 为本研究的目标检测算法。

### 3 实验部署

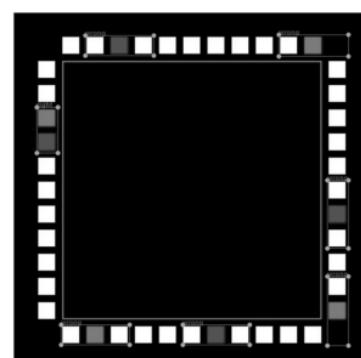

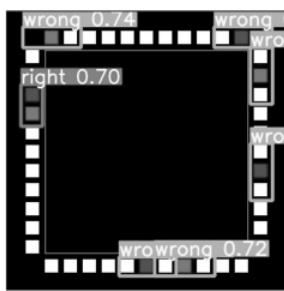

以 44 个引脚的布局为实验用例,见图 3。首先利用自编写的 Python 脚本生成了 100 张样本图片,随后运用 LabelImg 对其进行了标签标记并生成数据集。用 Python 生成版图框架,而后生成四组数字 0~10 的随机排布序列,并据数列确定 VSS 和 VDD 在每条边上的位置序号,随后生成样本图片。

将目标划分为两个大类:“right”和“wrong”。对于在

图 3 标记后的图形数据

同一条边上相邻的 VDD 与 VSS , 将其框住并将标签命名为 right; 对于不符合排布规范的 VDD 和 VSS 焊盘, 将其与左右相邻的普通焊盘或同极性焊盘一并框起并令标签名为 “wrong”。

数据集制作完成后, 利用 Python 脚本将其按照 90 : 9 : 1 的比例随机分成训练集、测试集和验证集三部分, 同时利用脚本获取每个部分的文件名与地址。完成以上数据的收集后, 将 Yolo v3 文件中的默认类别数量与名称悉数改为本次实验中的相关参数。至此, 第一次训练前的准备工作已全部完成。

调用训练器对训练集进行了训练。经过梯度下降算法的两百次迭代, 生成最佳权重文件 weight1.pt。然后调用版图检查器对权重进行测试。

为了测试版图检查器的泛化能力, 又制作了三组数据集。取消了每边一对极性焊盘的限制, 并分别改变了版图的整体大小、版图大小、形状与焊盘形状、间隔以及版图的倾斜角度, 随机生成了一批版图, 见图 4, 称为异形样本。

(a) 整体缩小

(b) 整体放大

(c) 版图大小、形状与焊盘形状、间隔改变

(d) 版图倾斜角度改变

图 4 非标准图形数据示例

对异形样本的测试集进行了测试, 然后针对测试中所暴露的弱点进行三次再训练。四次训练的特点和获得的权值如表 1 所示。

表 1 权值的标号

| 训练    | 数据集         | 得到权值       |

|-------|-------------|------------|

| 第一次训练 | 标准样本        | weight1.pt |

| 第二次训练 | 异形样本, 同比缩放  | weight2.pt |

| 第三次训练 | 异形样本, 不规则矩形 | weight3.pt |

| 第四次训练 | 异形样本, 倾斜版图  | weight4.pt |

## 4 实验结果

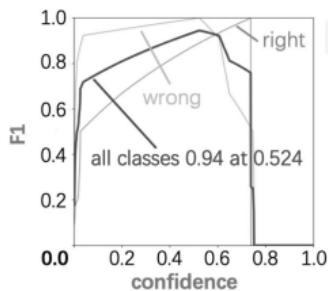

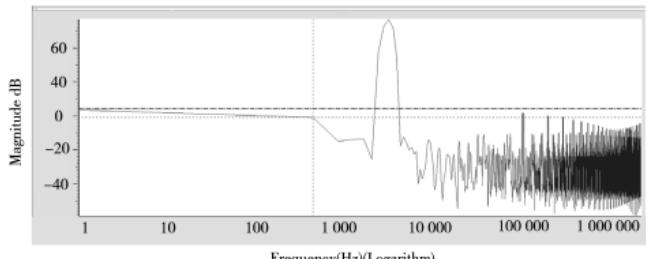

首先使用权值 weight1.pt 针对 100 张与训练集规格完全相同的测试图片进行了测试。实验结果如图 5、图 6

图 5 第一次训练后的 F1 曲线

图 6 同类样本检测效果图

所示。当置信度位于 0.02(约)至 0.75(约)区间内, 召回率与准确率的平均效果值(以下简称为“F1 值”)从约 0.70 近线性上升至最大值 0.94(置信度 0.524), 随后于最大置信度(约 0.75)处达到下降至约 0.75。

测试完成后在 “detect” 目录下生成了一个包含测试后图片的文件夹。结果显示, 该轮检测精确率达到 100%, 召回率也在 99% 以上。由此可见, 在同类样本的检测方面, 该版图检查器展现出了卓越的性能。

第二轮实验考查检测器的原始泛化能力, 仍然使用权值 weight1.pt 对异形样本进行测试, 结果如图 7 和表 2 (第一次)所示。版图检查器对于等比缩小样本的检测精度低, 对于间隙改变、角度改变的查全率较低。同时, 由于生成异形样本时取消了一边一对极性焊盘的限制, 对于同极性相邻的情况, 检查器将其误识别为正确样本。版图检查器针对异形样本的精确率与召回率都不高。

(a) 整体缩小

(b) 整体放大

(c) 版图大小、形状与焊盘形状、间隔改变

(d) 版图倾斜角度改变

图 7 第一次训练后的异形样本检测结果

第三轮实验中, 加入同比缩放的样本进行训练, 得到 weight2.pt 后, 再对异形样本测试, 结果如表 2(第二次)所示。检查器对于小尺寸目标的检测性能得到大幅提升。在本轮检测中, 小目标的边界框与实物更加贴合, 检测精度上升。对于宽、窄间隙的识别也更加精准。同时由于新数据集中焊盘的排布取消了限制, 该轮检测中同极

表 2 版图检查器对各类样本的检测效果总表

| 训练           | 测试集   | 精确率      | 召回率      |

|--------------|-------|----------|----------|

| 第一次(weight1) | 同形样本  | 1.000 00 | 0.994 64 |

|              | 整体缩小  | 0.829 79 | 0.590 91 |

|              | 整体放大  | 0.969 70 | 0.901 41 |

|              | 不规则矩形 | 0.854 17 | 0.494 00 |

| 第二次(weight2) | 倾斜版图  | 0.000 00 | 0.000 00 |

|              | 整体缩小  | 0.901 64 | 0.859 38 |

|              | 整体放大  | 0.921 05 | 0.989 52 |

|              | 不规则矩形 | 0.914 90 | 0.966 29 |

| 第三次(weight3) | 倾斜版图  | 0.923 08 | 0.808 99 |

|              | 整体缩小  | 0.984 38 | 0.900 00 |

|              | 整体放大  | 1.000 00 | 0.876 54 |

|              | 不规则矩形 | 0.975 31 | 0.963 41 |

| 第四次(weight4) | 倾斜版图  | 0.925 93 | 0.903 61 |

|              | 整体缩小  | 0.954 55 | 0.887 32 |

|              | 整体放大  | 0.930 56 | 0.930 56 |

|              | 不规则矩形 | 0.940 48 | 0.951 81 |

|              | 倾斜版图  | 1.000 00 | 0.964 29 |

性相邻判定错误的问题得到了解决。

第四轮实验中,加入版图大小、形状与焊盘形状、间隔改变的数据集进行训练,得到 weight3.pt 后,再对异形样本测试,结果如表 2(第三次)所示。检查器对于小目标边框的锚定得到了进一步优化。同时对于不规则矩形焊盘与宽度不规范的间隙有了更高的识别精度。对于倾斜摆放的版图样本,召回率已达到 90%以上。但由于尚未针对这一样本进行训练,边界框的框定不规范,精确率不佳。

第五轮实验中,加入版图倾斜的数据集进行训练,得到 weight4.pt 后,再对异形样本测试,结果如表 2(第四次)所示。版图检查器的泛化性能得到进一步提升。针对异形测试集,版图检查器的精确度达到预期。同时,由于泛化能力的提升,在小目标的检测上边界框贴合度有所下降。至此,该版图检查器针对同、异形样本的检测精度已全部达标。

经过四轮针对异形样本的实验,可以看出一些规律。随着训练样本的逐渐丰富,该版图检查器对于任一类型样本的检测精度与边界框贴合程度逐步平均,提示该版图检查器的泛化能力能够随训练提升。同时,检查器对于最近结束训练的样本表现出更优越、更稳定的检测性能。

如表 3 所示,版图检查器的最大 F1 值在前三次训练中由 0.94 单调升至 1.00,在第四次训练后降至 0.92。同时最大 F1 值所对应的置信度在第二次训练时达到最大值 0.641,而后于第四次训练后单调下降至 0.363。

前三次训练方向基本一致,重点关注提升检查器对于小样本、不规则形状、不规则间隙的检测精度。而第四轮训练的样本则需要更普适、包容性更强的标记方式。因此,在第四次训练后检查器的对于各类样本的检测效果趋于平均,对于同类样本以及不倾斜异形样本的检测效果相较第二、三次训练后有所下降。同时,经过修正训练,版图检查

表 3 各轮训练后版图检查器的综合性能总表

| 训练  | 测试集 | 最大 F1 值 | 对应置信度 |

|-----|-----|---------|-------|

| 第一次 | 异形  | 0.94    | 0.524 |

| 第二次 | 异形  | 0.99    | 0.641 |

| 第三次 | 异形  | 1.00    | 0.577 |

| 第四次 | 异形  | 0.91    | 0.363 |

器对于焊盘排布规则的改变表现出了较强的适应能力。

## 5 结论

目标检测算法 Yolo v3 在芯片版图焊盘排列规则的检测上表现出了优异的性能。在规整的版图样本和不规整的版图样本上都得到很高的精确率与召回率。展示出很强的泛化能力和适用能力。

集成电路版图的布局须遵循一定的规则。本次研究表明,通过训练深度神经网络在集成电路版图检查方面有很大潜力,值得持续的探索与挖掘。

## 参考文献

- [1] 张心怡.全球首个开源神经网络处理器指令集架构发布[N].中国电子报,2021-07-20(008).

- [2] 陈泳豪,萧嘉乐,粟涛.MobileNetV2 神经网络处理器的设计方案比较[J].计算机工程与科学,2021,43(1):24-32.

- [3] 南京智能计算中心正式投运[J].中国集成电路,2021,30(8):41.

- [4] 丁宜.国家信息中心单志广:智能计算中心建设要坚持需求导向[N].机电商报,2021-08-09(A03).

- [5] 赵广立.AI 计算中心建设急需一剂“普惠”良方[N].中国科学报,2021-08-27(004).

- [6] 陈亚宇,孙骥晟,李建龙,等.基于深度学习与图像处理的废弃物分类与定位方法[J].科学技术与工程,2021,21(21):8970-8975.

- [7] 陈琳.基于深度学习的 SAR 图像目标识别与分类[D].济南:山东大学,2021.

- [8] 袁哲明,袁鸿杰,言雨璇,等.基于深度学习的轻量化田间昆虫识别及分类模型[J].吉林大学学报(工学版),2021,51(3):1131-1139.

- [9] 王新娇.卷积神经网络结构设计及其在目标检测中的应用[D].桂林:广西师范大学,2021.

- [10] 黄真亮,张继顺,朱志武,等.目标检测算法在嵌入式平台中的应用[J].电子技术,2021,50(8):150-151.

- [11] 王红梅,王晓鸽,王晓燕.基于深度学习的复杂背景下目标检测研究[J/OL].控制与决策:1-8[2021-09-05].https://doi.org/10.13195/j.kzyjc.2021.0686.

- [12] 何文其,李剑,赵文浩.基于改进 FasterRCNN 的绝缘子异常检测[J].浙江电力,2021,40(8):40-46.

- [13] 李林,黄志华,张晶福,等.基于深度学习的 SAR 目标识别技术研究[J].长江信息通信,2021,34(7):6-10.

- [14] 何伟鑫,邓建球,刘爱东,等.基于改进 YOLOV3 算法的弹库目标识别方法研究[J].现代电子技术,2021,44(13):

(下转第 48 页)

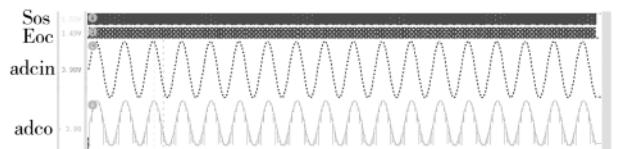

(a) A/D 转换后的正弦

(b) FFT 结果

图 10 正弦波仿真

表 1 性能比较

|                      | 文献[7] | 文献[12] | 文献[6] | 文献[11] | 本文   |

|----------------------|-------|--------|-------|--------|------|

| 电源/V                 | 2.8   | NA     | 3.3   | 1.8    | 4    |

| 分辨率/bit              | 10    | 16     | 12    | 10     | 10   |

| Samp/(kS/s)          | 116   | 1000   | 1000  | 240    | 1000 |

| SNDR/dB              | 61.9  | NA     | 68.4  | NA     | 58   |

| 有效位/bit              | 9.9   | NA     | 10.7  | 8.2    | 9.5  |

| 功耗/mW                | 1     | 11     | 2     | 35.5   | 8    |

| FOM/dB               | NA    | 127    | 300   | 95     | 136  |

| Area/mm <sup>2</sup> | NA    | 6.5    | 0.3   | 0.1    | 0.2  |

| Process/nm           | 180   | 250    | 180   | 180    | 130  |

## 参考文献

- [1] 黄宏斌,牟云飞.逐次逼近主要结构分析[J].电子测试,2019(7):47–48.

- [2] 荆苏丹,吴朝烨.逐次逼近模数转换器专利技术分析[J].河南科技,2017,605(2):37–38.

- (上接第 43 页)

- 1–6.

- [15] 肖思昌,靳经,潘敏,等.基于机器学习的多类目标识别方法分析[J].中国设备工程,2021(16):24–25.

- [16] 韩健鸿.基于深度信息融合的遥感图像多类目标辨识技术[D].北京:北方工业大学,2021.

- [17] 老翌.基于深度学习的车辆检测与识别算法研究[D].哈尔滨:哈尔滨理工大学,2021.

- [18] 杨思樱.神经网络在微波电路计算机辅助设计中的应用研究[D].成都:西南交通大学,2009.

- [19] JAFARI A,SADRI S,ZEKRI M.Design optimization of analog integrated circuits by using artificial neural networks[C]//2010 International Conference of Soft Computing and Pattern Recognition,2010:385–388.

- [3] 陈宏铭,许升睿,曾玉光.一种电容阵列结构的 10 位 8 通道 1MS/S 逐次逼近 AD 转换器[J].中国集成电路,2013(10):28–35.

- [4] 王也,刘力源,吴南健.一种 20 MS/s 基于 VCO 比较器的二阶噪声整形 SAR ADC 设计[J].信息技术与网络安全,2021,40(6):62–68.

- [5] 佟星元.R-C 型逐次逼近 ADC D/A 转换网络功耗模型与仿真[J].系统仿真学报,2016,28(4):946–950.

- [6] 黄玲,姜岩峰,鞠家欣,等.一种 12bit CMOS 全差分 SAR ADC[J].电子世界,2014(9):20–21.

- [7] 车来晟,唐鹤,高昂,等.一款 10 位逐次逼近型模数转换器设计[J].电子与封装,2019(7):16–19.

- [8] 廖方云,王绩伟,谷京儒,等.一种提高 SAR ADC 的 D/A 转换精度的方法[J].微电子学,2019,49(5):598–601,608.

- [9] 乔峻石,李冬梅.基于开关运放的低功耗逐次逼近 ADC 设计[J].半导体技术,2008(3):252–256.

- [10] Hong Hui,Li Shiliang,Zhou Tao.Design of a low power 10 bit 300 ksps multi-channel SAR ADC for wireless sensor network applications[J].Journal of Semiconductors,2015(4):158–164

- [11] TSAI S J,CHEN Y C,HSIEH C C,et al.A column-parallel SA ADC with linearity calibration for CMOS imagers[J].IEEE Sensors,2012:1–4

- [12] ZHONG L,YANG H,ZHANG C.Design of an embedded CMOS CR SAR ADC for low power applications in bio-sensor SOC[C]//7th International Conference on ASIC,2007.

(收稿日期:2021-10-16)

## 作者简介:

邓玉清(1983-),通信作者,女,硕士,高级工程师,主要研究方向:数模混合集成电路设计,E-mail:dengyuqing321@163.com。

牛洪军(1987-),男,硕士,工程师,主要研究方向:数模混合集成电路设计。

扫码下载电子文档

- [20] PAH Z.Hierarchical test generation using neural networks for digital circuits[C]//International Conference on Neural Networks and Signal Processing,2003,2003:245–248.

- [21] 赵永强,饶元,董世鹏,等.深度学习目标检测方法综述[J].中国图象图形学报,2020,25(4):629–654.

- [22] REDMON J,FARHADI A.Yolov3:an incremental improvement[EB/OL].[2019-06-20].<https://arxiv.org/pdf/1804.02767.pdf>.

(收稿日期:2021-11-02)

## 作者简介:

林纯熙(2001-),本科,主要研究方向:通信工程和机器学习、深度学习等。

粟涛(1977-),副教授,主要研究方向:数字集成电路设计与集成电路电磁干扰分析。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所