# C-R型多通道 10 bit SAR-ADC 设计

邓玉清<sup>1</sup>,牛洪军<sup>2</sup>

(1.中科芯集成电路有限公司,江苏 无锡 214035;2.无锡翼盟电子科技有限公司,江苏 无锡 214035)

**摘要:**采用0.13 μm工艺,设计并实现了一款单端CR型分级的10 bit SAR-ADC。在设计中,CR型分级的采用显著降低了芯片面积,高5位的温度计码控制有效消除时钟馈通等误差,自举开关的设计提高了采样精度,前置放大器的高精度静态比较器有效降低失调、提升了转换精度。设计的ADC内核尺寸为580 μm×290 μm,后仿真结果显示,在采样率1 MS/s下,输入正弦信号200 kHz时,ENOB可达9.5位,EO=1 LSB。

**关键词:**模数转换;温度计码;CR逐次逼近;静态放大器;自举开关

中图分类号: TN432

文献标识码: A

DOI:10.16157/j.issn.0258-7998.212235

中文引用格式: 邓玉清,牛洪军. C-R型多通道 10 bit SAR-ADC 设计[J]. 电子技术应用, 2022, 48(7): 44–48.

英文引用格式: Deng Yuqing, Niu Hongjun. A design of 10 bit C-R multi-channel SAR-ADC[J]. Application of Electronic Technique, 2022, 48(7): 44–48.

## A design of 10 bit C-R multi-channel SAR-ADC

Deng Yuqing<sup>1</sup>, Niu Hongjun<sup>2</sup>

(1.China Key System & Integrated Circuit Co.,Ltd., Wuxi 214035 ,China ;

2.Wuxi Imeng Electronic Technology Co.,Ltd., Wuxi 214035 ,China)

**Abstract:** This paper presents a design and implementation of a multi 10-bit successive approximation register analog-to-digital converter(ADC) with a 0.13 μm technology. A C-R DAC optimization technique is utilized in proposed design to reduce the area of ADC. Using thermometer codes to reduces harmonic distortions due to clock feedthrough. Using bootstrapped switch to improve sampling accuracy. The comparator is designed using static architecture with preamplifiers to eliminate offset. The chip is 580 μm×290 μm. The post simulation show that with an sampling ratio of 1 MS/s, 200 kHz signal, the ENOB is 9.5 bit and EO=1 LSB.

**Key words:** analog-digital conversion; thermometer code; C-R successive approximation; static amplifier; bootstrap switch

## 0 引言

Flash A/D转换器满足高速高精度,可以实现GS/s的水平,主要用于军工设计,例如雷达、卫星通信等<sup>[1]</sup>。ΣΔA/D转换器满足低速高精度,主要用于音频领域。流水线A/D转换器满足高速高精度,可以实现500 MS/s水平,主要应用于高速仪表、视频领域、网络系统。积分型A/D转换器满足中等速度中等精度,主要用于低速仪表。逐次逼近ADC(SAR ADC)满足中等速度中等精度,并且具有功耗低、面积小、复杂度低、易于集成SoC等优势,被广泛应用在数据采集、工业控制<sup>[1-2]</sup>。

提高转换速率可以通过增加比较器个数、采用异步控制等,但往往伴随功耗和面积的更多开销。随着位数增加,传统结构的DAC面积呈指数增加,可以改变分段结构来降低面积。为了降低失调,许多文章提到采用全差分结构配合混合切换<sup>[3]</sup>,然而相比单端结构会消耗更大的面积和功耗。在降低功耗上,有人通过采用动态比较器,但动态比较器带来更大的失调,需要更为复杂的

修调算法补偿<sup>[4]</sup>。

综上,本文采用CR分级、温度计码、自举开关、前置放大技术克服如上提到的缺点。

### 1 系统设计

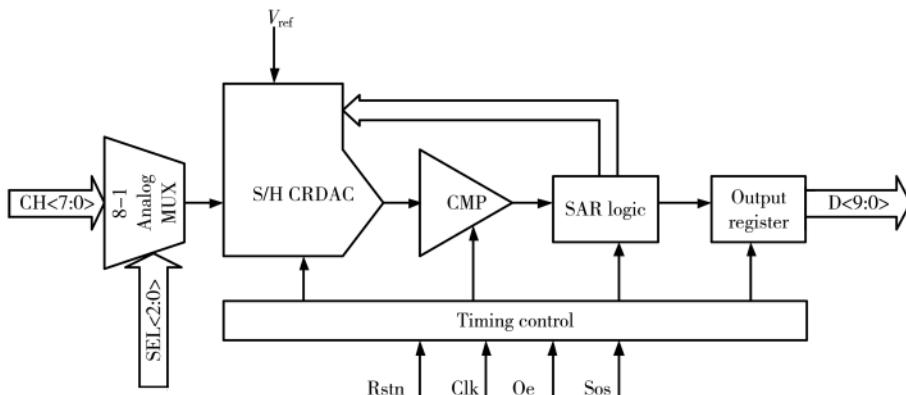

#### 1.1 SAR 系统结构

本设计的结构如图1所示,包括通道选择、采样、CR-DAC、静态比较器、SAR控制逻辑。在传统结构基础上加入通道选择控制,实现对任一通道输入的A/D转换。针对传统结构中面积大问题,采用CR分级合理选型,达到面积与性能的最优化<sup>[5-6]</sup>。

#### 1.2 SAR 系统结构

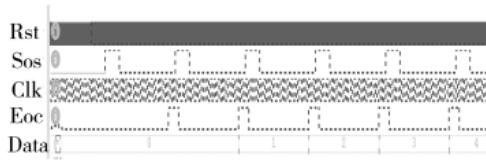

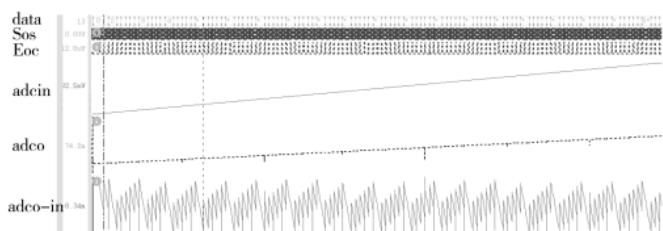

当软硬件配置好后,ADC按图2时序工作。

复位信号Rst释放后,当数字逻辑接收到Sos(Start of sample)的高脉冲后开始采样时序(>2T)。当数字逻辑接收到Sos的下降沿则会触发SAR逻辑,按照固定周期循环10T,每周期完成一次D/A转换和比较工作。按照每次的比较值设置对应sar的值。当完成最后一次比较之

图 1 SAR-ADC 功能框图

图 2 ADC 的工作时序图

后 Eoc(End of converse) 变为高 , 与此同时 , sar 的数值会读入 reg , 在数据口 D<9:0> 可获取。

在采样阶段 , 与  $V_{in}$  连接的开关全部闭合 , 输入对采样电容负极板充电 , 采样时正极板为共模电压  $V_{cm}$  , 此时采样极板的电荷量为<sup>[7]</sup> :

$$Q_{in}=2^N C_u (V_{in}-V_{cm}) \quad (1)$$

在保持阶段 , 与  $V_{in}$  连接的开关全部断开并连接地 , 正极板与共模电压间的开关也断开 , 此时正极板的电荷量为 :

$$Q_o=-2^N C_u (V_{in}-V_{cm}) \quad (2)$$

在转换阶段 , SAR 逻辑从 MSB 开始逐位置位 DAC 的输入 , 使 DAC 输出向共模点逼近。根据每次比较结果获得最终的 ADC 输出 , 经过  $N$  次比较后 , 最终的残余电荷为<sup>[8]</sup> :

$$Q_o=-2^N C_u \left( (V_{in}-V_{cm}) - D_{N-1} \times \frac{V_{ref}}{2} - D_{N-2} \times \frac{V_{ref}}{4} - \cdots - D_0 \times \frac{V_{ref}}{2^N} \right) \quad (3)$$

## 2 电路级设计

### 2.1 DAC 设计

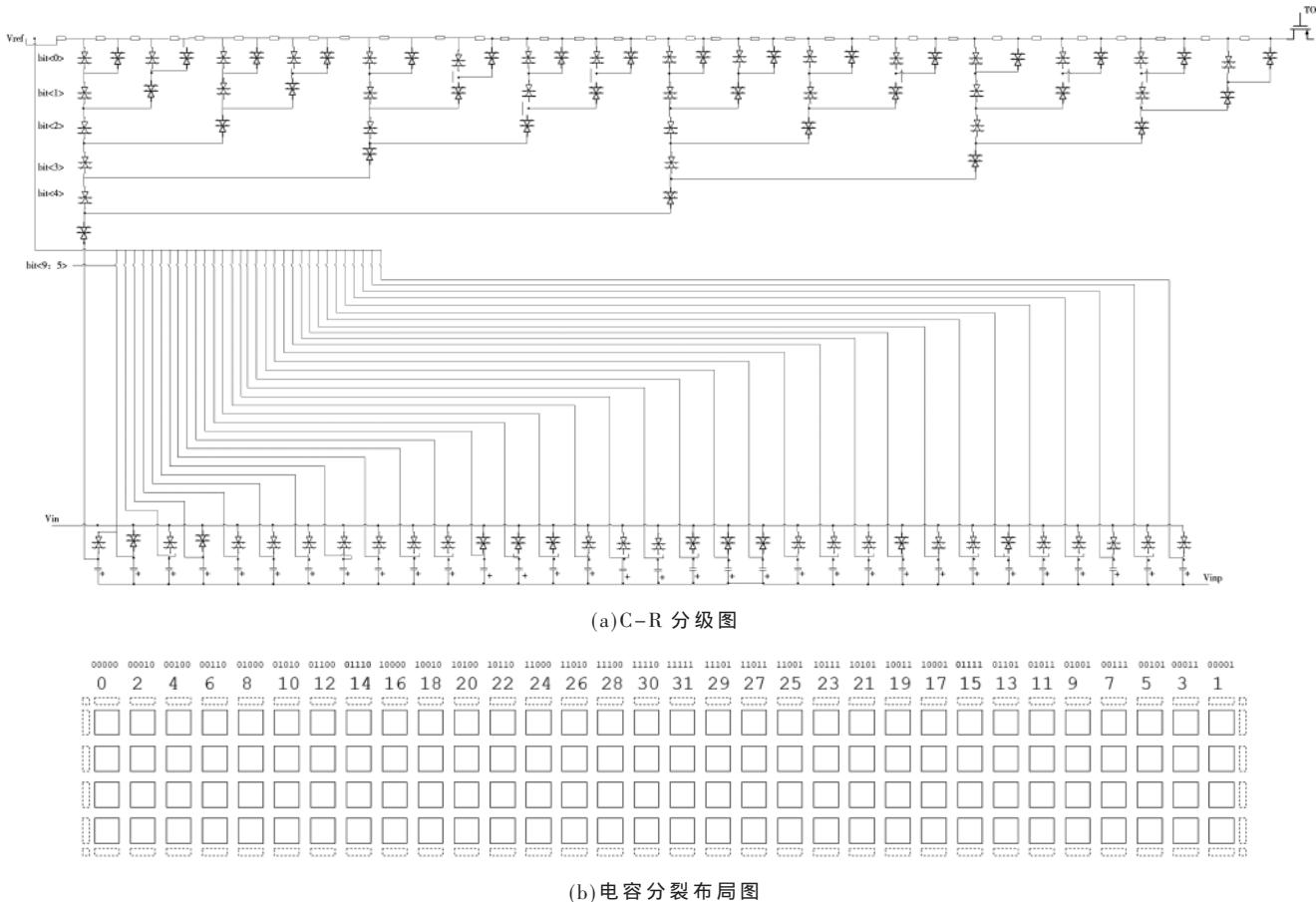

DAC 是 SAR-ADC 中最重要的子模块 , DAC 的线性会影响 ADC 精度。DAC 主要有电压定标型、电荷定标型、混合型结构<sup>[6]</sup>。电阻分压型最大的优势是能保持良好的单调性 , 但随着位数增加芯片面积也大大增加。电荷定标型 ADC 功耗一般比较小 , 并且不需要额外的采样保持电路 , 但是电容的精度和面积都是限制位数的因素<sup>[6]</sup>。电容 - 电阻 (C-R) 组合结构则可以兼具电压型与电阻型的优点 , 在降低芯片面积和功耗的同时可保证线

性<sup>[7]</sup>。文献[5, 7]针对“5+7”“6+6”以及“7+5”三种典型的 C-R 组合结构进行了功耗仿真和比较 , 低 5 位用电阻实现具有良好的单调性。

在以上研究背景下 , 本文采用“5+5”的分级结构实现 DAC 设计。图 3(a) 为 CR 混合式结构 DAC 示意图。高 5 位用电容满足高位的精度 , 低 5 位用电阻实现良好的单调性。高 5 位只需要  $32C_u$  , 而不分级的 10 位 ADC 则需要  $1\,024C_u$  , 可以大幅降低芯片面积。

二进制编码控制开关会存在开关大量切换的过程。而在开关切换过程中会引入时钟馈通和电荷注入效应。从文献[7]可获得 DNL 贡献公式如下 :

$$\sigma(DNL)_{max} = \frac{\sigma(\sum 2^i C_u)}{C_u} = \sqrt{(2^N-1)} \frac{\sigma(C_u)}{C_u} \quad (4)$$

因此在高 5 位的设计中 , 除了尽量采用大电容外 , 高 5 位全部采用温度计码设计 , 从而进一步提升芯片的 DNL。低 5 位的电阻分压型采用二进制切换即可满足要求。图 3(a) 展示的是最终确定的 DAC 结构 , 从上到下依次为电阻分压、温度计译码、电容阵列。

电容的匹配性布局设计如图 3(b) 所示。一个  $C_u$  在版图上分裂为 4 个小电容。在温度计码递增/减时 , 电容数会按照图中标注次序以 Y 轴对称交互选中/关断。

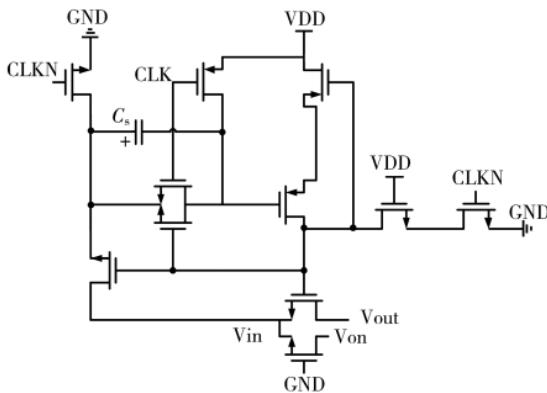

### 2.2 自举开关设计

由于单管开关的输入信号摆幅会受到开关阈值的影响 , 大多都会采用 CMOS 开关进行信号传输。但 CMOS 开关的导通电阻也很难保证恒定 , 会影响 ADC 的非线性增益误差。因此在本设计中采样开关采用自举开关 , 电阻开关采用 CMOS , 置 0/置 1 开关采用 NMOS/PMOS。

本设计中的自举开关如图 4 所示。当 CLKN 为高时 , 电源对采样电容  $C_s$  充电 ; 当 CLK 为高时 , 电路对输入电压采样 , 采样开关的栅源电压等于 AVDD , 与输入电压大小无关 , 如此则保证了很好的线性度。此外 , 在开关两端跨接了伪开关抵消部分电荷泄漏 , 采样开关的线性度更高<sup>[4]</sup>。

### 2.3 静态比较器的设计

动态比较器由时钟触发 , 速度快、静态功耗小 , 但具

图 3 DAC 结构

图 4 自举采样开关

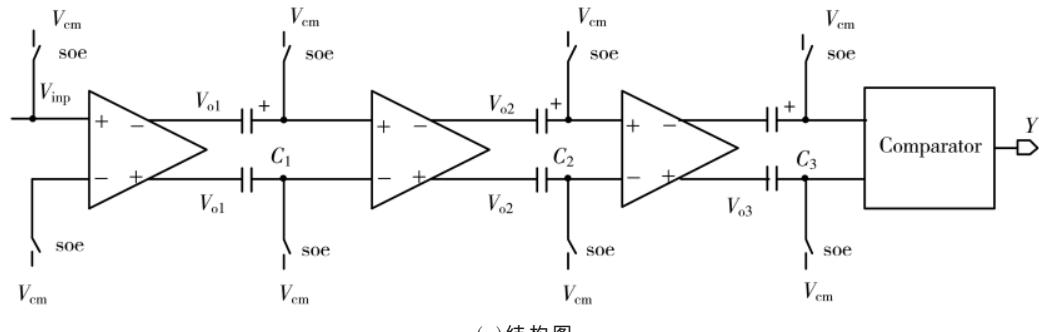

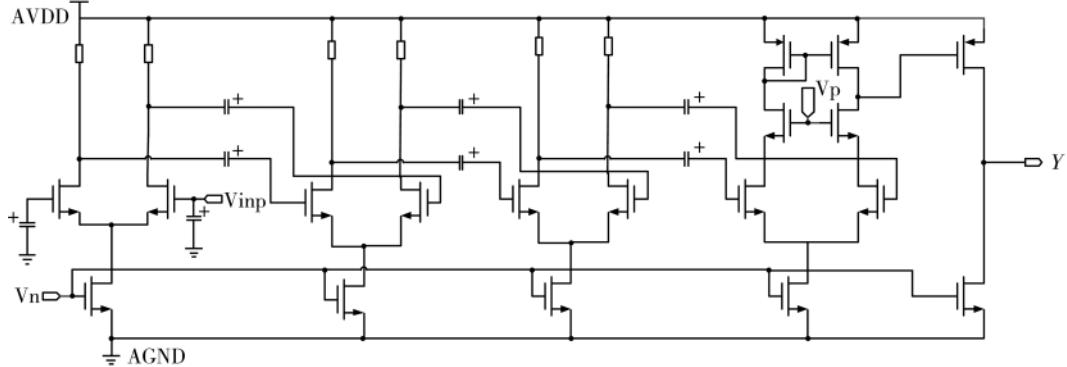

有失调电压大和回踢噪声大缺点<sup>[7]</sup>,不经过修调算法的动态比较器只能达到 6 位。因此本设计确立了静态比较器结构选型,结构如图 5(a)所示。比较器由四级构成,前三级为前置放大,输出级为双转单输出。全差分的输入级天生具有消除共模误差的作用,大增益等效降低了输出级的失调误差影响。如图 5(b)所示,静态比较器由两级构成,第一级为共源共栅,第二级为共源放大器。

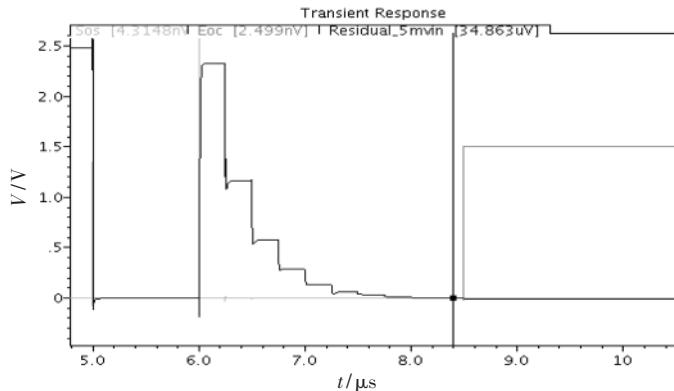

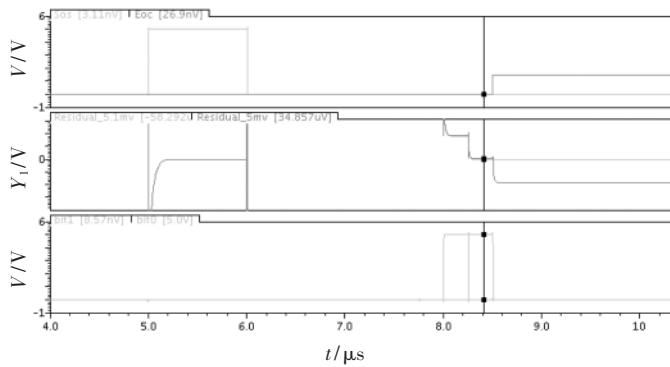

图 6 和图 7 为整体仿真中比较器输入端的残余电压。从图 7 可知输入端 0.1 mV 的差异就可造成比较器

的翻转,完全满足系统的精度要求。

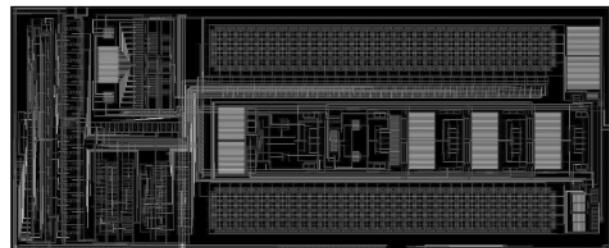

### 3 仿真结果

整个 ADC 电路在 0.13 μm 工艺上设计实现。用 Spectre 进行了子模块仿真,并用 hsim 完成 ADC 的系统仿真。ADC 核心电路版图如图 8 所示。版图的尺寸为 580 μm×290 μm。

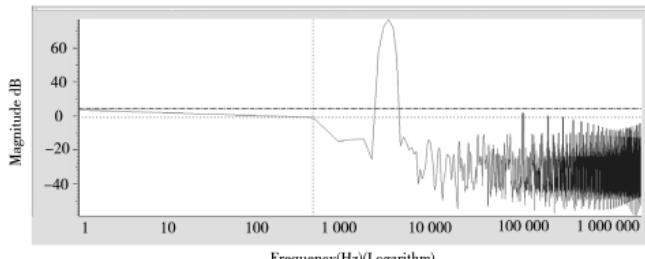

ADC 的静态参数包括失调误差、增益误差、DNL、INL、综合误差。输入斜坡信号完成全量程仿真后,通过 Analog expression 实现数字输出结果的模拟化,再与 10 位 ADC 的理想阶跃曲线取差即可获得 ADC 的静态参数。仿真结果如图 9 所示。可以看出 DNL<+0.5/-0.5LSB, INL<+0.7/-0.7LSB。

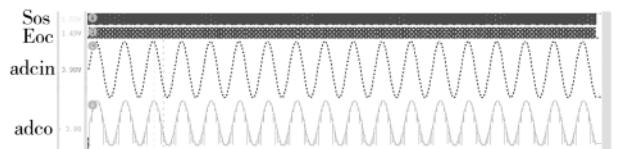

ADC 的动态参数包括 SNDR、ENOB 等。为获得动态参数,广泛的做法是输入正弦信号进行多周期仿真,然后对采样数值在 MATLAB 中做 FFT 分析。图 10(a)为输入 5 kHz 正弦信号,在采样率为 200 kS/s 时的仿真图形。为简化 ADC 的设计流程,本文采用 hsim 仿真器做整体仿真,仿真结果可以直接用 Verdi 来做 FFT 分析。图 10(b)为取样 16 384 点,并且加 Blackman 窗函数后的 FFT 结果。从频谱可看出 SNDR 达 60 dB,ENOB 达到 9.5。

当输入 50 kHz 正弦信号,在采样率为 1 000 kS/s 时,

(a) 结构图

(b) 主体电路图

图 5 静态比较器

图 6 5 mV 信号输入残余电压

图 7 对比 5.1 mV 输入时的残余电压

$\text{SNDR} = 58 \text{ dB}$ , 详见表 1。本文用品质因数 FOM (Figure-Of-Merit) 作为衡量 ADC 综合性能的标准。

图 8 模数转换器的版图

图 9 输入斜坡信号时的输出波形

$$\text{FOM} = \text{SNDR}(\text{dB}) + 10\log(\text{BW}/\text{Power}) \quad (5)$$

表 1 是与近期相似领域论文的比较结果。从表中可见,本设计的综合指标较好,有较高的性价比。

#### 4 结论

本文在  $0.13 \mu\text{m}$  工艺中设计实现了一款 10 位 SAR-ADC, 通过 C-R 结构、自举开关、温度计码控制、高精度比较器的设计有效减小芯片面积, 提高了 ADC 精度。在信号峰峰值  $4 \text{ V}$ 、信号频率为  $200 \text{ kHz}$ 、采样率为  $1 \text{ MS/s}$  下后仿真得到 SNDR 达  $58 \text{ dB}$ , ENOB 达 9.5 位。

(a) A/D 转换后的正弦

(b) FFT 结果

图 10 正弦波仿真

表 1 性能比较

|                      | 文献[7] | 文献[12] | 文献[6] | 文献[11] | 本文   |

|----------------------|-------|--------|-------|--------|------|

| 电源/V                 | 2.8   | NA     | 3.3   | 1.8    | 4    |

| 分辨率/bit              | 10    | 16     | 12    | 10     | 10   |

| Samp/(kS/s)          | 116   | 1000   | 1000  | 240    | 1000 |

| SNDR/dB              | 61.9  | NA     | 68.4  | NA     | 58   |

| 有效位/bit              | 9.9   | NA     | 10.7  | 8.2    | 9.5  |

| 功耗/mW                | 1     | 11     | 2     | 35.5   | 8    |

| FOM/dB               | NA    | 127    | 300   | 95     | 136  |

| Area/mm <sup>2</sup> | NA    | 6.5    | 0.3   | 0.1    | 0.2  |

| Process/nm           | 180   | 250    | 180   | 180    | 130  |

## 参考文献

- [1] 黄宏斌,牟云飞.逐次逼近主要结构分析[J].电子测试,2019(7):47–48.

- [2] 荆苏丹,吴朝烨.逐次逼近模数转换器专利技术分析[J].河南科技,2017,605(2):37–38.

- (上接第 43 页)

- 1–6.

- [15] 肖思昌,靳经,潘敏,等.基于机器学习的多类目标识别方法分析[J].中国设备工程,2021(16):24–25.

- [16] 韩健鸿.基于深度信息融合的遥感图像多类目标辨识技术[D].北京:北方工业大学,2021.

- [17] 老翌.基于深度学习的车辆检测与识别算法研究[D].哈尔滨:哈尔滨理工大学,2021.

- [18] 杨思樱.神经网络在微波电路计算机辅助设计中的应用研究[D].成都:西南交通大学,2009.

- [19] JAFARI A,SADRI S,ZEKRI M.Design optimization of analog integrated circuits by using artificial neural networks[C]//2010 International Conference of Soft Computing and Pattern Recognition,2010:385–388.

- [3] 陈宏铭,许升睿,曾玉光.一种电容阵列结构的 10 位 8 通道 1MS/S 逐次逼近 AD 转换器[J].中国集成电路,2013(10):28–35.

- [4] 王也,刘力源,吴南健.一种 20 MS/s 基于 VCO 比较器的二阶噪声整形 SAR ADC 设计[J].信息技术与网络安全,2021,40(6):62–68.

- [5] 佟星元.R-C 型逐次逼近 ADC D/A 转换网络功耗模型与仿真[J].系统仿真学报,2016,28(4):946–950.

- [6] 黄玲,姜岩峰,鞠家欣,等.一种 12bit CMOS 全差分 SAR ADC[J].电子世界,2014(9):20–21.

- [7] 车来晟,唐鹤,高昂,等.一款 10 位逐次逼近型模数转换器设计[J].电子与封装,2019(7):16–19.

- [8] 廖方云,王绩伟,谷京儒,等.一种提高 SAR ADC 的 D/A 转换精度的方法[J].微电子学,2019,49(5):598–601,608.

- [9] 乔峻石,李冬梅.基于开关运放的低功耗逐次逼近 ADC 设计[J].半导体技术,2008(3):252–256.

- [10] Hong Hui,Li Shiliang,Zhou Tao.Design of a low power 10 bit 300 ksps multi-channel SAR ADC for wireless sensor network applications[J].Journal of Semiconductors,2015(4):158–164

- [11] TSAI S J,CHEN Y C,HSIEH C C,et al.A column-parallel SA ADC with linearity calibration for CMOS imagers[J].IEEE Sensors,2012:1–4

- [12] ZHONG L,YANG H,ZHANG C.Design of an embedded CMOS CR SAR ADC for low power applications in bio-sensor SOC[C]//7th International Conference on ASIC,2007.

(收稿日期:2021-10-16)

## 作者简介:

邓玉清(1983-),通信作者,女,硕士,高级工程师,主要研究方向:数模混合集成电路设计,E-mail:dengyuqing321@163.com。

牛洪军(1987-),男,硕士,工程师,主要研究方向:数模混合集成电路设计。

扫码下载电子文档

- [20] PAH Z.Hierarchical test generation using neural networks for digital circuits[C]//International Conference on Neural Networks and Signal Processing,2003,2003:245–248.

- [21] 赵永强,饶元,董世鹏,等.深度学习目标检测方法综述[J].中国图象图形学报,2020,25(4):629–654.

- [22] REDMON J,FARHADI A.Yolov3:an incremental improvement[EB/OL].[2019-06-20].<https://arxiv.org/pdf/1804.02767.pdf>.

(收稿日期:2021-11-02)

## 作者简介:

林纯熙(2001-),本科,主要研究方向:通信工程和机器学习、深度学习等。

粟涛(1977-),副教授,主要研究方向:数字集成电路设计与集成电路电磁干扰分析。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所