# 基于 FPGA 的雷达 A 式显示电路设计

阮成肖

(江苏自动化研究所, 江苏 连云港 222061)

**摘要:** 为了实现对雷达显示技术的优化与升级, 设计实现了一种基于 FPGA 的雷达 A 式显示电路, 采用 FPGA 集成雷达显示 IP 核实现雷达前端信号的采样、处理及显示。该设计利用 FPGA 芯片庞大的可编程逻辑单元以及丰富的成熟 IP 核的优势, 实现了单片逻辑芯片实现雷达输入信号的接收、采样、变换以及显示的功能, 简化了以往雷达显示电路的硬件结构, 降低了信号的显示延迟, 整体提升雷达显示性能。同时该设计可以通过进一步修改内部 IP 核实现其他雷达显示方式, 使其具备硬件设备的通用性和可扩展性。

**关键词:** 现场可编程逻辑芯片; IP 核; 雷达视频; 显示技术

中图分类号: TN952

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.229987

中文引用格式: 阮成肖. 基于 FPGA 的雷达 A 式显示电路设计[J]. 电子技术应用, 2022, 48(8): 24–28.

英文引用格式: Ruan Chengxiao. Design of radar A-display circuit based on FPGA[J]. Application of Electronic Technique, 2022, 48(8): 24–28.

## Design of radar A-display circuit based on FPGA

Ruan Chengxiao

(Jiangsu Automation Research Institute, Lianyungang 222061, China)

**Abstract:** In order to optimize and upgrade radar display technology, a radar A-display circuit based on FPGA is designed and implemented in this paper. The FPGA integrated radar display IP core is used to realize the sampling, processing and displaying of radar front-end signals. The design takes advantage of the huge programmable logic unit of the FPGA chip. The rich mature IP cores realize the functions of receiving, sampling, transforming and displaying the radar input signal of the single-chip logic chip. It simplified the hardware structure of the previous radar display system, reduced the display delay of the signal, and improved the radar display performance. At the same time, the design can realize other radar display methods by further modifying the internal IP core, so that it has the versatility and scalability of hardware devices.

**Key words:** FPGA; IP core; radar video; display technology

## 0 引言

随着电子设备的飞速发展, 雷达技术也取得了跨越式发展, 当前的雷达视频显示技术已不能满足人们的需求。特别是对雷达终端显示的可操作性、分辨率, 以及显示的内容和层次提出了更高的要求<sup>[1]</sup>。雷达显示技术主要用来显示雷达所获得的目标信息和情报<sup>[2]</sup>, 完成显示雷达回波、雷达状态等信息, 是雷达系统的重要组成部分<sup>[3]</sup>。传统的雷达显示技术主要基于结构复杂的专用硬件设备, 价格昂贵, 移植性差, 通用性不够理想, 功能有限且开发升级周期较长<sup>[4]</sup>。随着现代雷达的发展, 如何依据最新的芯片技术提高雷达显示性能是雷达显示的基本要求。本文分析原有雷达显示技术的不足, 针对雷达的 A 式显示, 提出了一种基于 FPGA 的雷达 A 式显示电路设计, 实现对目标回波信号的采集、存储及实时显示<sup>[5–6]</sup>。利用现场可编程芯片庞大的逻辑单元以及越来越丰富的免费 IP 核, 将雷达 A 式显示的全部功能置

于一片 FPGA 中<sup>[7–8]</sup>, 完成单片 FPGA 可以实现雷达前端信号的分选、采样、数值变换、波门叠加、线存、帧存、像素变换等功能。

## 1 系统设计方案

### 1.1 雷达显示原理

雷达显示的目的是将雷达视频回波实时地显示在显示屏上, 而雷达 A 显的原理是将雷达信号强度和距离的关系通过直角坐标系进行表示。目标的距离与信号时间之间的关系如式(1)所示, 其中  $L$  代表目标距离,  $s$  代表回波速度(光速  $3 \times 10^8$  m/s),  $t$  代表时间。

$$2L = s \times t \quad (1)$$

要将回波视频显示在直角坐标系中, 就要将采样得到的点按照距离远近的关系进行显示, 式(2)所示为采样时间与坐标系的位置关系, 其中  $t$  为采样时间,  $T$  为采样时钟周期,  $x$  为显示位置(即直角坐标系中  $x$  坐标, 代表距离)。

$$t/T=x \quad (2)$$

结合式(1)和式(2),就会得到显示位置与距离关系,如式(3)所示,其中 $f$ 代表采样频率, $f=1/T$ 。在实际采样中为了不丢失目标,往往采用较大的采样频率,然后对一个最小采样周期内的采样点进行选取,通过取得的值进行组合进行显示,这种方式就是分选。

$$2L=s\times x/f \quad (3)$$

## 1.2 雷达显示 IP 核功能设计与实现

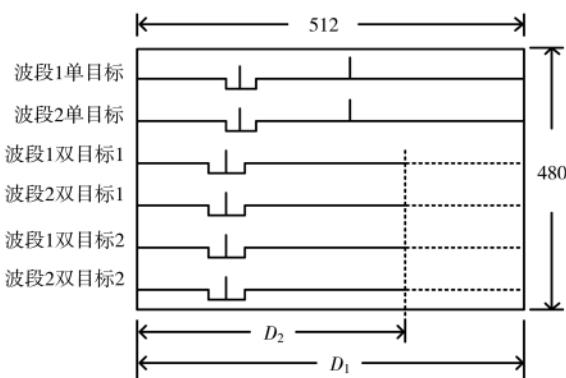

雷达显示 IP 核的设计目标是实现雷达 A 显的扫描变换。显示屏上应该显示六根扫描线,分为两组,两组由波段 1/波段 2 信号控制,波段 1/波段 2 为低电平时刷新波段 1 的三根扫描线,为高电平时刷新波段 2 的三根扫描线,不刷新时,扫描线保持上次的扫描状态。

每组的三根扫描线分别显示单目标、双重目标 1、双重目标 2 三种视频,单目标同步脉冲到来时,开始刷新单目标视频,刷新时间达到 $t_2$ (即刷新了 $D_1$  公里)时结束;双重目标同步脉冲到来时,开始刷新双重目标 1 视频,过 $t_3$ (即刷新了 $D_2$  公里)后,改为刷新双重目标 2 视频,过 $t_3$  后结束。由于 $t_3$  时间不能完全刷新 $D_1$  公里的视频,因此双重目标视频扫描线的后部需人为增补,其幅度与视频输入电平为低时相同。

波门脉冲来到时,无论正在刷新哪种视频,该视频都应叠加一个固定时间的负电平,该波门以下凹的形式出现,即采样视频减去一个固定的波门深度。

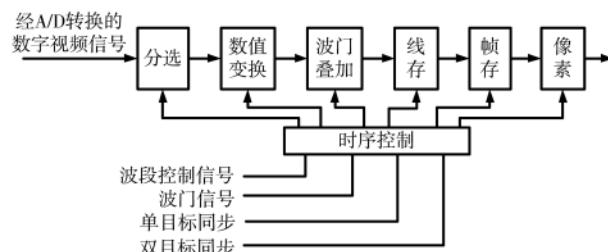

经外部模拟电路采样完成的视频信号经量程控制电路(分选)后存入线存。线存中的视频数据经读写控制写入相应的帧存中,帧存中的像素数据输出后,经像素格式转换电路,形成图像像素送到图形板,由显示屏进行显示,图 1 所示为雷达 A 显画面示意图。

图 1 雷达 A 显画面示意图

雷达显示 IP 核功能框图如图 2 所示,前端雷达模拟信号经过 A/D 转换为数字信号,经过信号的分选进行数据的采样,然后经过数值变换和波门叠加得到线存数据,线存数据线存控制器接口存入线存 RAM 中,存储方式为线性一维数据。每当同步信号来临时,帧存会从线存中读取一帧数据转存至帧存 RAM 中,存储方式为平

图 2 雷达显示 IP 核功能框图

面式存储,最后经由像素输出模块将帧存图像转换为 A 显画面。

### 1.2.1 分选模块

动态分选取值原理图如图 3 所示。为了不丢失目标,分选模块连续采样 16 次后取最大值作为该点视频采样值送入线存。原有系统中的分选取值为固定分选取值,首先在第一个分选周期完成对一组采样数值的缓存,然后通过两两比较的方式完成一次数据的过滤,直至取到最大值。这种方式需要占用大量的寄存器,且至少存在一个分选周期的数据延迟,同时,如果增加采样点的个数,寄存器数量会成倍地增加,且数据延迟会更大。

图 3 动态分选取值原理图

本文设计选用动态分选取值占用更少的寄存器,且有更少的数据延迟,又因为分选取值的改变并不会降低视频的分选效率,使得系统可以根据具体的情形选择自己的分选次数,增加了系统的灵活性和适应性。

### 1.2.2 数值变换与波门叠加

波门信号在上升沿时有效,每当一个波门上升沿来临,模块自行生成固定宽度的波门,波门宽度的大小可通过软件选择。波门采用下凹式显示,下凹深度的大小可通过软件选择。

图形分辨率为 $1280\times1024$  时,设波门下凹深度为 BD,首先对采样、分选后的 8 位视频值 AD\_DATA[7:0] 进行数值变换,将其灰度值从 0~255 的范围变换到 0~(64-BD)的范围。在无波门时,变换后的视频值加上 BD 后送入线存;在波门下凹期间,变换后的数值直接送入线存。

数值变换,即灰度等级变换,由于两个灰度级之间的比例关系为小数0~0.25,为了实现硬件小数换算,本文使用累加器和移位寄存器。设定累加器权值寄存器,通过位加权确定寄存器取值,加权值如下: $K[5]=0.125$ , $K[4]=0.062\ 5$ , $K[3]=0.031\ 25$ , $K[2]=0.015\ 625$ , $K[1]=0.007\ 812\ 5$ , $K[0]=0.003\ 906\ 25$ 。

硬件中的小数就是通过该寄存器直接进行乘法,然后右移8位来实现。设分选产生的数据为 $D_{sample}$ ,经变换后数据为 $D_{trans}$ ,gate代表有无波门,那么该模块的换算关系如下所示:

$$D_{trans} = \begin{cases} K \times D_{sample}, & \text{gate} = 1 \\ K \times D_{sample} + BD, & \text{gate} = 0 \end{cases} \quad (4)$$

从式中可以看出,由于本文使用硬件语言描述,为了防止数值变换时出现负值,故采用无波门叠加的方式进行波门的控制。

### 1.2.3 线存模块

采样的视频数据,经过数值变换和波门叠加之后,变为低灰度值数据,存入由片内双口RAM设计的线存中,每当目标同步信号到来时,连续向线存中写入数据,当屏幕刷新信号到来时,帧存模块从RAM读数据端口读取线存数据。

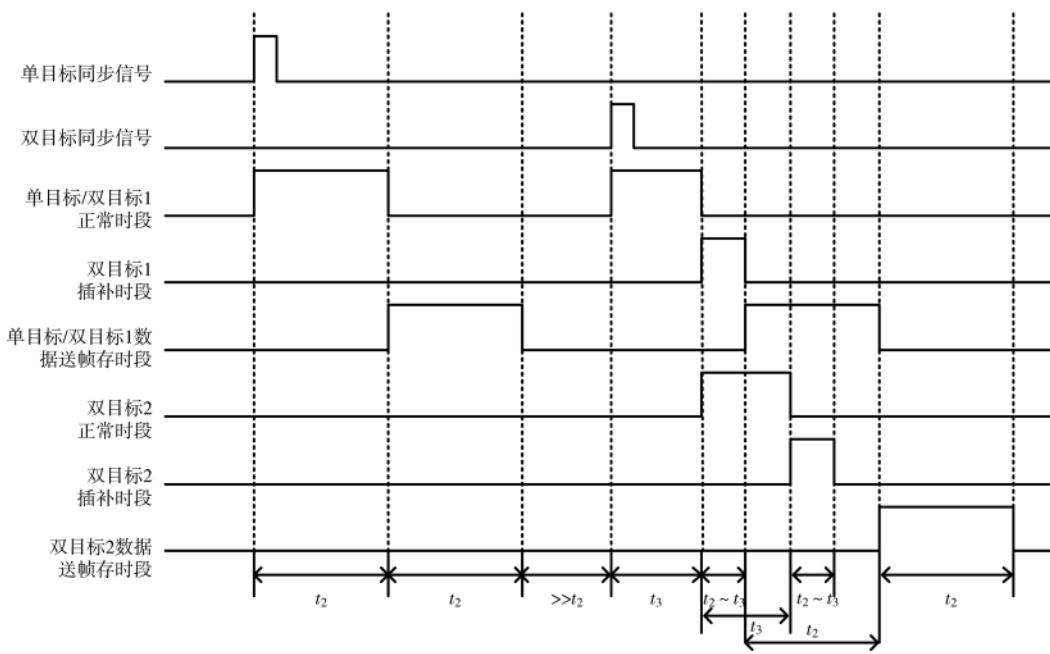

由于双重目标1视频和双重目标2视频之间是连续的,为了确保数据完整性,线存由两个片内双口RAM组成。单目标同步信号到来时,开始将采样处理后的视频数据送入线存RAM1,送512个采样数据后停止送数;双重目标同步信号到来时,将采样处理后的视频数据送入线存RAM1,送300( $t_3$ 对应采样点)个采样数据后停止送入线存RAM1,改为送入线存RAM2,送300个数据后停止送数。线存数据传输的控制时段如图4所示。

六路A显的距离量程都是 $D_1$ ,但四路双重目标A显的有效距离只有 $D_2$ 。为了使六路A显的距离轴长度一致,需要将双重目标A显的距离轴进行延长。由于在双重目标同步周期每个目标的回波都只有 $t_3$ 时间有效,不能使用延长采样时间办法来加长距离轴,而需用插补方法实现。

距离轴插补的方法是在处理后的数据送入线存前,需经过一个选择器,当单目标回波信号或双重目标回波信号有效时,选择真正的数据送线存;插补距离轴时则选择一个“小波发生器”的数据给线存。所谓“小波发生器”是一组低电平噪声数据,也可以使用低电平的常值数据代替。由于A显的扫描变换周期远大于 $t_2$ ,有足够的插补时间。无论双重目标1还是双重目标2,它们的插补时间均在采样 $t_3$ 时间后,如图4中所示。

### 1.2.4 帧存模块

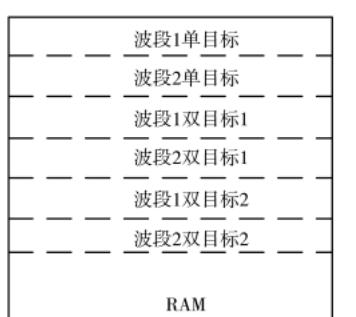

帧存数据存储的是一帧图像的数据,数据的存储是平面式的存储方式,本文使用片内双口RAM设计帧存体,为了实现平面式存储,RAM中按照地址段存储的方式顺序存储每一帧数据。根据实际要求,数据在帧存体中的存储顺序如图5所示,线存数据的传输顺序与帧存存放有很大不同,因此线存向帧存的数据传输采用寻址的方式进行。

由于帧存数据保存的是一帧完整的显示图像,那么为了避免视频信号因为外界干扰而产生突发脉冲,或者视频采样过程中丢失采样目标,造成显示图像的缺损而影响显示效果,本文采用FPGA内部双口RAM的乒乓切换进行帧存缓存<sup>[9]</sup>,并在帧存模块的两个帧存体之间引入写相关的功能,这样既可以消除图像缺损,又能够使图像产生衰减的效果。

图4 线存控制时段时序

图 5 帧存数据存放示意图

### 1.2.5 像素输出模块

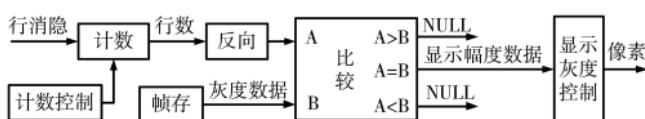

雷达视频通过 A/D 转换电路, 得到的是信号的灰度值数据, 经由数据变换到存储在帧存中的像素格式也是如此。但雷达 A 显的显示功能上是用 X 坐标轴表示距离, Y 坐标表示信号的幅度。帧存中的像素输出时, 进行一次数据格式转换, 将信号灰度转换为图像幅度。

首先对屏刷新的行同步进行计数; 其次在像素输出时, 将像素的信号灰度值与行同步计数结果相比较。若两者相等, 则判该像素为有, 显示该像素; 反之, 则判该像素为无, 不进行显示。按以上方法处理后, 输出的就是像素的图像幅度。数据格式转换处理框图如图 6 所示。

图 6 像素数据格式转换框图

## 2 上位机软件设计

本文设计基于 Windriver 平台的 PCI 驱动程序, 得到用户层 PCI 函数库, 通过这些函数实现对硬件设备寄存器组的访问。为了实现系统的各项显示功能, 本文还要进行上位机应用程序的设计。

本文采用 VC 平台的 MFC 函数类库来实现雷达显示系统应用程序设计<sup>[10]</sup>, 上位机的应用程序设计主要分为三个部分: 一是雷达显示控制单元; 二是雷达信号源单元; 三是读写测试单元。表 1 和表 2 中所示为 3 个功能单元的具体窗口功能列表。

表 1 雷达显示控制单元功能列表

| 主要窗口    | 具体功能                                                                                              |

|---------|---------------------------------------------------------------------------------------------------|

| 雷达视频开窗  | 窗口坐标: 开窗左上角第一个点的坐标, 可任意设定, 但不得超过图形板开窗最大值<br>窗口大小: 雷达 6 条扫描线占据的窗口大小                                |

| 波门设定    | 波门宽度: 设定波门的具体显示宽度, 可在 0~7 之间设定, 但是为了能够较好地包含峰值, 建议在 5~7 之间选择<br>波门高度: 用于设定扫描线下凹的深度, 可在 0~15 之间任意设定 |

| 信号源开关   | 用于外部信号源和板上信号源的切换                                                                                  |

| 6 路 A 显 | 6 路显示开关: 用于选择显示哪几路扫描线, 6 条扫描线独立显示, 互不影响<br>6 条扫描线颜色: 选择每条扫描线的颜色, 每条扫描线各有 6 种颜色可供选择                |

| 图像冻结    | 用于冻结扫描图像, 使其显示当时扫描情况                                                                              |

表 2 雷达信号源单元和读写测试单元功能列表

| 主要窗口       | 具体功能             |

|------------|------------------|

| 无目标视频值     | 没有具体目标时的回波信号水平   |

| 目标视频值      | 有具体目标时的回波信号水平    |

| 单目标初始坐标    | 单目标被发现时的距离信息     |

| 双目标 1 初始坐标 | 双目标 1 被发现时的距离信息  |

| 双目标 2 初始坐标 | 双目标 2 被发现时的距离信息  |

| 波段开关       | 双波段显示的选择开关       |

| 目标种类       | 固定目标视频<br>移动目标视频 |

| 地址         | PCI 总线地址         |

| 数据         | PCI 总线数据         |

根据具体的功能列表, 完成雷达显示系统软件功能界面, 如图 7 所示。

图 7 雷达显示系统软件

## 3 系统验证

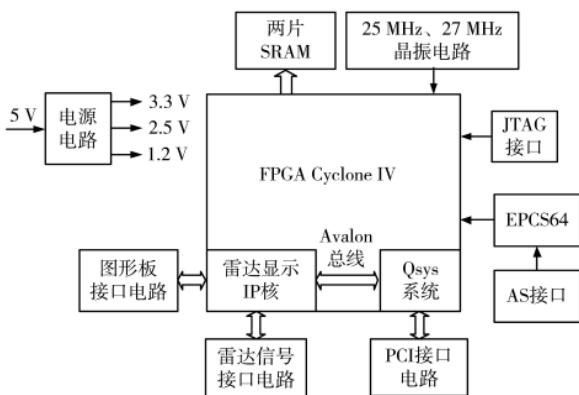

雷达显示板所有的功能设计全部围绕一片 FPGA 芯片展开。除了 FPGA 芯片之外, 显示板上还包括电源电路、雷达接口电路、图形板接口电路、PCI 接口电路、两片 SRAM 存储芯片、25 MHz 和 27 MHz 晶振电路、JTAG 接口以及 AS 接口。其中雷达接口电路、图形板接口电路以及 PCI 接口电路均通过 CPCI 插槽与外部连接。图 8 所示为雷达显示板硬件结构图。

本文根据系统验证要求搭建系统调试环境, 系统调试环境主要由以下部分组成: 调试底板、主板、图形显示

图 8 雷达显示板硬件结构图

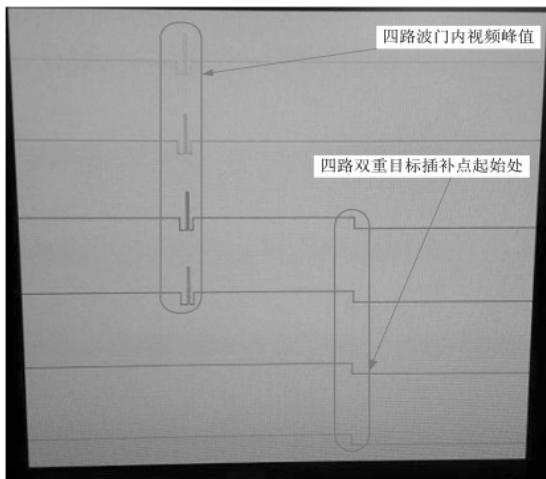

板、雷达显示板、显示器、键盘鼠标和电源模块。按照要求对平台进行搭建。系统平台搭建完毕后,通过 EDA 环境将雷达显示 IP 核下载至雷达显示板中,并将信号源的软件描述通过上位机软件环境加载至雷达显示板中,启动系统调试环境,进行系统验证。图 9 所示为系统验证环境图,图 10 为雷达 A 显验证效果图,从图中可以看出,该雷达显示 IP 核能够实现雷达 A 显需求。

针对本文设计的雷达显示系统和原有雷达显示系统的实时性问题,本文通过对两者在不同功能模块的数据

据延迟以及总体的数据延迟,对两者性能进行分析对比。表 3 所示为新老雷达显示板功能模块的延迟时间。

表 3 两个系统各功能模块延迟时间对比

(ns)

|     | 分选模块 | 数值变换<br>波门叠加 | 线存模块  | 帧存模块  | 总体    |

|-----|------|--------------|-------|-------|-------|

| 本设计 | 98   | 1 172        | 1 120 | 856   | 3 558 |

| 原设计 | 402  | 1 208        | 1 300 | 1 620 | 4 922 |

从表 3 中的延迟时间对比可知,本文雷达显示系统的各个功能模块相较原有的雷达显示系统延迟时间都有所减少,特别是分选模块和帧存模块,由于作了相应的改进,实时性大幅度提高。

#### 4 结论

本文主要完成了一种基于 FPGA 的雷达 A 式显示电路设计与实现,该技术利用 FPGA 芯片庞大的可编程逻辑单元以及丰富的成熟 IP 核的优势,实现雷达输入信号的接收、采样、变换以及显示的功能,简化了以往雷达显示系统的硬件结构,降低了信号的显示延迟,整体提升雷达显示性能。同时该设计可以通过进一步修改内部 IP 核实现其他雷达显示方式,使其具备硬件设备的通用性和可扩展性。

#### 参考文献

- [1] 莫军.基于 FPGA 和 ARM 的雷达视频混合显示技术[J].信息技术与信息化,2014(2):60–62,65.

- [2] 杨雷.基于 FPGA 的雷达显示终端的研制[D].成都:电子科技大学,2015.

- [3] 陆迪.基于 FPGA 和计算机视频混合的雷达终端显示设计[J].中国科技信息,2012(12):165,175.

- [4] 赵新雪,张永利.一种雷达回波数据处理及显示方法[J].电子世界,2021(7):160–161.

- [5] 陆海林.X 波段船舶导航雷达显示控制与存储系统开发[D].南京:南京信息工程大学,2016.

- [6] 王金龙.船用导航雷达信号处理系统设计与实现[D].哈尔滨:哈尔滨工程大学,2014.

- [7] 左龙军,李和平,李建雄.基于 Nios II 和 HDMI 的高清雷达显示系统[J].计算机测量与控制,2011,19(7):2729–2732.

- [8] 张敏,赵宜楠,乔晓林.一种专用雷达目标显示平台的实现[J].电视技术,2011,35(13):35–37.

- [9] 孙玉梅,张彦飞,王美春,等.基于 FPGA 的雷达信号高速实时采集和显示系统设计[J].电子器件,2018,47(1):63–65.

- [10] 徐恺.雷达多功能显示终端设计与实现[D].西安:西安电子科技大学,2017.

(收稿日期:2022-05-18)

#### 作者简介:

阮成肖(1989-),男,硕士研究生,工程师,主要研究方向:雷达显示、图形显示等。

扫码下载电子文档

图 9 系统验证环境

图 10 雷达 A 显验证效果图

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所