# 一种加速大规模模拟和射频 IC 后仿真的验证流程

陈思雨<sup>1</sup>, 黄亚平<sup>1</sup>, 胡 劍<sup>1</sup>, 曾 义<sup>2</sup>

(1. 深圳市中兴微电子技术有限公司, 广东 深圳 518055; 2. 上海楷登电子科技有限公司, 上海 200120)

**摘要:** 近年来, 模拟射频 IC 的功能越来越多, 导致片上集成的功能模块快速增加。且进入到先进工艺节点后, 单一模块的后仿真网表规模急剧增加。对后仿真速度以及 debug 效率提出了极高的要求, 除了使用更为先进的 FULL-SPICE 仿真器(比如 Cadence Spectre X 等)提升仿真速度之外, 对后仿真输入文件格式的选择与优化同样是一种有效提升整体后仿真效率的方法。主要讨论 Cadence Quantus 最新的 SmartView 输出格式以及与 ADE Assembler 和 Spectre X 联合加速后仿真验证的一种新流程, 并给出了与传统流程的对比结果。

**关键词:** Quantus ; SmartView ; ADE Assembler ; 大规模后仿验证

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.229802

中文引用格式: 陈思雨, 黄亚平, 胡剑, 等. 一种加速大规模模拟和射频 IC 后仿真的验证流程[J]. 电子技术应用, 2022, 48(8): 42–45.

英文引用格式: Chen Siyu, Huang Yaping, Hu Jie, et al. A verification flow on speed-up large-scale analog and RFIC post-layout simulations[J]. Application of Electronic Technique, 2022, 48(8): 42–45.

## A verification flow on speed-up large-scale analog and RFIC post-layout simulations

Chen Siyu<sup>1</sup>, Huang Yaping<sup>1</sup>, Hu Jie<sup>1</sup>, Zeng Yi<sup>2</sup>

(1. Sanechips Technology Co., Ltd., Shenzhen 518055, China; 2. Cadence Design Systems, Inc., Shanghai 200120, China)

**Abstract:** Recently, the functions and features implemented on Analog/RF ICs increases greatly which requires much more circuit blocks to be integrated into one single chip. On the other hand, with advanced node processes adopted, the post-layout netlist size of a single circuit block increases sharply. All of these pose a high demand on performance and efficiency of post-layout simulations and debugs. Except on adopt advanced Full-SPICE simulators, like Cadence Spectre X, to speed-up post-layout simulations, the choice and optimization method on post-layout input for simulator is another efficient methodology to speed-up overall post-layout verifications. This paper mainly focused on introducing a new post-layout simulation speed-up flow provided by Cadence Quantus SmartView and ADE Assembler with Spectre X, also comparisons with traditional flows are presented.

**Key words:** Quantus ; SmartView ; ADE Assembler ; large-scale post-layout verification

## 0 引言

一般模拟射频电路仿真流程主要包括网表生成(netlisting), 仿真(simulation)和结果计算(results evaluation)。纯粹仿真速度的提升毫无疑问能加快模拟设计迭代, 但是另一方面, 随着模拟射频电路复杂性的增加以及制造工艺的不断进步, 模拟工程师需要考虑和验证的工艺角(PVT corner)急剧增加, 需要处理的电路规模越来越庞大。着眼于模拟射频电路仿真验证全流程的设计方法学需要进一步优化。

Cadence Quantus 晶体管级寄生参数抽取工具提供的 SmartView 输出格式正是针对这种需求推出的。该输出格式是 ADE Assmbler 以及 Spectre X 仿真器无缝支持的, 在生成 SmartView 这种格式的网表时所需要的时间急剧减小, 相比于传统的 av-extracted view, 其 OA view 的体积缩小非常多, 且在整个寄生参数抽取到仿真开始

这一过程中, 寄生参数网表仅需完整产生一次, 而传统流程是完整的两次, 另外, SmartView 还保留了传统 av-extracted view 提供的后仿真 debug 流程。

本文应用两个规模不同的后仿真设计, 对比 Quantus 生成 SmartView 以及 av-extracted view 的时间, ADE Assembler 在 netlisting 这两种 view 时需要的时间以及仿真器(Spectre X)在这两种情况下的性能与精度情况。

## 1 电路介绍

芯片设计进入小尺寸工艺后, 所对应的后仿真网表规模也急剧增加, 这对于工具本身的优化、仿真器算法的提升、电路设计方法的快速迭代以及计算资源等方面提出了更高挑战。

本文所用的两个后仿真电路均采用 FinFET 工艺。其一是 afc dac filter(自动频率校准数模转换滤波器)电路, 主要功能是将数字信号转化成 1 bit 电压信号, 通过输出

单端电压控制片外的 VC-TCXO(压控晶体振荡器)的压控端子,从而达到调整 VC-TCXO 的输出参考频率的目的。其二是 adc(模拟数字转换器)电路,实现的是将模拟信号输入的信号经过滤波器积分,再经过量化器量化为数字信号的这一过程。两个电路性能的主要评价指标均是有效位数(Effectice Number of Bits, ENOB)。

这两个电路通过目前主流的 av-extracted view 网表进行后仿真时,存在生成网表文件很大、生成网表时所需时间较长、图形界面长时间不能操作、后仿真时间长、后仿真 debug 困难等问题,影响迭代效率。

## 2 Quantus SmartView 以及 ADE Assembler 和 Spectre X 介绍

在 SmartView 问世之前,一般模拟射频仿真使用的后仿真设计是 dspf/spice 之类的文本格式网表或者 av-extracted view 之类的图形化设计视图(cellview)。文本格式网表的缺点是后仿真 debug 几乎不可能或者需要大量人工操作,且不符合模拟射频工程师习惯的电路拓扑结构设计流程。av-extracted view 之类的图形化视图(cellview)在电路规模不太大的情况下是一种非常优秀的后仿真设计视图。

SmartView 是 Quantus 提供的第二代 av-extracted view 输出格式,具有使用文本格式网表进行后仿真以及使用图形化设计视图(cellview)进行后仿真 debug 的全部优点。

ADE Assembler/Explorer 是 Cadence Virtuoso ADE XL/L 的升级加强版,相比于 ADE XL/L, ADE Assembler/Explorer 最大的优势在于两者均支持多工艺角和蒙特卡洛仿真。且其核心的仿真任务管理机制在最近几年进行了基础性的重大革新,能够同时进行 1000+ 仿真任务的管理。

Spectre X 仿真器是 Cadence 于 2019 年推出的新一代 FULL-SPICE 仿真器,提供高达 10 倍的速度提升以及高达 5 倍的容量提升,使用方式非常简单,支持多线程多进程技术,最新版本支持高达 512 线程的仿真任务。

## 3 后仿真性能对比

本文使用的设计电路均采用 FinFET 工艺,分别对比了 SmartView 和 av-extracted view 两种输出格式的提参结果、生成网表时间、后仿真的性能差异。

### 3.1 Quantus SmartView 和 av-extracted view 提参结果

利用 Quantus 工具分别抽取 av-extracted view 和 SmartView 两种格式的提参文件,分别对比提参所需时间以及生成的 OA view 的文件大小,结果对比展示在表 1 中。

表 1 两种 View 的提参结果

| 电路设计   | Quantis           |        |          |

|--------|-------------------|--------|----------|

|        | 输出类型              | 抽取时间   | 文件大小     |

| adc    | av-extracted view | 49m45s | 3.05 GB  |

|        | SmartView         | 33m25s | 360.3 MB |

| filter | av-extracted view | 14m34s | 888 MB   |

|        | SmartView         | 20m19s | 173.6 MB |

从表 1 可看出,从抽取时间上来说,SmartView 和 av-extracted view 两者是比较接近的。在抽取生成文件大小方面,对于电路规模较大的 adc 电路来说,传统的 av-extracted 生成的 OA view 文件达到 3.05 GB,而 SmartView 仅 360.3 MB,OA view 减小了 88.19%;对于电路规模正常的 filter 电路来说,生成的 OA view 同样减小达到 80.45%。可以看出,SmartView 在规模大小不同的两类电路中,对于降低文件大小的表现趋于一致且十分理想,均能达到 80% 左右的减小。

SmartView 提参出来的 OA view 能明显减小文件大小的原因可以从数据结构上来分析,如图 1 所示。以 adc 这个电路为例,av-extracted 抽取的电路特征和寄生信息集成在 layout.oa 文件中间,这个文件大小达到 3.05 GB,如图 1(a)所示,所以使用 av-extracted view 进行分析,如后仿真、生成网表、查看寄生等操作均需要等待较长时间,操作十分不便。而 SmartView 将电路特征和寄生信息分别存放在 layout.oa 和 detailed\_rc.oa 两个文件中,单个文件仅 360.3 MB 和 556 MB,如图 1(b)所示。

|                                                                                                                                                               |                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>4.0K May 13 2022 . 4.0K May 13 10:42 .. 2.3K May 13 10:43 CCLFile 3.2K May 13 10:43 data.dm 3.1G May 13 10:43 layout.oa 38 May 13 10:43 master.tag</pre> | <pre>4.0K May 6 15:07 . 4.0K May 13 10:42 .. 2.4K Apr 29 16:21 CCLFile 3.4K Apr 29 16:27 data.dm 556M Apr 29 16:40 detailed_rc.oa 361M Apr 29 16:41 layout.oa 38 Apr 29 16:07 master.lag</pre> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

(a)av\_extracted\_view

(b)SmartView

图 1 两种 view 数据结构对比

av-extracted view 支持的寄生参数反标回电路原理图的功能是一种有效的后仿真 debug 手段,但存在的问题是当 av-extracted view 文件很大时,这种反标操作需要非常多的时间。

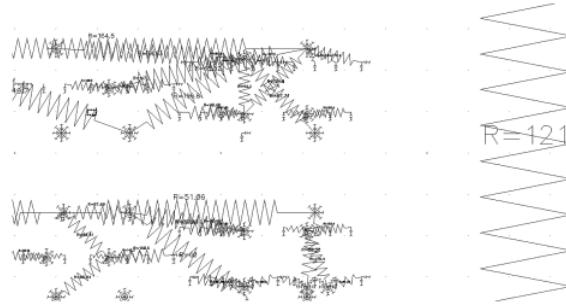

SmartView 保留了该功能且得益于全新的数据结构,极大地降低了 cellview 的文件大小,可以直接在版图上快速预估寄生电阻、寄生电容以及寄生电感,效果如图 2 所示。

图 2 smart-parasitics 效果展示

需要注意的是 smart-parasitics 提供的预估值最佳应用场景应当是快速分析版图实现带来的寄生效应,精确评估寄生参数对电路性能的影响还需借助普通 PVT 仿

真或者其他后仿真流程实现。

### 3.2 ADE Assembler 网表生成时间对比

基于 adc 和 filter 两个电路, 分别抽取 av-extracted view 和 SmartView 两种格式的寄生参数, 使用 ADE Assembler 生成后仿真网表, 记录下所需时间, 如表 2 所示。从表 2 可以看出, adc 电路利用 av-extracted view 生成网表需要 5 754.0 s(约 96 min), 而使用 SmartView 则仅需要 2 132.0 s(约 36 min), 有效缩短生成网表时间 62.95%, 近 1 个小时。同样地可以看到, 在 filter 电路中, 使用 SmartView 生成网表比 av-extracted view 节约 86.67% 的时间, 由原来的 900.0 s 缩短到 120.0 s。

表 2 ADE Assembler 网表生成时间对比

| 电路设计   | ADE Assembler     |          |       |

|--------|-------------------|----------|-------|

|        | 输出类型              | 网表生成时间/s | 提升/%  |

| adc    | av-extracted view | 5 754.0  | -     |

|        | SmartView         | 2 132.0  | 62.95 |

| filter | av-extracted view | 900.0    | -     |

|        | SmartView         | 120.0    | 86.67 |

在后仿真过程中, 需要先利用提参文件生成网表, 再提交给仿真器进行仿真。但在生成网表过程时, 为单线程运行模式, 所以图形界面会一直保持生成网表的状态, 不能进行其他操作, 而在使用 SmartView 时, 得益于 cellview 文件大小的大幅度降低, 即使是在前台产生网表, 图形界面不允许操作的时间大幅度降低。

另外, 如果使用 ADE Assembler 进行仿真, 默认设置下, 甚至感觉不到图形界面不允许操作的时间。

ADE Assembler 提出了一套全新的仿真任务管理机制 LSCS(Large Scale Cloud Simulation), 据 Cadence 描述, 这是一套 Cloud ready 的分布式仿真任务调度技术。区别于以往技术的最大特点在于将网表任务和仿真任务分隔, 网表任务所需的时间一般远小于仿真任务但会消耗内存资源。在之前的模式下, 网表任务和仿真任务是统一管理的, 而在 LSCS 模式, 网表任务在工作完成之后是可以直接退出的。且网表任务也支持分布式技术, 在计算资源管理明确的环境下可以将网表任务计算队列和仿真任务队列分开, 最优化仿真计算环境。

另外, 一般的仿真验证电路包含两部分, 一是测试电路(testbench), 二是设计电路(Design Under Test, DUT)。通常进行多 PVT 仿真时, 控制 DUT 变化的因素一般都存在于 testbench 当中。即 DUT 网表在多 PVT 仿真时是不变的, 变化的仅仅是 testbench 网表。

在 ADE 传统默认模式下, 每一个 PVT corner 事实上都需要单独生成网表。

而在 LSCS 模式下, 多 PVT 仿真时, DUT 的网表是默认复用的, 所有 PVT 工艺角仅需一个 DUT 网表, 其他工艺角仿真仅需更新测试电路(testbench)的网表, 这能够

极大减小网表生成时间和消耗的资源, 尤其是 PVT 工艺角非常多的情况下。

ADE Assembler 提供的 LSCS 模式带来的多 PVT 工艺角仿真优势很难直接数据描述, 因为其相对于传统模式来说, 是工作模式的改变。

### 3.3 Spectre X 仿真结果对比

为了讨论 SmartView 抽取的寄生文件的可靠性如何, 在 3.2 节生成后仿真网表的基础上, 使用 Spectre X 进行仿真, 得到两种提参文件的性能对比, 如表 3 所示。主要依据电路后仿真完成后计算得到的 ENOB 这一指标, 以 av-extracted view 的结果作为参考, 判断 SmartView 得到的结果与之的差异。

表 3 Spectre X 仿真结果对比

| 电路设计   | 输出类型              | 内存/GB | 运行时间     | ENOB/bit | 差异/%  |

|--------|-------------------|-------|----------|----------|-------|

| adc    | av-extracted view | 17.9  | 7h35m    | 10.96    | -     |

|        | SmartView         | 13.5  | 7h33m57s | 10.89    | -0.64 |

| filter | av-extracted view | 4.26  | 3d5h22m  | 10.24    | -     |

|        | SmartView         | 4.32  | 3d2h55m  | 10.37    | +1.27 |

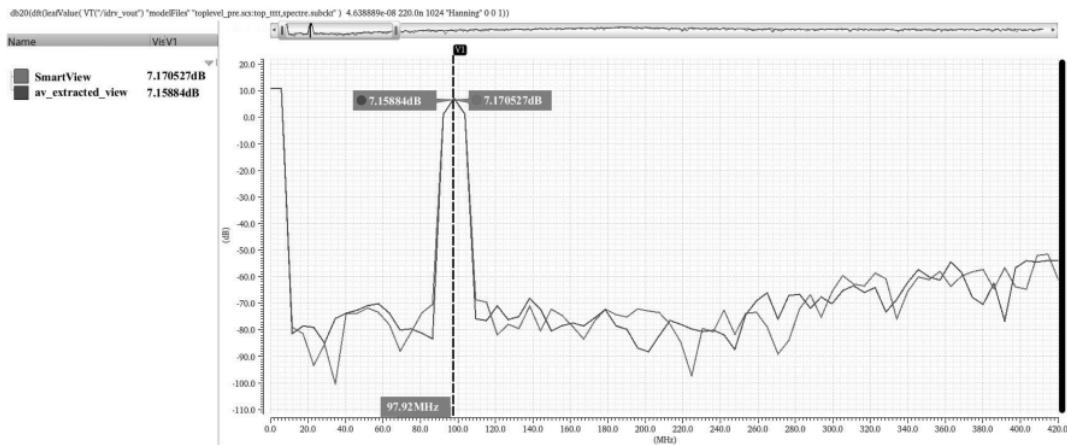

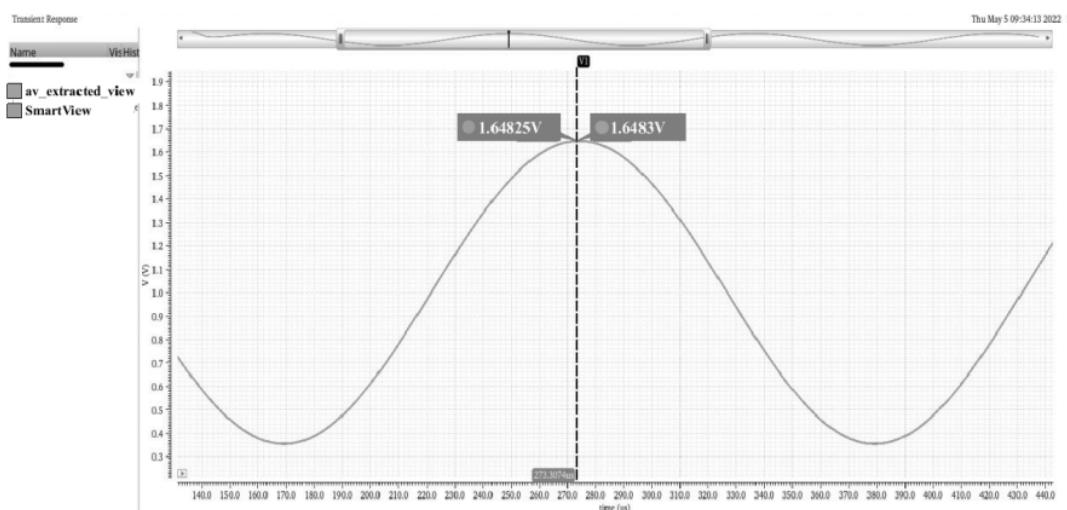

首先以 adc 电路来说, av-extracted view 得到的 ENOB 结果为 10.96 bit, SmartView 得到的结果为 10.89 bit, 两者仅相差 0.64%, 在频谱图上体现如图 2 所示, 两者在信号频率(97.92 MHz)上几乎完全一致, 仅相差 0.01 dB。在其余频段上亦几乎没有差异。对于 filter 电路的结果, 从图 3 中可以看出, 两种提参方式得到的波形几乎完全重合, 在具体数值上仅相差 0.000 05 V。SmartView 得到的 ENOB 比 av-extracted view 的略高 1.27%。

从两个电路得到的结果综合来看, 可以认为 SmartView 与 av-extracted view 的结果是十分接近且可信的。

从表 3 中两者对比的具体仿真数据, 仍可以看到 SmartView 的其他优势。对于 adc 电路来说, 均使用精度为 mx、16 核 CPU 进行计算。av-extracted view 总的运行时长为 7h35m, 使用内存为 17.9 GB, 得到的有效位为 10.96 bit。SmartView 总的运行时间为 7h33m57s, 与 av-extracted view 相比分别 +4.58%、+0.54%、-0.23%, 这三者均相差不大。但在使用内存上, SmartView 仅使用 13.5 GB, 相比减少 24.58%, 当计算资源一定时, 内存使用的减少更能加快仿真效率。

### 4 结论

本文讨论了 SmartView 和 av-extracted view 在抽取结果、生成网表及后仿真结果及性能上的差异, 可以看到 SmartView 的抽取格式在后仿真结果可靠的前提下, 具有有效减小 OA view 的文件体积, 缩短生成网表的时间, 节省内存等优势, 实现了从模拟射频设计后仿真全流程上的改进与优化, 这些对于先进工艺的电路设计后仿真来说都是十分有益的。

另外, 本文中提到的部分功能事实上动态的, 比如

图 2 adc 电路两种网表的波形及频谱对比

图 3 filter 电路两种网表的波形及频谱对比

smart-parasitics, 不能完整进行描述。ADE Assembler 支持的 config sweep 功能可以实现同时扫描 design cellview, 比如前后仿真可以同时进行, 可以很方便地观察前后仿真结果差异。

#### 参考文献

- [1] Quantus user guide version 21.2[Z].2022.

[2] ADE Assembler user guide version ICADVM20.1[Z].2022.

(收稿日期: 2022-06-20)

(上接第 41 页)

- [2] 郭炜, 魏继增, 郭筝, 等. SoC 设计方法与实现[M]. 北京: 电子工业出版社, 2011.

[3] 朱健, 胡凯, 张伯钧. 智能合约的形式化验证方法研究综述[J]. 电子学报, 2021, 49(4): 792–804.

[4] 谢小赋, 曾梦岐, 庞飞. 面向计算机并发程序的形式化验证方法设计[J]. 信息安全与通信保密, 2022(3): 54–62.

[5] 朱夕辉. 核电厂仪控系统中 FPGA 的形式验证方法及 V&V 技术[J]. 工业控制计算机, 2017, 30(10): 84–85, 87.

#### 作者简介:

陈思雨(1997-), 女, 硕士, 模拟 IC 设计工程师, 主要研究方向: ADC/DAC 模拟电路设计。

黄亚平(1990-), 男, 硕士, 资深高级模拟 IC 设计工程师, 主要研究方向: 高性能射频和数模混合 IC。

胡劼(1984-), 男, 硕士, 资深模拟 IC 设计专家, 主要研究方向: 高性能射频和数模混合 IC。

扫码下载电子文档

(收稿日期: 2022-06-20)

#### 作者简介:

赵亚雪(1994-), 女, 硕士, IC 验证工程师, 主要研究方向: 无线通信基带芯片系统设计、通用处理器芯片设计。

植玉(1981-), 男, 硕士, IC 验证经理, 主要研究方向: 无线通信基带芯片系统设计、通用处理器芯片设计。

梁其锋(1985-), 男, 硕士, IC 验证专家, 主要研究方向: 无线通信基带芯片系统设计、通用处理器芯片设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所