# 基于老化特征化提取进行时序分析的解决方案

陈寒,宋存彪,吴韦忠

(中兴微电子技术有限公司 后端设计部 FoundationIP, 上海 200120)

**摘要:** 基于 Cadence 的 Liberate + Tempus 解决方案,采用一种先进的标准单元老化特征化的方法,同时考虑了偏置温度不稳定性(Bias Temperatrure Instability, BTI)和热载流子注入(Hot Carrier Injection, HCI)老化效应,得到标准单元老化时序库,用于 Tempus 进行考虑老化的静态时序分析(Aging-aware Static Timing Analysis, Aging-aware STA)。产生一套先进的标准单元老化时序库,能够针对不同标准单元不同传输路径,表征一定范围的老化应力条件的时序特征,改善了传统添加全局时序减免值导致电路 PPA(Performance/Power/Area)难以收敛的问题,同时只需要调用一套标准单元库也使 STA 更加简洁易操作。

**关键词:** 老化标准单元库; Cadence Liberate; Aging Aware STA; Tempus

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.229804

中文引用格式: 陈寒,宋存彪,吴韦忠. 基于老化特征化提取进行时序分析的解决方案[J]. 电子技术应用, 2022, 48(8): 51-54, 59.

英文引用格式: Chen Han, Song Cunbiao, Wu Weizhong. Solution to aging timing analysis based on aging characterization[J]. Application of Electronic Technique, 2022, 48(8): 51-54, 59.

## Solution to aging timing analysis based on aging characterization

Chen Han, Song Cunbiao, Wu Weizhong

(SANECHIPS Technology Co., Ltd., Backend Design Dept. FoundationIP, Shanghai 200120, China)

**Abstract:** In this paper, an aging standard cell library considering both BTI(Bias Temperatrure Instability) and HCI(Hot Carrier Injection) is obtained by an advanced characterization method based on Cadence Liberate + Tempus solution, which can be used by Tempus to perform Aging-aware Static Timing Analysis(Aging-aware STA). Compared to setting a flat derate to the circuit, the aging library indicates the timing information of a certain range of aging stress conditions for different arcs of different cells, which optimizes PPA(Performance/Power/Area)of the circuit. In addition, only one library is invoked making STA simpler and easier to operate.

**Key words:** aging library; Cadence Liberate; aging aware STA; Tempus

## 0 引言

近年来,CMOS 技术不断发展至纳米级先进工艺,带来的可靠性问题也越来越突出,众多老化效应,例如偏置温度不稳定性(Bias Temperatrure Instability, BTI)、热载流子注入(Hot Carrier Injection, HCI),成为提高超大规模集成(Very Large Scale Integrated, VLSI)电路可靠性的主要挑战<sup>[1-3]</sup>。BTI 效应是由于在氧化层界面的不饱和 Si 键在 H<sub>2</sub> 退火过程中形成 Si-H 键。当器件的栅极给到足够的电压产生持续的电场应力时(对于 NMOS 是高电平-VDD,对于 PMOS 是低电平-VSS),这些 Si-H 键很容易断裂,H 原子变成游离态并留下陷阱。随着更高的电压和更高的温度,陷阱态的生成速度加快,导致阈值电压(V<sub>th</sub>)增加、漏端电流(I<sub>ds</sub>)减少以及沟道中电子迁移率下降<sup>[4-5]</sup>。在先进工艺中,负栅极偏置(Negative Bias Temperatrure Instability, NBTI)的 PMOS 会产生比正栅极偏置

(Positive Bias Temperatrure Instability, PBTI) 的 NMOS 更严重的衰退。HCI 效应通常发生在数字电路中信号转换时,器件源漏极和栅极施加高电压时,沟道中具有源极指向漏极的高横向电场,沟道中的空穴在横向电场加速下,会与晶格碰撞发生散射或电离,部分载流子能在垂直于界面方向获得足够的能量而幸运地注入到栅氧化层中形成界面态或被陷阱捕获,极少部分会到达栅极形成栅电流,在小尺寸器件中,沟道中的高能载流子注入造成器件损伤是热载流子效应导致器件性能退化的主要原因。这些注入载流子影响器件的 V<sub>th</sub> 和跨导(G<sub>m</sub>),导致 I<sub>ds</sub> 的衰退<sup>[6]</sup>。考虑到老化效应的影响,电路设计人员通常会在时序路径上加上一定时序减免值以保证电路能在经历老化后也可以在不同条件和特定频率下工作<sup>[7]</sup>。

器件的老化程度依赖于其老化应力条件,包括电压、

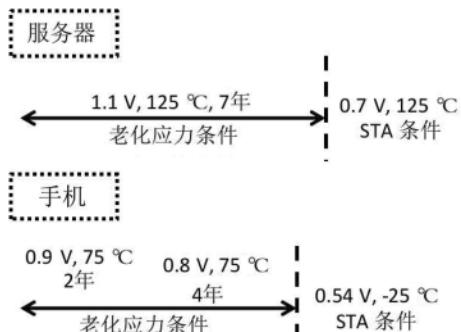

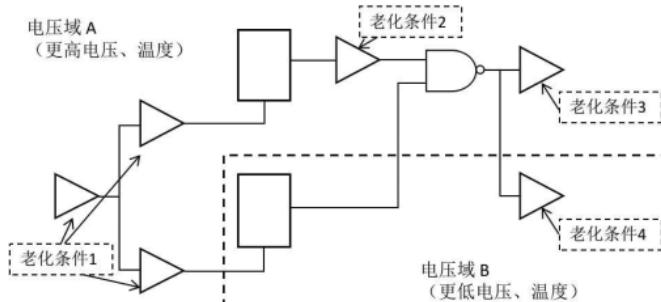

温度和老化时间,最终影响单元的时序特性,许多应用领域如移动通信、汽车、航空航天等,都会根据使用情况产生相对应的应力条件,因此在进行 Aging-aware STA 时会考虑不同的老化条件,如图 1 所示。同一个的标准单元在不同的信号传输路径或不同深度时,其老化应力条件也会有所差别,如图 2 所示。通常,这些不同的应用场景以及不同老化应力条件在标准单元特征化过程中是无法得到体现的。

图 1 动态的 STA 环境

图 2 同一个标准单元在不同路径不同深度有不同的老化条件

基于这种情况,电路设计人员有两种选择,第一种方法是考虑最坏情况,所有路径都考虑最大的老化衰减,即所有的路径统一加上时序减免值,使得老化效应在所有时序路径上都能够被体现。这个方式的优点是保守且安全,但却容易造成整体时序过于悲观,使得 STA 收敛困难,最终导致其芯片性能大打折扣。第二种方法是通过 SPICE 仿真表征出大量的标准单元库用以覆盖不同的老化应力条件,因为一套老化单元库只对应于一种应力条件,需要大量的标准单元库才能满足设计需求,这极大增加了设计成本。

本文将提供一种先进的标准单元老化时序特征化的方法用于 5 nm 先进工艺节点,该方法是基于 Cadence 的 Liberate+Tempus 的解决方案,以实现 STA 签核。产生的一套老化标准单元库可以包含一个应力范围,并且根据不同标准单元/路径进行老化分析,以实现 STA 可以有针对性地设置时序减免值来进行设计裕量设置。以下将从该方法的流程和数据分析上进行详细说明。

## 1 Liberate 进行先进的标准单元老化时序特征化的流程

该方法是用 Cadence 公司的 Liberate 进行标准单元老化时序特征化。产生的老化标准单元库可借助于 Tempus 进行 Aging-aware STA。

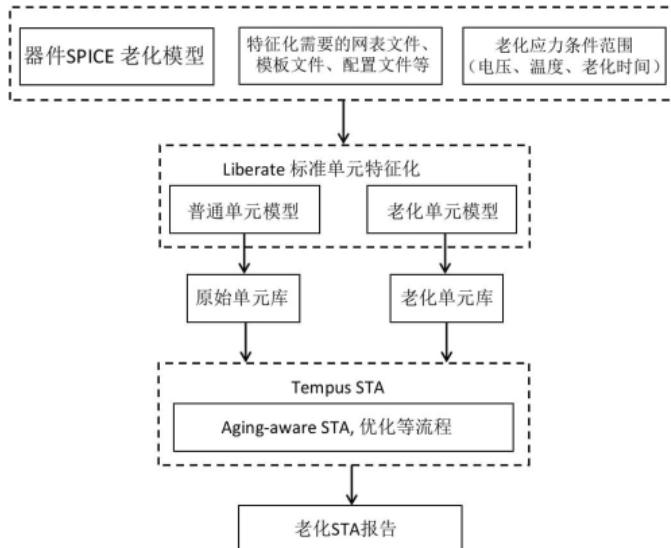

图 3 为标准单元老化时序特征化+Tempus STA 流程示意图。输入特征化所需文件,包括器件的 SPICE 老化模型(如 TMI(TSMC Modeling Interface)模型),一定范围的老化应力条件,以及相关网表文件、模板文件、配置文件等,经过 Liberate 输出不带老化效应的原始标准单元库和覆盖所有应力条件的老化标准单元库。在产生老化标准单元库之前,会产生表征单元中的器件老化情况的中间文件,包含  $V_{th}$  变化量和  $I_{ds}$  变化量。最终产生的老化标准单元库模型针对每个标准单元的不同路径进行规定应力条件下的老化时序计算,得到老化后的时序差值,但是这个值无法直接读取,需借助 Tempus 进一步应用。产生的原始标准单元库和老化标准单元库用于后续 Tempus 进行 Aging-aware STA。

图 3 标准单元老化时序特征化+Tempus STA 流程示意图

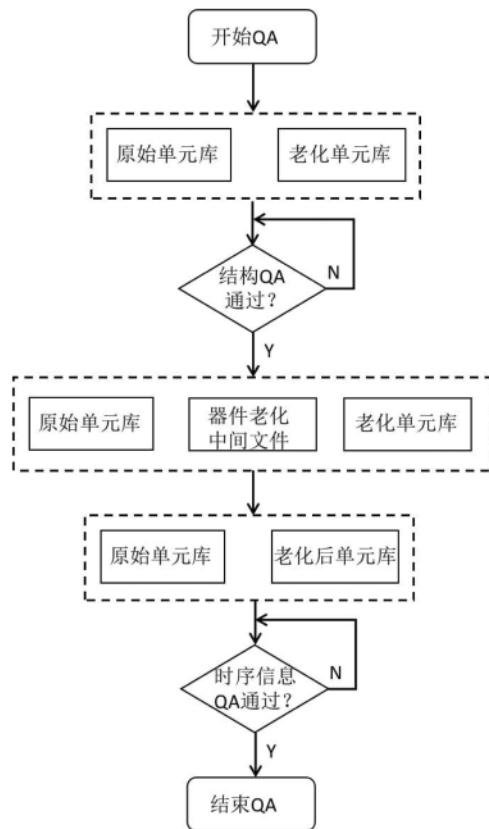

为了保证标准单元库的质量,需要对老化标准单元库进行 QA。主要有两步,如图 4 所示,首先进行结构 QA,对比产生的老化标准单元库和原始标准单元库,检查两者的标准单元及路径的信息是否相对应。由于特征化之后无法从老化标准单元库中直接读取老化时序差值,因此需要进行第二步 QA,经过一系列复杂的计算将特征化产生的表征器件老化情况的中间文件、老化标准单元库和原始标准单元库进行整合,产生一个老化后标准单元库,表征了库中单元经历应力条件老化后的最终时序信息,将老化后标准单元库与原始标准单元库进行库时序信息比较,进一步验证老化效应产生的影响。

图 4 Liberate Advanced Aging Characterization QA 流程图

## 2 结果与讨论

### 2.1 单元中的器件在老化应力条件下的衰退

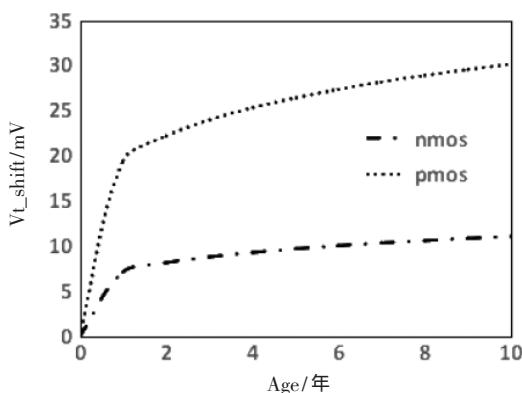

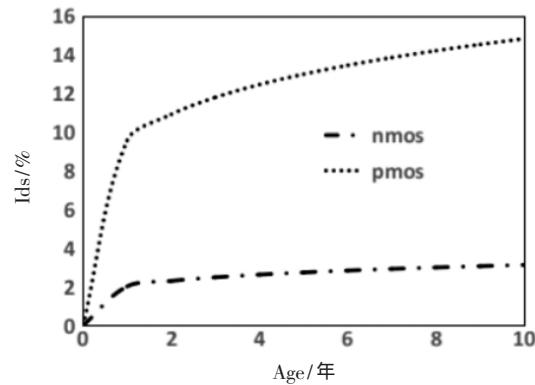

对于数字电路设计的时序分析来说，影响其可靠性的最主要的两个效应是 BTI 和 HCI。文中的先进标准单元老化特征化流程考虑了这两种效应。图 5 为在 5 nm 先进工艺节点下，一个反相器单元(Inverter)中的器件(PMOS/NMOS)在特定老化应力条件(电压为 1.0 V、温度为 125 °C)下  $V_{th}$  随着老化时间(Age)的增加情况，老化时间为 10 年时，PMOS 的  $V_{th}$  增加量为 30 mV，NMOS 的  $V_{th}$  增加量为 11 mV，图 6 为其  $I_{ds}$  的衰退情况，老化时间为 10 年时，PMOS 的  $I_{ds}$  衰退率为 14.8%，NMOS 的衰退率为 3.1%。

图 5 HCI+BTI 引起的  $V_{th}$  偏移(1.0 V, 125 °C)图 6 HCI+BTI 引起的  $I_{ds}$  衰退率(1.0 V, 125 °C)

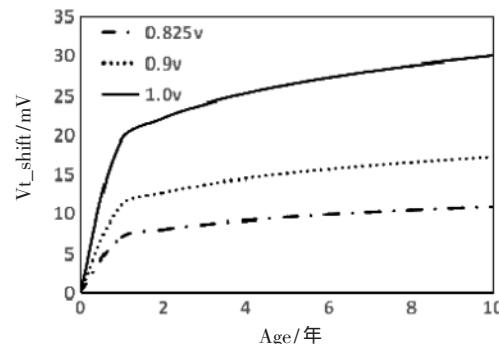

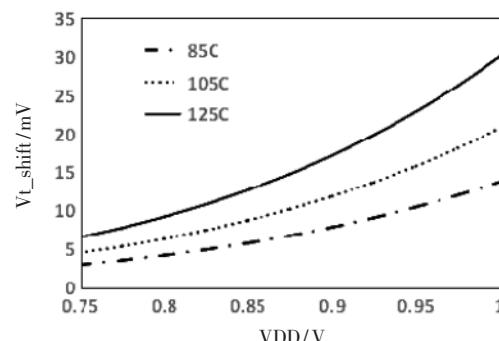

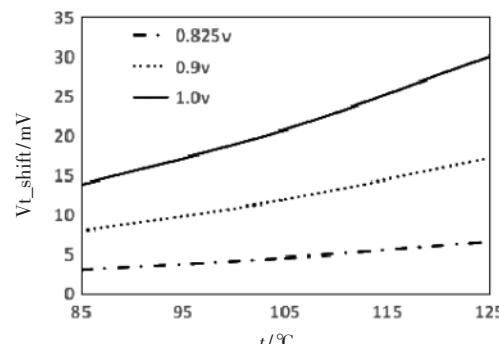

器件在不同老化应力条件下的  $V_{th}$  增加如图 7 所示。老化应力条件中任一条件的变大都导致器件性能的

(a) 不同 VDD 下  $V_{th}$  随 Age 的偏移曲线(b) 不同温度下  $V_{th}$  随 VDD 的偏移曲线(c) 不同 VDD 下  $V_{th}$  随温度的偏移曲线图 7 不同的老化应力条件导致的  $V_{th}$  偏移

进一步衰退。

## 2.2 标准单元在老化应力条件下的时序变化

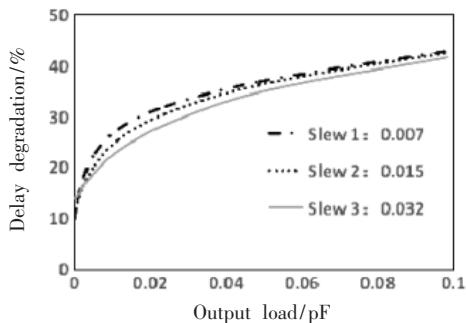

在数字电路中,由BTI和HCl导致的器件性能变化会使相应标准单元的延时产生严重影响,进而影响电路的时序。一个反相器标准单元经过的一定老化应力条件(1.0 V, 125 °C, 10 年)下的上升沿延时衰退情况在翻转率(Slew)分别为0.007、0.015、0.032时随着输出负载(Output load)的变化如图8所示。可以看出,HCl+BTI效应对反相器的延时影响很大,并且在slew一定时,延时衰退随着load增大而变大,老化效应引起的最大延时衰退为42.9%。

图8 HCl+BTI引起的上升沿延时衰退

## 2.3 Advanced Aging-aware STA 与 SPICE 对比

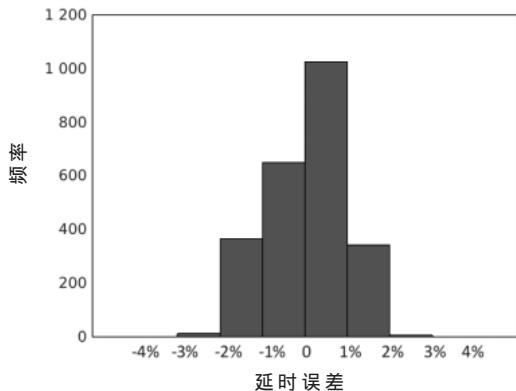

通过对Advanced Aging-aware STA与SPICE仿真结果验证用Liberate进行老化时序特征化结果的精度。SPICE的老化数据是Tempus找到传输路径后调用Cadence Spectre运行全可靠性仿真收集的,包括对器件的应力条件下的老化分析和后续对时序的老化分析。Advanced Aging-aware STA则是由本文提到的Liberate+Tempus的解决方案得到的数据。在一定的老化应力条件下,对上述两种方法得到的由BTI引起的老化标准单元库中所有单元的传输路径的延时进行对比,并统计两者的差值,如图9所示。计算的标准单元的传输路径一共2 398条,平均绝对误差为0.75%。数据表明,采用本文先进的老化标准单元库得到的数据体现了良好的单元级精度。

图9 Advanced Aging-aware STA与SPICE的延时差值统计

## 2.4 Advanced Aging-aware STA与设置统一时序减免值对比

传统考虑老化效应的STA的方法会设置统一时序减免值(Flat Derate)并加在所有的传输路径上,即认为所有的路径经历老化后会发生一样的时序衰退,这样会导致电路设计的负时序裕量(Total Negative Slack, TNS)数量增加,使得电路的PPA(Performance/Power/Area)难以取得较优结果。本文中的先进老化标准单元库中不同的路径有不同的时序减免值,有效减少了TNS,能得到较好的PPA。在一定应力条件(0.9 V, 105 °C, 10 年)下,两种方法得到的对建立时间(Setup)分析的TNS如表1所示,设置统一时序减免值得到的老化标准单元库产生的TNS为190,而由本文的先进老化标准单元库产生的TNS为124,减小了35%。

表1 Advanced Aging-aware STA与Flat derate的TNS差异

|           | Flat derate | Advanced Aging-aware STA | Delta |

|-----------|-------------|--------------------------|-------|

| Setup TNS | 190         | 124                      | 35%   |

## 3 结论

本文的基于Liberate先进标准单元老化特征化得到的老化标准单元库考虑了影响芯片可靠性的主要老化效应BTI和HCl,该流程操作简单,数据可靠合理,主要有以下优点:

(1)相比于将一个固定的时序减免值加到标准单元库中得到老化标准单元库的过于悲观方法,文中的先进老化标准单元库对不同单元不同传输路径进行有针对性的赋予设计裕量的分析更合理,更接近实际情况。

(2)用SPICE仿真得到的一套老化标准单元库只体现一种应力条件,Aging-aware STA对大量的单元库的需求增加了设计成本;而文中得到的一套先进老化标准单元库包含一定范围内的老化应力条件,因此进行Aging-aware STA时,只需调用一个单元库即可,操作更简洁也节省了成本。

(3)先进老化标准单元库的TNS数量小于传统的设置固定时序减免值的TNS数量,能实现STA签核产生更大收益,得到较好的PPA。

## 参考文献

- [1] JI Z, CHEN H, LI X. Design for reliability with advanced integrated circuit (IC) technology: challenges and opportunities[J]. Sci. China Inf. Sci., 2019, 62(12): 1–4.

- [2] ULLMANN B, JECH M, PUSCHKARSKY K, et al. Impact of mixed negative bias temperature instability and hot carrier stress on MOSFET characteristics—Part I: experimental[J]. IEEE Trans. Electron Devices, 2019, 66(1): 232–240.

- [3] 郝跃, 刘红侠. 微纳米MOS器件可靠性与失效机理(精)[M].

(下转第59页)

电源强壮性和 signal bump 数量以及产生重合导致的短路数,电源强壮性可以用电源网络面积占芯片面积比例量化,算法优化后,电源网络面积占比由 25% 提升至 33%,signal bump 数会体现在流程报告中,由 10 860 提升至 15 402,而且不会产生重合导致短路。

## 6 结论

本实验在对于 Integrity 3DIC EFS 后端流程进行实现且优化后,获得了设计的 PPA 数据,对同一设计不同频率的 2D 芯片实现的 PPA 数据对比,得到结果如表 2、表 3 所示。

表 2 1.25 GHz 频率下 PPA 对比

|                   | 2D          | 3D        | 收益/% |

|-------------------|-------------|-----------|------|

| 尺寸/ $\mu\text{m}$ | 1 200×1 200 | 800×800×2 | 11.2 |

| WNS/ns            | -0.24       | -0.117    |      |

| TNS/ns            | -4 126      | -22       |      |

| 实际频率/GHz          | 1.01        | 1.133     | 12   |

| 功耗/mW             | 2 961       | 2 868     | 3.2  |

由上述结果对比可得:在基于 Integrity 3DIC EFS 工具优化,结合芯盟 HITOC Design Kit 下的逻辑堆叠逻

(上接第 50 页)

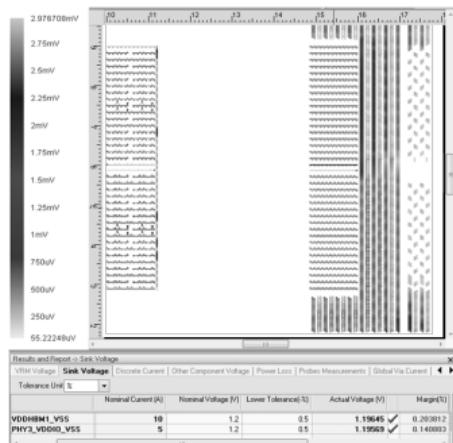

图 22 HBM 接口电源直流压降仿真

(上接第 54 页)

北京:科学出版社,2008.

- [4] SCHRODER D K.Negative bias temperature instability(NBTI): physics, materials, process, and circuit issues[J].Tutorial IRPS, 2005:67–74.

- [5] 张月.PMOSFET 器件 NBTI 效应的机制与模型研究[D].西安:西安电子科技大学,2014:54–56.

- [6] LI E, ROSENBAUM E, TAO J, et al. Hot carrier effects in nMOSFETs in 0.1/spl mu/m CMOS technology[C]//Reliability Physics Symposium Proceedings, 1999.37th Annual. 1999 IEEE International.IEEE, 1999: 253–258.

表 3 1.35 GHz 频率下 PPA 对比

|                   | 2D          | 3D        | 收益/% |

|-------------------|-------------|-----------|------|

| 尺寸/ $\mu\text{m}$ | 1 200×1 200 | 800×800×2 | 11.2 |

| WNS/ns            | -0.288      | -0.152    |      |

| TNS/ns            | -9 282      | -1 054    |      |

| 实际频率/GHz          | 1.062       | 1.198     | 13   |

| 功耗/mW             | 3 378       | 3 292     | 2.5  |

辑芯片后端实现,与传统 2D 芯片实现的 PPA(性能、功耗、面积)对比中,本实验获得了频率提升 12%、面积减少 11.2%、功耗减少 2.5% 的收益。

## 参考文献

- [1] 姚明军.基于混合键合和后硅通孔的晶圆级三维芯片堆叠技术研究[D].大连:大连理工大学,2019.

(收稿日期:2022-06-20)

## 作者简介:

徐睿(1995-),男,本科,芯片设计师,主要研究方向:芯片设计、数字后端设计。

王贻源(1985-),男,硕士,芯片设计师,主要研究方向:芯片设计、数字后端设计。

扫码下载电子文档

以支持 HBM2e 3.2 Gb/s,兼具了性能和成本优势。

## 参考文献

- [1] Cadence OrbitIO reference guide version 17.4[Z].2019.

- [2] Cadence Innovus user guide version 20.10[Z].2020.

- [3] Cadence Innovus text command reference Version 20.10[Z].2020.

(收稿日期:2022-06-20)

## 作者简介:

张成(1978-),男,硕士,封装设计经理,主要研究方向:先进封装设计。

李晴(1978-),女,硕士,研发中心总监,主要研究方向:Memory、Flash、先进封装设计。

赵佳(1984-),女,硕士,封装设计主任工程师,主要研究方向:AIoP 等先进封装设计。

扫码下载电子文档

- [7] ZHANG Z, WANG R, SHEN X, et al. Aging-aware gate-level modeling for circuit reliability analysis[J].IEEE Trans. Electron Devices, 2021, 66(9): 4201–4207.

(收稿日期:2022-06-20)

## 作者简介:

陈寒(1993-),女,硕士,IC 工艺库设计工程师,主要研究方向:标准单元库设计。

宋存彪(1990-),男,硕士,IC 工艺库设计高级工程师,主要研究方向:标准单元库设计。

吴韦忠(1981-),男,硕士,IC 工艺库设计经理,主要研究方向:标准单元库设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所