# 基于 Liberate+Tempus 的先进老化时序分析方案

欧阳可青<sup>1,2</sup>, 王彬<sup>1</sup>, 魏琦<sup>1,2</sup>, 鲁超<sup>1</sup>, 陈俊豪<sup>3</sup>, 李鸣霄<sup>3</sup>

(1. 深圳市中兴微电子技术有限公司, 广东 深圳 518055;

2. 移动网络和移动多媒体技术国家重点实验室, 广东 深圳 518055; 3. 上海楷登电子科技有限公司, 上海 200000)

**摘要:** 在先进工艺节点(7 nm, 5 nm 及以下)下, 电路老化已经成为制约芯片性能和可靠性的“卡脖子”难题。老化效应将导致器件延时增大, 进而产生时序违例的风险。数字电路设计工程师需要在时序分析中预判老化后的时序情况, 并针对性地设置时序裕量, 才能确保芯片在服役期限中可靠地运行。鉴于此, 导入基于 Liberate+Tempus 的考虑老化效应的静态时序分析(aging-aware STA)方案。评估结果显示, 该方案能在兼顾效率、准确性、多样场景老化时序分析的同时实现时序裕量释放, 为达成具备更高可靠性和更佳性能的先进芯片设计提供有力依据。

**关键词:** 芯片老化; 静态时序分析; Tempus; aging-aware STA

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.229806

中文引用格式: 欧阳可青, 王彬, 魏琦, 等. 基于 Liberate+Tempus 的先进老化时序分析方案[J]. 电子技术应用, 2022, 48(8): 60–64, 69.

英文引用格式: Ouyang Keqing, Wang Bin, Wei Qi, et al. Advanced aging-aware STA solution based on Liberate+Tempus[J]. Application of Electronic Technique, 2022, 48(8): 60–64, 69.

## Advanced aging-aware STA solution based on Liberate+Tempus

Ouyang Keqing<sup>1,2</sup>, Wang Bin<sup>1</sup>, Wei Qi<sup>1,2</sup>, Lu Chao<sup>1</sup>, Chen Junhao<sup>3</sup>, Li Mingxiao<sup>3</sup>

(1. Department of Back-End Design, Sanechips Technology Co., Ltd., Shenzhen 518055, China;

2. State Key Laboratory of Mobile Network and Mobile Multimedia Technology, Shenzhen 518055, China;

3. Shanghai Cadence Electronics Technology Co., Ltd., Shanghai 200000, China)

**Abstract:** At the advanced process nodes(7 nm, 5 nm and belows), circuit aging has become a neck problem that restricts chip performance and reliability. The aging effects may cause increasing cell delay, and thus led to the risk of path timing violation. The IC design engineers need to predict the aging timing in the timing analysis and set some aging margin accordingly to ensure the reliable operation of the chip during the service life-time. In view of this, this paper introduces an advanced aging-aware STA solution based on Liberate+Tempus. Evaluation results show that this solution can release the over-designed time margin while keeping the analysis efficiency, the accuracy, as well as the multi-situation analysis capability, thus providing a powerful basis for achieving advanced chip design with higher reliability and better performance.

**Key words:** chip aging; static timing analysis; Tempus; aging-aware STA

## 0 引言

在数字电路物理设计中, 随着晶体管特征尺寸不断减小到 7 nm、5 nm 及以下, 器件性能对老化的敏感度急剧增加, 电路老化已经成为制约芯片性能和可靠性的关键问题。研究表明, 以偏置温度不稳定性(Bias Temperature Instability, BTI)和热载流子效应(Hot Carrier Injection, HCI)为主的老化效应将导致标准单元(可称为 cell)延时增大, 进而产生路径时序违例的风险<sup>[1-3]</sup>。对此, IC 设计工程师需要在芯片物理实现阶段即进行考虑老化的时序分析, 通过设置针对性的时序裕量(margin)来覆盖老化后的恶劣时序场景, 确保芯片在服役期限中可靠运行。在先进工艺芯片设计中, 精确的老化时序分析

并确认合理的 margin 是一个关键问题。偏大的 margin 会导致过设计, 带来额外成本并限制芯片性能, 而偏小的 margin 会导致欠设计, 造成失效泄露的风险。

本文利用基于 Liberate+Tempus 的 aging-aware STA 方案进行先进芯片的老化时序分析, 评估其效率、准确性以及针对多样应用场景的老化时序分析能力。

### 1 芯片物理设计过程中的老化时序分析概述

#### 1.1 老化效应对数字电路时序的影响

芯片老化是指在芯片使用过程中, 各组成部分随着使用时间的增长而出现性能退化的现象。对于物理实现而言, 需要关注的老化效应通常包括: BTI、HCI 和电迁移效应等<sup>[4]</sup>。由于 BTI 和 HCI 会导致路径时序在芯片投

入使用的前几年就发生快速的退化,通常在时序分析时主要关注 BTI 和 HCI 效应。

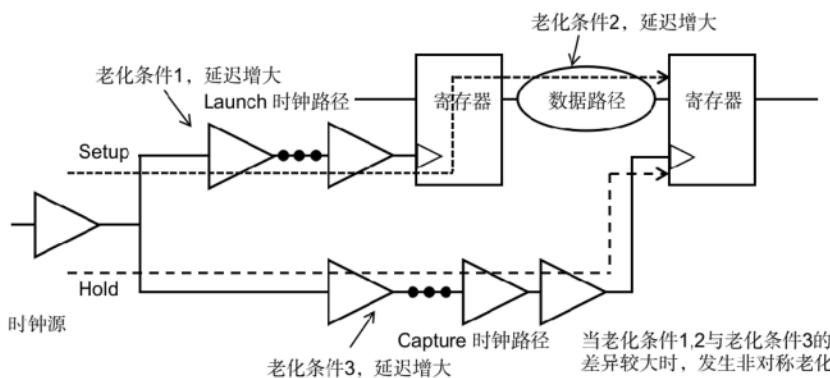

从原理上讲,BTI 和 HCI 都是在电场作用下,晶体管沟道中的载流子迁移到栅氧界面处形成界面态,进而导致阈值电压和漏电流等参数发生变化的过程<sup>[5]</sup>。体现到标准单元时序性能上,则主要导致标准单元的延迟增大,进而导致路径延迟增大。如图 1 所示,当时钟路径和数据路径的延迟均增大时,会导致时序路径时序余量(slack)发生变化,进而影响路径频率。对于那些 slack 较小的路径,更会面临时序违例(slack<0)的风险。

图 1 老化影响路径时序原理图

## 1.2 传统老化时序分析方法和局限性

在先进工艺下,老化效应对路径时序的影响十分明显,需要尽早在设计过程中进行考虑。通常设计师通过两类方法进行路径老化时序分析:基于 SPICE 的时序分析和考虑老化的静态时序分析(aging-aware STA)<sup>[6-8]</sup>。

基于 SPICE 的老化时序分析方法依赖晶体管老化模型获取老化后的晶体管参数,再将其反标入网表,进而开展路径时序仿真。这种方法的精度高,但是效率非常低。由于无法遍历大芯片设计中的每一条路径,设计师通常需要仔细地筛选出设计中的关键路径进行仿真,再基于覆盖 worst case 的原则确定 aging margin,然后将其添加在所有路径的 STA 中进行时序收敛。这样会在大部分路径中引入过设计的 margin,增大时序收敛难度,限制设计性能上限。

传统的 aging-aware STA 基于老化时序库和 STA 工具开展,该方案效率高,能实现覆盖全芯片的时序分析。然而影响晶体管老化程度的因素众多,传统的老化时序库只能覆盖其中一个因素组合场景,若要实现多样化的老化时序分析,需要在 K 库上付出极大代价,因此也无法满足当代针对多样应用场景的老化时序分析需求。

## 2 Liberate+Tempus 先进老化时序分析方案

针对传统老化时序分析方案存在的缺点,本文采用 Liberate+Tempus 老化时序分析方案对芯片设计中的路

径老化时序进行分析。

### 2.1 方案简介

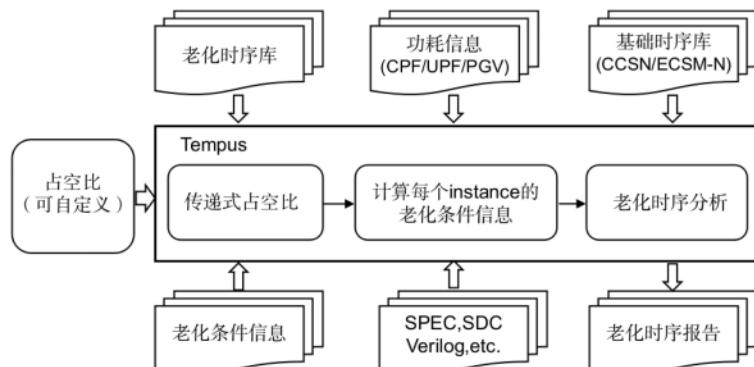

如图 2 所示,该方案基于 Liberate 和 Tempus 的先进功能实现。其中 Liberate 提供老化时序库,与传统方案不同,先进的老化时序库以多种老化影响因素(例如老化电压、老化温度、老化时间、信号占空比、翻转率等)作为输入,能够通过一套库提供针对不同应用场景的标准单元老化时序信息。而借助 Tempus 的强大时序分析能力,Liberate+Tempus 方案也能提供相较传统方案更多的时序分析功能。

本文从设计师对老化时序分析方案的实际需求出发,着重于该方案的时序分析能力验证(对于 Liberate 相关先进功能,不在本文过多介绍),包括:

- (1) 方案的效率、准确性及 margin 释放收益;

- (2) 方案针对多样 mission profile 的分析能力;

- (3) 方案针对多样 workload 的分析能力;

- (4) 方案针对非对称场景的时序分析能力。

图 2 基于 Tempus 的老化时序分析示意图

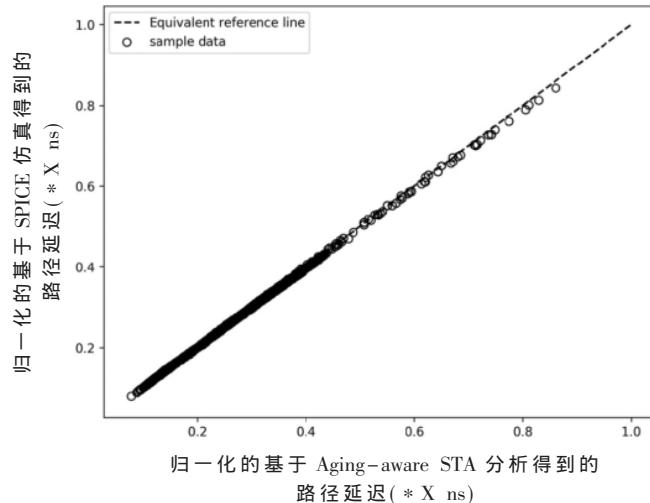

## 2.2 流程效率、准确性以及 margin 释放收益

先进工艺芯片需要设计师进行覆盖全芯片的老化时序分析,并设置合理 margin 来保证设计可靠性。因此对于老化时序分析方案的效率、准确性都有较高的要求。在本部分通过 Tempus aging-aware STA 对 block 时序进行老化分析,并实现 path-by-path 的精准 margin 添加。用到的主要命令是:

```

set_analysis_mode -aging true

```

如图 3 和表 1 所示,当以 SPICE 仿真结果为参照时,两种分析方案得到的路径延迟基本一致,两种方案的相对误差(SPICE to STA)仅有-2.43%~2.15%,表明 aging-aware STA 分析方案有出色的分析精度。而另一方面,SPICE 仿真速度仅为 15 条/h,而 aging-aware STA 可以在 10 min 内完成 570 万条路径的老化分析,展示出巨大的效率收

图 3 Aging-aware STA 与 SPICE 分析结果对照

(图中数据对标相同数值( $X$  ns)进行了归一化处理)

表 1 Aging-aware STA 与 SPICE 分析结果差异分布

| 相对误差/% | 路径数目/条 | 占比/%  |

|--------|--------|-------|

| 2~4    | 5      | 0.21  |

| 0~2    | 1 370  | 57.13 |

| -2~0   | 1 012  | 42.20 |

| -4~-2  | 11     | 0.46  |

注:1) 相对误差算法为: 路径延迟(STA-SPICE)/路径延迟(SPICE)。

益和全芯片时序分析的能力。

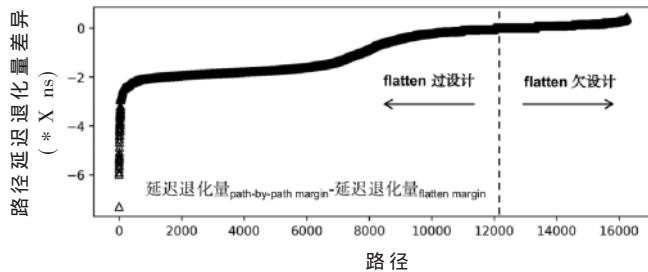

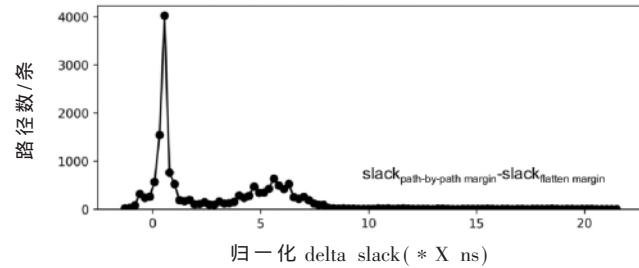

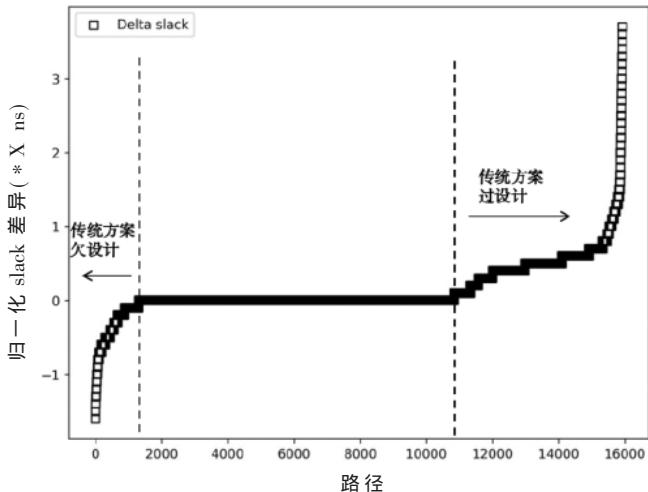

在 margin 释放的收益方面, 这里将全路径添加 5% (flatten margin 5%), 该数值从部分路径的 SPICE 仿真统计结果中获取)时序 margin 的方式与基于 aging-aware STA 的 path-by-path margin 添加方式进行对比。如图 4(a)所示, 添加 flatten margin 在大部分路径中引入了较大的过设计, 归一化过设计量在 0~8\*X ns 之间。并且基于少部分路径获取的 worst case margin 并不能覆盖所有路径, 还有部分路径存在欠设计的可靠性风险, 这部分风险在 path-by-path margin 添加方式下能被有效覆盖。在时序检查方面, 如图 4(b)所示, 设计整体 slack 有明显的下降, 表明对于大多数路径而言, 过设计的 aging margin 得到了释放, STA 收敛难度也随之大幅降低。

(a) 路径延退变化量差异

(数据对标相同数值( $X$  ns)进行归一化处理)

(b) 路径 slack 差值分布

(图中数据对标相同数值( $X$  ns)进行归一化处理)

图 4 添加 path-by-path margin 分析结果与 flatten margin 分析结果对比

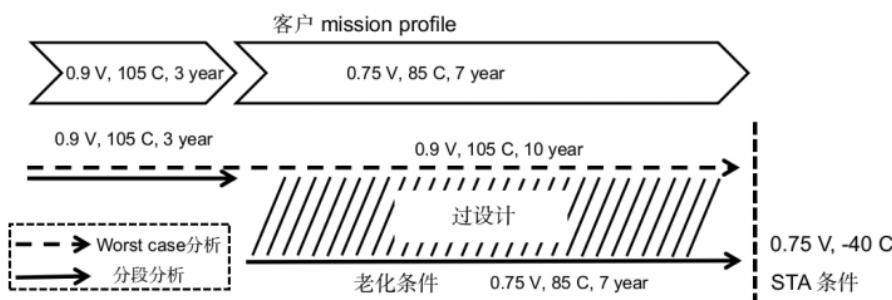

### 2.3 针对多样 mission profile 的分析能力

在芯片的实际使用过程中, 其所处的电压、温度等环境因素往往不是固定的, 为此客户通常会将其划分成多个不同的场景, 并提供 mission profile 以供可靠性工程师作为参考。如图 5 所示, 芯片在 10 年寿命中分别经历高温高压和低温低压的工作场景, 按照传统的 worst case 方式, 将以 10 年高温高压的条件进行仿真来覆盖全部工作场景, 这会引入过悲观的 margin。而通过 Tempus aging-aware STA 可以实现分段的分析方式, 以更贴合 mission profile 的条件作为输入, 进行老化时序分析。此处用到的主要命令是:

```

set multi_segments 1

if {$multi_segments} {create_aging_stress_profile \{ { duration 3 } {**} \} { { duration 7 } {**} }}

```

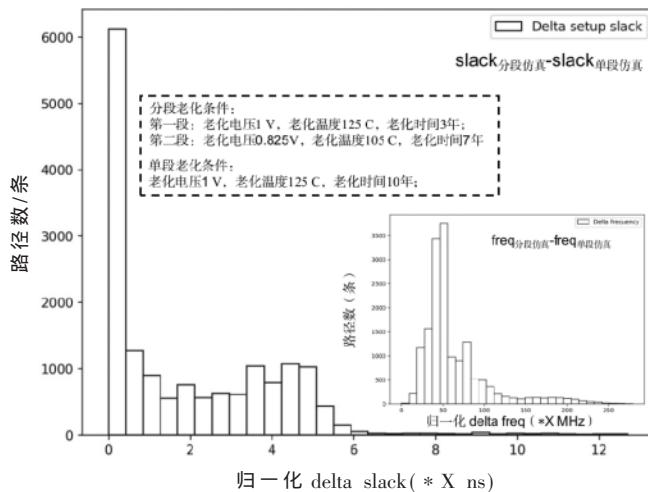

如图 6 所示, 当以 10 年高温高压的分析结果为参照时, 大部分路径基于多段仿真得出的 slack 明显低于前

图 5 针对多样 mission profile 的分析方式示意图

图 6 通过分段仿真与传统单段仿真得到的 slack 差异

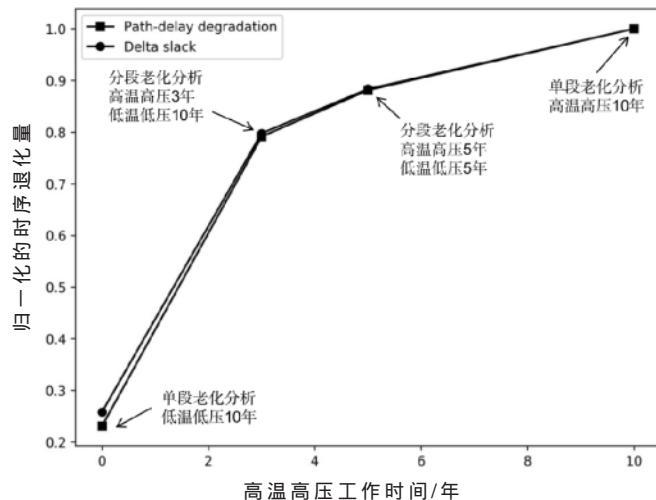

者,归一化 slack 差异在  $0\sim12.7 \times X$  ns 之间,说明该分析方式能降低整体设计收敛难度。图 6 展示通过两种方案得到的频率差异,算法为分段仿真数据-传统仿真数据,图中数据对标相同数值进行了归一化处理。而如图 7 所示,分段仿真的方式能释放更多的 margin,相同路径理论可达频率更高,有利于设计性能的提升。另外,从

图 7 不同高温高压时间下的老化时序退化量

(图中数据对标高温高压 10 年的结果进行了归一化处理)

图 7 中可以看到,路径时序老化的程度主要受到使用过程中高温高压时间的主导,因此对于有升压超频应用场景的芯片,老化导致的路径时序衰退应该得到重点关注。

#### 2.4 多样 workload 分析能力

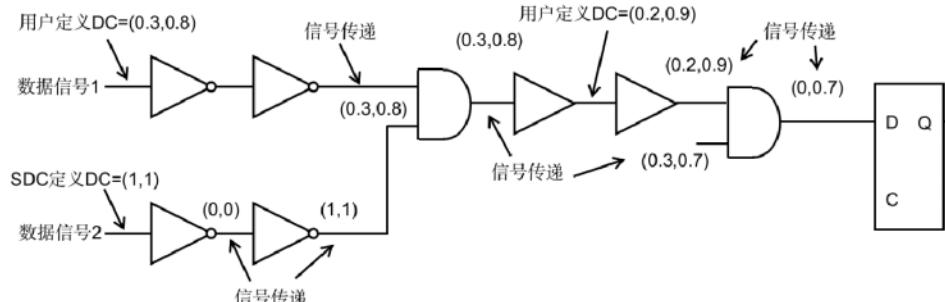

除了电压和温度外,信号占空比也是晶体管老化的的主要影响因素。传统方案受限于单一的老化时序库,常常只能以统计平均的结果为所有 cell 端口施加相同的占空比,分析结果与实际场景存在较大的差异。如图 8 所示,Tempus aging-aware STA 可以依据时序路径中的逻辑传递分析,首先定义全局的占空比参数(大小和模式),然后工具计算得出每个端口的占空比情况,进而基于该场景进行老化时序分析。用到的主要指令为:

```

set_aging_analysis_mode

-min_duty_cy[117]cle 0.0 \

-max_duty_cycle 1.0

-activity_propagation_mode worst/probabilistic

```

另一个与 workload 相关的问题是对 recovery 效应的复现。对于 BTI 而言,当前栅极电场撤去或者反向时,栅氧化界面处的界面态会有一定程度的恢复,因而体现出老化影响恢复的现象(recovery 效应)。在先进工艺下,recovery 效应十分明显,会对老化分析结果会产生很大的影响。这里通过如下指令实现考虑 recovery 效应的老化分析:

```

create_aging_stress_profile{***} -btิ_pmos_scale 0.38 -btิ_nmos_scale 0.56

```

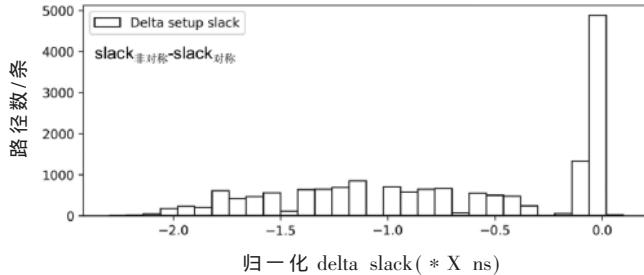

如图 9 所示,对于样本路径,当设置起始端口占空比为 0.5 进行传递时,分析得到的 slack 与将所有 cell 端口占空比固化为 0.5 的分析结果间存在明显差异,大部分路径 slack 差异在  $-0.8\sim1.4 \times X$  ns 之间,最大的 slack 差异可以达到  $3.71 \times X$  ns。可见,精确设置占空比能降低过设计带来的额外代价,也避免了欠设计带来的可靠性风险。图 9 算法为:传递占空比仿真 slack-固化全局占空比仿真 slack。图中数据对标相同数值(X ns)进行了归一化处理。

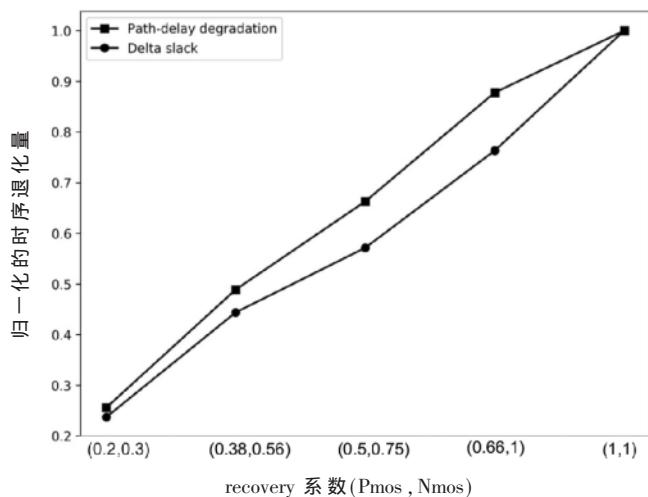

而由图 10 可见,老化导致的路径延迟退化量随着 recovery 折算系数的下降而明显减少,以 NBTI 折算系数 0.38,PBTI 折算系数 0.56 为例,与非 recovery 场景相比,整体的平均时序退化量减少了 48.41%,实现了明显的

图 8 Tempus 对路径占空比传递方式分析示意图

图 9 通过传递占空比与传统固化全局占空比仿真得到的 slack 差异

图 10 不同 recovery 系数下的老化时序退化量

(图中数据对标非 recovery 的结果进行了归一化处理)

时序 margin 释放。需要注意的是, 只有在 cell 翻转时, 才会发生 recovery 效应, 因此对于存在 cell 长期不翻转场景的路径, 不适用考虑 recovery 效应的老化时序分析。

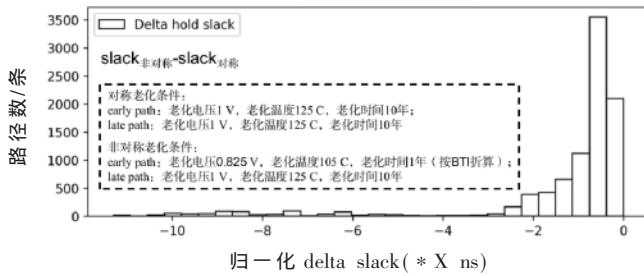

## 2.5 非对称老化时序分析能力

所谓非对称老化是指在一条时序路径上, 路径不同部分老化条件不同的情况<sup>[9]</sup>。例如, early path 和 late path 由于受到 clock gating 或者跨电压域的影响, 导致两边的翻转率或者电压存在较大的差异。相比对称的老化, 这种非对称老化在 early path 和 late path 之间引入了额外的延时差异, 可能会使路径 slack 退化更严重。在可靠性要求较高的芯片设计过程中, 这种场景必须被纳入考虑。这里通过如下指令实现非对称条件下的老化时序分析:

```

create_aging_stress_profile -early { *** }

create_aging_stress_profile -late { *** }

```

如图 11(a)所示, 相对于对称老化场景, 非对称条件

下的 setup 时序明显恶化, 导致路径 slack 减小, 样本路径中的 slack 偏差在  $-2.30 \sim 0*X$  ns 之间。对于 Hold 而言, 通常对称老化对于 slack 的影响较小, 不会出现明显的时序恶化。但是如图 11(b)所示, 非对称老化条件下的 hold slack 也相比对称场景更小, 偏差范围在  $-11.30 \sim 0*X$  ns 之间, 对于 slack 余量较小的路径, 存在 hold 违例的风险。

(a) setup 分析

(b) hold 分析

图 11 非对称与对称老化条件下的时序对比

(图中数据对标相同数值 (X ns) 进行了归一化处理)

## 3 结论

本文导入基于 Liberate + Tempus 的 aging-aware STA 方案对先进工艺芯片进行老化时序评估。结果显示, 该方案可以实现针对不同服役条件的老化时序分析, 并在 STA 过程中实现 path-by-path 的精准时序裕量添加。该方案能在兼顾效率、准确性的同时实现时序裕量释放, 为达成具备更高可靠性和更佳 PPA 的先进芯片设计提供有力依据。

## 参考文献

- [1] MAHAPATRA S, PARIHAR N.A review of NBTI mechanisms and models[J]. Microelectronics and Reliability , 2018 , 81 : 127–135.

- [2] 张春伟, 刘斯扬, 张艺, 等.pMOSFET 的 NBTI 退化机理及内在影响因素[J].东南大学学报(自然科学版), 2015 , 45 (4): 5.

- [3] MUKHOPADHYAY S, GOEL N, MAHAPATRA S.A comparative study of NBTI and PBTI using different experimental techniques[J]. IEEE Transactions on Electron Devices , 2016 : 4038–4045.

(下转第 69 页)

表 3 各 case 功耗组成占比

|         | Case 0  | Case 1  | Case2 |

|---------|---------|---------|-------|

| 总功耗/mW  | 1 117.2 | 1 000.8 | 895.5 |

| 比例/%    | 100     | 89.6    | 80.2  |

| 泄露功耗/mW | 17.4    | 15.4    | 14.6  |

| 内部功耗/mW | 519     | 476.5   | 414.3 |

| 开关功耗/mW | 580.9   | 508.9   | 466.7 |

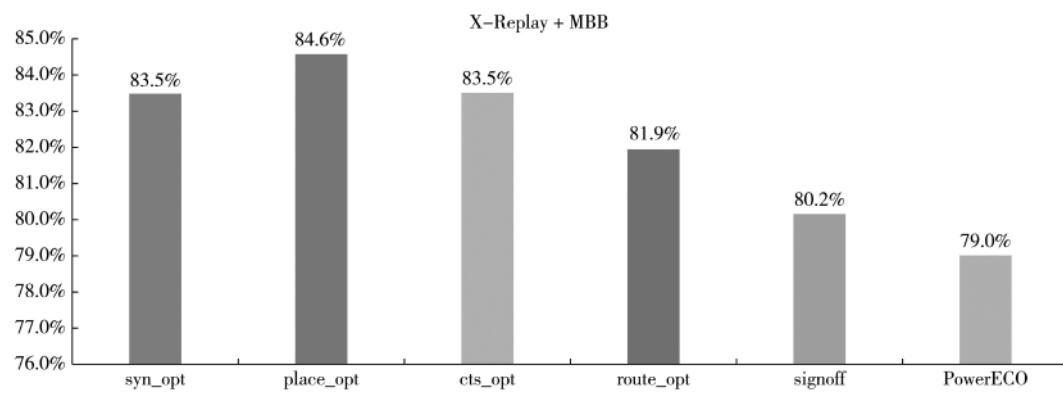

### 4.3 签核流程中功耗优化

为进一步优化功耗,在 Tempus timing signoff 的流程中进行 PowerECO,如图 8 所示,PowerECO 能够进一步优化 1.8% 的功耗,最终全流程功耗优化能够达到 21% 的优化效果。

### 5 结论

综上所述,本文使用了带 FSDB Genus 综合流程,带 FSDB Innovus PR 实现流程,以及 Tempus Power ECO 签核优化流程,并在整个实现与优化流程中结合 MBFF 技术,可以实现从 RTL 到 GDS 的 21% 的功耗优化,这为大

芯片的功耗优化带来全新的选择,为芯片的 PPA 的提升提供了一种全新的方法。

### 参考文献

- [1] Cadence Innovus user guide[EB/OL].[2019-05-11].<http://www.cadence.com>.

- [2] Cadence Genus user guide[EB/OL].[2021-10].<http://www.cadence.com>.

(收稿日期:2022-06-20)

### 作者简介:

顾东华(1982-),男,硕士,硬件总监,主要研究方向:先进工艺下物理设计实现与优化、2.5D 等先进封装设计。

曾智勇(1991-),男,硕士,芯片物理设计主管,主要研究方向:先进工艺下物理设计实现与优化、低功耗设计与优化。

余金金(1987-),男,硕士,资深芯片物理设计主管,主要研究方向:先进工艺下物理设计实现与优化、2.5D 等先进封装设计。

扫码下载电子文档

图 8 Joules-replay + MBB 各阶段功耗优化的比例

(上接第 64 页)

- [4] CUO X , STAN M R.Circadian rhythms for future resilient electronic systems: accelerated active self-healing for integrated circuits[M].Switzerland : Springer , 2020.

- [5] CACHO F , MORA P , ARFAOUI W , et al.HCI/BTI coupled model : the path for accurate and predictive reliability simulations[C]//2014 IEEE International Reliability Physics Symposium(IRPS).IEEE , 2014.

- [6] HUANG K , ZHANG X Q , KARIMI N .Real-time prediction for ic aging based on machine learning[J].IEEE Transactions on Instrumentation and Measurement , 2019 , 68(12) : 4756–4764.

- [7] MISHRA S , AMROUCH H , JOE J , et al.A simulation study of NBTI impact on 14-nm Node FinFET technology for logic applications: device degradation to circuit-level interaction[J].IEEE Transactions on Electron Devices , 2019 , 66(1) : 271–

278.

- [8] KARAPETYAN S , SCHLICHTMANN U .Integrating aging aware timing analysis into a commercial STA tool[C]//VLSI Design , Automation and Test , 2015.

- [9] JAIN P , CANO F , PUDI B , et al .Asymmetric aging : introduction and solution for power-managed mixed-signal SoCs[J].IEEE Transactions on Very Large Scale Integration(VLSI) Systems , 2014 , 22(3) : 691–695.

(收稿日期:2022-06-20)

### 作者简介:

欧阳可青(1981-),男,硕士,工程师,主要研究方向:先进工艺芯片物理实现方法学。

王彬(1996-),男,硕士,工程师,主要研究方向:数字集成电路物理实现。

魏琦(1990-),男,博士,工程师,主要研究方向:数字集成电路物理实现。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所