# 软件无线电架构的导航接收机模拟前端设计

孙金中,付秀兰,高艳丽

(安徽芯纪元科技有限公司,安徽 合肥 230031)

**摘要:** 针对基于超外差或低中频的传统导航接收机模拟前端电路功能复杂、功耗高、不利于单片集成等问题,基于模拟最小化,数字最大化的思想,通过芯片内部集成高增益射频放大器、低功耗的高速模数转换器、低抖动的时钟锁相环,创新性地设计并实现了一款基于软件无线电架构的接收机模拟前端电路。通过 55 nm CMOS 工艺电路设计、版图设计、仿真及硅流片验证,测试结果表明该接收机前端电路各模块功能正常,实现了单个模拟接收通道处理多模导航信号,极大地降低了模拟电路的规模及功耗并成功应用于一款多模导航 SoC 芯片中。

**关键词:** 软件无线电;接收机;放大器;模数转换器;锁相环

中国分类号: TN851

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.222671

中文引用格式: 孙金中,付秀兰,高艳丽. 软件无线电架构的导航接收机模拟前端设计[J]. 电子技术应用, 2022, 48(8): 131-134, 139.

英文引用格式: Sun Jinzhong, Fu Xiulan, Gao Yanli. Design of an analog front-end of navigation receiver based on software defined radio[J]. Application of Electronic Technique, 2022, 48(8): 131-134, 139.

## Design of an analog front-end of navigation receiver based on software defined radio

Sun Jinzhong, Fu Xiulan, Gao Yanli

(Anhui Siliepoch Technology Co., Ltd., Hefei 230031, China)

**Abstract:** The analog front-end of traditional navigation receiver based on superheterodyne or low IF is complex in function, high in power consumption and not conducive to monolithic integration. Based on the idea of analog minimization and digital maximization, a novel analog front-end of navigation receiver based on software radio architecture is designed and implemented by integrating a high gain RF amplifier, a high speed low power ADC and a low jitter clock phase-locked loop. Through 55 nm CMOS process circuit design, layout design, simulation and silicon wafer verification, the test results show that the analog front-end of navigation receiver works normally and only one analog receiver channel is able to process the multimode navigation signals which greatly reduces the size and power consumption of analog circuit. The analog front-end circuit has successfully applied in a multimode navigation SoC chip.

**Key words:** software defined radio; receiver; amplifier; ADC; PLL

## 0 引言

随着信息技术的飞速发展,无线接收机的实现形式也发生了巨大变化,原来的超外差、低中频、零中频架构的无线接收机已经不能满足现代通信、雷达、电子对抗等多频段、多模式及多功能的电子装备的需求,软件无线电架构的接收机因其自身的结构特点,是未来无线通信、多模导航、多功能一体机的理想选择<sup>[1-4]</sup>。

软件无线电架构的接收机的设计难点是设计高性能的接收机模拟前端电路。随着集成电路技术的飞速发展,模数转换器的转换速度越来越高,使得设计单片软件无线电架构的接收机成为了可能<sup>[5-6]</sup>。

本文设计了一款软件无线电架构的接收机模拟前端用于多模卫星导航系统的射频信号接收及转换,从而实现单片软件无线电架构的导航 SoC 芯片。该模拟前端

通过低功耗高速模数转换器直接对导航信号进行射频采样量化转换,在数字域完成频率变换及信号处理,数字电路随着集成电路工艺的进步面积和功耗可以不断降低,由于内部集成了宽带的射频放大器和高速 ADC 可以对不同模式的导航信号全部进行采样量化转换,实现了单个模拟通道完成多模导航信号的处理,从而实现系统终端的最优化设计<sup>[7-9]</sup>。

## 1 电路设计

### 1.1 软件无线电架构的接收机模拟前端设计

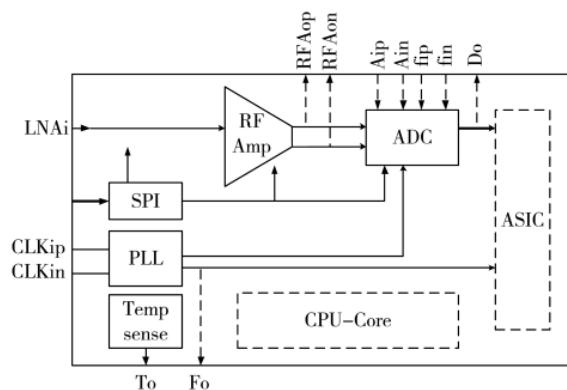

如图 1 所示,本文设计的高性能接收机模拟前端芯片内部集成高增益射频放大器、低功耗高速 ADC、锁相环等,外围只需要搭载天线连接低噪声放大器(LNA)、声表射频滤波器(SAW)、时钟和电源即可完成多模导航卫星射频信号的接收放大滤波及模数转换。该接收机模拟

图 1 接收机模拟前端的系统架构

前端内部只需要加入用于数字信号处理的基带电路及 CPU 电路就可构成单片的多模导航 SoC 芯片。

## 1.2 宽带射频放大器的设计

高性能接收机模拟前端芯片中的射频放大器主要完成导航信号的低噪声放大,使得微弱的导航信号及噪声放大到 ADC 可以完成量化的信号电平值<sup>[10]</sup>。由于不同模式导航信号的频率差异较大,为了满足北斗、GPS、GLONASS 等导航信号的射频放大,该射频放大器的带宽设置为 1.1 GHz 到 1.7 GHz,增益设计为 38 dB。

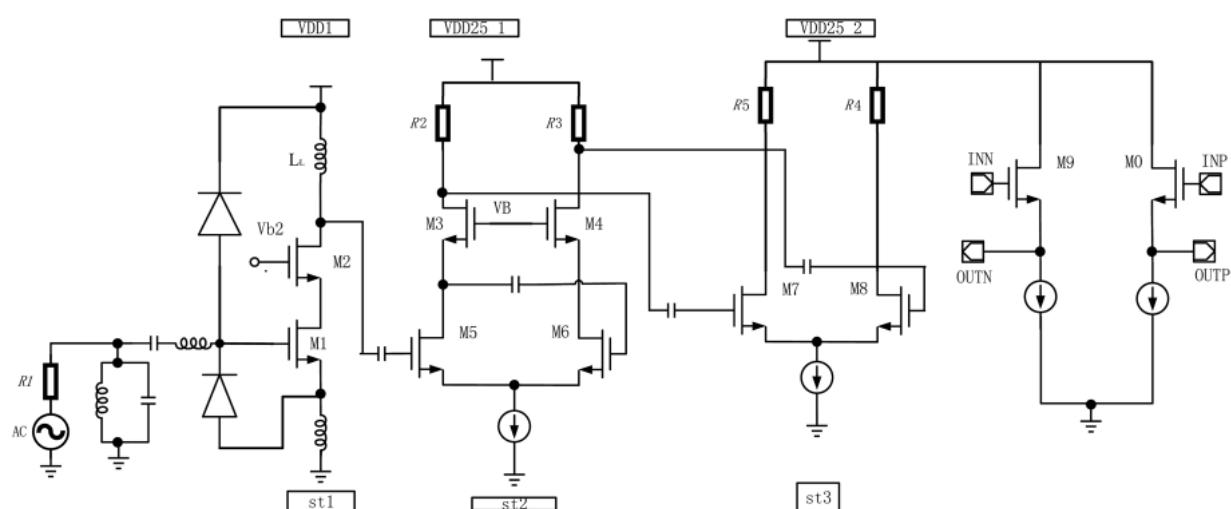

本文设计的射频放大器结构如图 2 所示,放大器包括三级放大器电路和一级输出驱动电路,在第一级的输入还加入了宽带匹配电路,宽带匹配电路全部在片上实现。

## 1.3 低功耗高速模数转换器 ADC 的设计

射频采样 ADC 主要完成射频信号的采样量化,将模拟信号转换成对应的数字信号提供给后端的数字基带处

理电路进行处理。该模块的主要难点是射频采样,由于要量化的信号频率高达 1.5 GHz 以上,如果采用低通奈奎斯特 ADC 需要转换时钟超过 3 GHz,这在具体的电路实现上是十分困难的,而且电路实现所需的功耗、面积也是十分不经济的。然而导航信号的带宽一般在几十兆赫兹以内,根据带通奈奎斯特采样定律,采用欠采样的 ADC 来完成采样量化转换实现具体的电路功能。该 ADC 的模拟全功率输入带宽要包括各模式下的导航信号频率,同时要具有足够的动态范围以满足系统抗饱和的要求,该射频采样 ADC 要实现的具体技术指标为 7 bit/250 MS/s,模拟输入带宽为 2.5 GHz,功耗低于 10 mW。

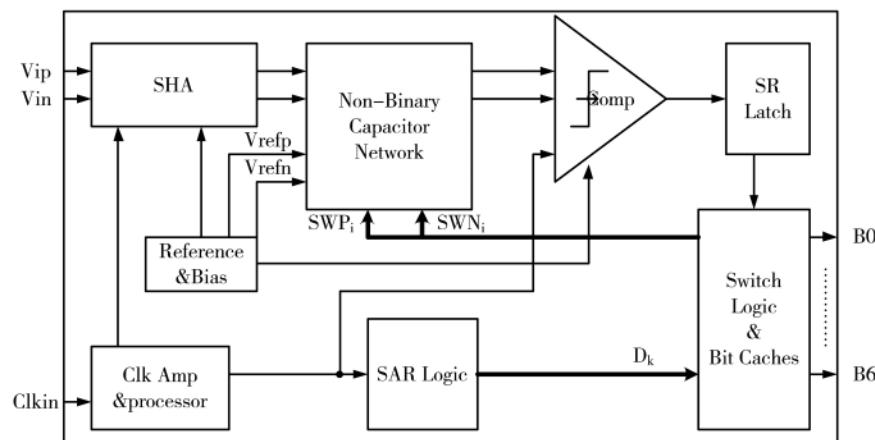

本文设计的高速 ADC 结构框图如图 3 所示,该 ADC 是典型的逐次逼近 SAR ADC 架构,从结构框图可知,该 ADC 可划分成如下电路子模块:宽带采样保持电路、非二进制权重电容 DAC 电路、动态比较器和锁存输出电路、逐次逼近控制逻辑电路和开关电容阵列控制逻辑产生电路、输出控制和驱动电路、时钟放大和处理模块以及基准产生和偏置电路等<sup>[11-12]</sup>。

图 3 射频采样 SAR ADC 结构框图

图 2 射频放大器顶层电路原理图

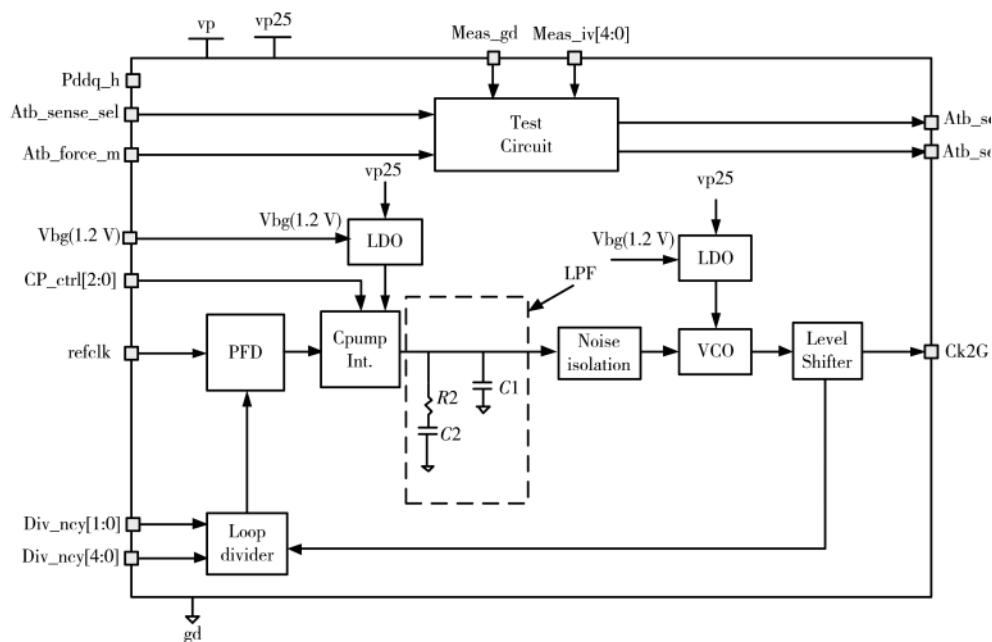

#### 1.4 高性能时钟锁相环的设计

在高性能接收机模拟前端芯片中,锁相环主要产生用于ADC的系统时钟。由于ADC直接对射频信号完成采样量化,时钟信号的质量将限制转换后数字信号的信噪比,因此本SoC芯片中的锁相环需要设计成一个低噪声、性能稳定的锁相环。

本文设计的倍频锁相环结构框图如图4所示,该锁相环由鉴相器(Phase Detector)、电荷泵(Cpump)、环路滤波器、四级压控差分振荡器、相位内插器、电压调节器、时钟选择器、分频器和测试电路组成。采用1.2V/2.5V双电源供电,其中1V主要给鉴相器、分频器等数字电路供电;2.5V电源提供给电压基准源产生出电荷泵、环路滤波器、压控振荡器、相位内插器等模块所需的工作电压。

#### 2 版图设计

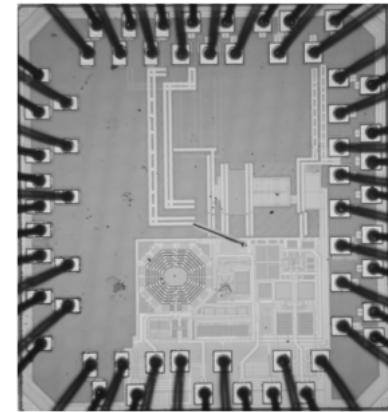

本文设计的接收机模拟前端芯片采用55nm CMOS工艺设计实现,模拟前端内部集成了射频放大器、时钟锁相环、ADC和SPI接口(便于测试)模块,ADC的输出采用LVDS IO输出,整个芯片的大小为1200μm×1320μm。模拟部分采用全定制的版图设计方法,在设计中重点考虑射频放大器和ADC之间的信号隔离及匹配,同时为了降低锁相环时钟信号对射频放大器的干扰,将射频放大器放在最下边,锁相环放在最上面。该芯片的显微照片如图5所示。

#### 3 测试结果

根据上述方案实现的接收机模拟前端芯片采用数模混合集成电路的设计技术,结合超深亚微米VLSI设计技术不仅在功能上全面达到了设计要求,同时在芯片功耗、面积、可测性及使用灵活性方面获得了良好的效果<sup>[13-14]</sup>。基于该接收机模拟前端芯片的系统测试平台综

图5 模拟前端芯片的显微照片

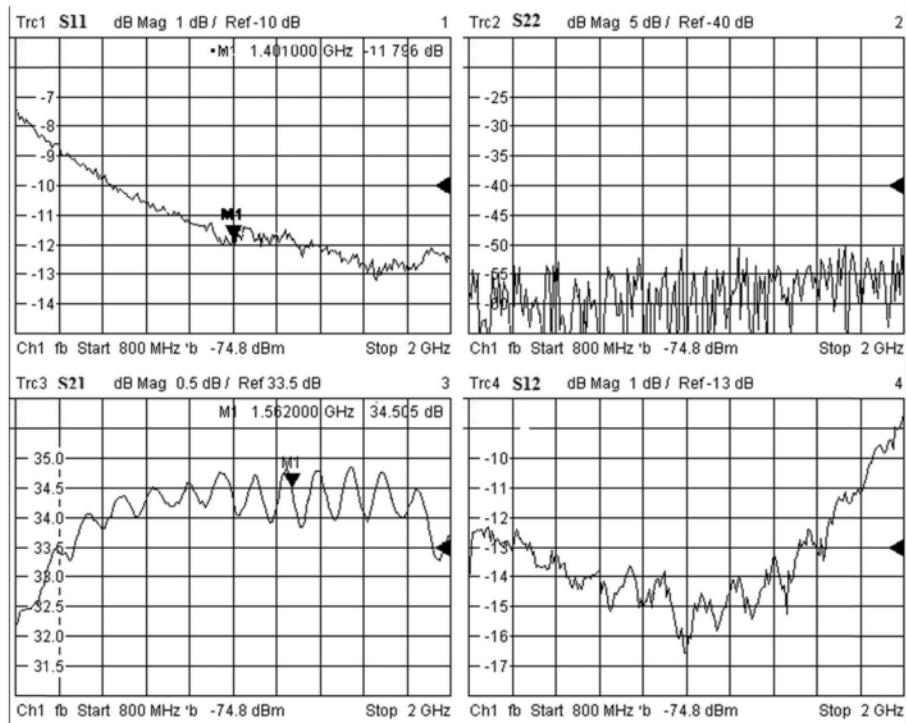

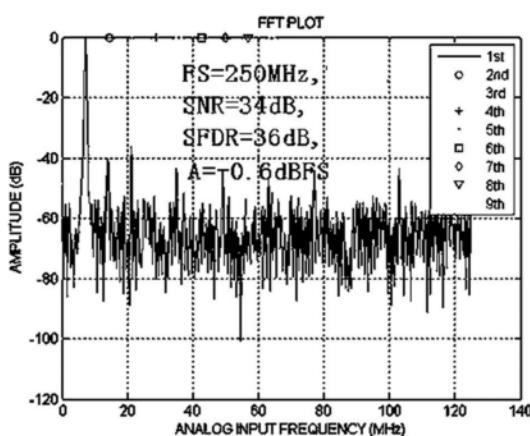

合考虑结构、环境适应性、可靠性、电磁兼容性、长期稳定性等因素。接收机模拟前端系统测试终端如图6所示,射频放大器的S参数测试结果如图7所示。低功耗ADC的测试结果如图8所示。该接收机模拟前端主要测试结果汇总如表1所示。

图6 接收机模拟前端芯片测试终端

图4 锁相环电路结构框图

图 7 S 参数的测试结果

图 8 ADC 的动态测试结果

表 1 模拟前端芯片的测试结果汇总表

|     | 参数                     | 测试值     |

|-----|------------------------|---------|

| 放大器 | 带宽/GHz                 | 1.2~1.6 |

|     | 增益                     | 34      |

|     | 输入反射                   | -12     |

|     | 噪声系数                   | 4.2     |

|     | 1 dB 压缩点               | -4      |

|     | 分辨率/bit                | 7       |

|     | 采样率/(MS/s)             | 250     |

| ADC | 模拟输入带宽/GHz             | 1.6     |

|     | SNDR                   | 34      |

|     | SFDR                   | 36      |

| PLL | 振荡频率/GHz               | 1.5~2.5 |

|     | 积分抖动(10 kHz~25 MHz)/ps | 2       |

#### 4 结论

基于软件无线电架构的接收机模拟前端电路通过电路设计并实现，并已成功应用在多模导航 SoC 芯片中；通过对接收到的卫星导航信号直接射频采样量化转换成对应的数字信号，在数字域完成频率变换，通过单个模拟接收通道处理多个不同频率不同制式的导航信号，极大地降低了模拟电路的规模及功耗。

#### 参考文献

- [1] 刘宁, 马洪涛, 王晓君. ARM+FPGA 的双模导航接收机硬件平台设计[J]. 单片机与嵌入式系统应用, 2017, 17(4): 21~23.

- [2] 李思聪, 王康谊. GPS+BDS 双模的快速定位接收机设计[J]. 单片机与嵌入式系统应用, 2021, 21(11): 89~91.

- [3] 陈玺光, 王尔申, 任旭, 等. 基于北斗导航的无人机系统设计[J]. 电子器件, 2021, 44(5): 1248~1253.

- [4] 王宝平, 余江鑫, 陈卫强. 北斗二代导航接收机的卫星导航系统设计[J]. 单片机与嵌入式系统应用, 2013, 13(7): 40~43.

- [5] 楼才义, 徐建良, 杨小牛. 软件无线电原理与应用[M]. 北京: 电子工业出版社, 2014.

- [6] 林朋飞, 陈少昌. 软件无线电中 ADC 的应用[J]. 电子设计工程, 2017, 25(13): 96~98.

- [7] 曾隆月, 黄继伟, 张常红, 等. 基于 0.13 μm CMOS 工艺的全集成北斗导航射频接收机[J]. 电子器件, 2012, 35(6): 717~722.

(下转第 139 页)

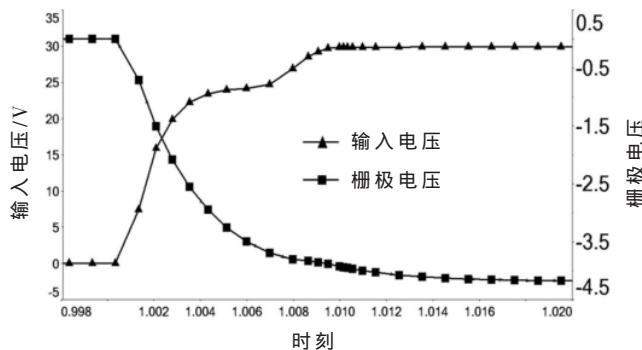

前的浪涌电流如图 10 所示,可知经本文所提方法抑制后的浪涌电流峰值大幅度减小。为准确地检测到开关动作瞬间的电压及电流变化,仿真时需将开关动作时刻设为仿真开始后一段时间,因此图 9、图 10 中的横坐标表示时刻,且在  $t=1$  s 时单刀双掷开关接通负载,由结果可知上述参数选择满足设计要求。

图 10 DC-DC 模块输入电压与 MOS 管栅极电压的变化趋势

#### 4 结论

传统的浪涌电流设计方法源于设计师们的工程经验,采用软启动电路的方法来抑制浪涌电流效果显著,然而在减缓浪涌浪涌电流的同时也引入了二次浪涌电流。经过试验分析可知,浪涌抑制电路的关键元件的参数确定可通过理论与实践相结合的方法来确定,全面考虑整个电路结构的兼容性,根据经验确定大致范围,再经由数学方法求解最优值。

(上接第 134 页)

- [8] 王瑛,严涛.一种基于通用软件无线电平台的低成本导航接收机及其性能分析[C]//第十届中国卫星导航年会论文集-S09 用户终端技术.2019.

- [9] 王佩生,朱家兵,郭二辉.基于 BD、GPS 及 MEMS 的组合导航系统:CN204479757U[P].2015-07-15.

- [10] 郭锐,高艳丽,孙金中,等.一种宽带低噪声放大器设计[J].中国集成电路,2017,26(7):38-41.

- [11] 孙金中,郭锐,高艳丽,等.用于逐次逼近型模数转换器前端的宽带采样保持电路:CN203708221U[P].2014-07-09.

- [12] 付秀兰,孙金中,郭锐,等.高速逐次逼近型模数转换器

#### 参考文献

- [1] 梁斌,朱海龙,张涛,等.星敏感器技术研究现状及发展趋势[J].中国光学,2016,9(1):16-29.

- [2] 钟建勇.CCD 星敏感器电路设计研究[D].成都:电子科技大学,2008.

- [3] 邱燕,王斌,黎颖.一种机载电源浪涌电流抑制电路的设计与分析[J].航空电子技术,2020,51(2):60-64.

- [4] 赵雷,王磊,董仲博,等.星载电子设备浪涌电流抑制以及浪涌电流的测试方法[J].计算机测量与控制,2014,22(9):2730-2732.

- [5] 杜培德,卢翔,鄢毅之.一种机载 DC/DC 浪涌电流抑制电路的设计[J].微电子学,2018,48(2):216-221.

- [6] 张伟,张泰峰,鲁伟,等.基于 MOSFET 适用于母线开关的浪涌抑制电路[J].电源技术,2015,39(10):2222-2224.

- [7] 王益军.一种卫星用浪涌电流抑制电路的设计与分析[J].航天器环境工程,2016,33(1):86-88.

(收稿日期:2021-10-28)

#### 作者简介:

何泽志(1996-),女,硕士研究生,主要研究方向:星敏感器的电磁兼容性分析测试与影响抑制。

钟建勇(1962-),通信作者,男,硕士,研究员级高级工程师,主要研究方向:卫星星敏感器、机载星敏感器、星载相机的电路设计技术。

吴威(1981-),男,博士,副研究员,主要研究方向:星敏感器、FPGA 硬件设计。

扫码下载电子文档

的电容阵列型数模转换器电路:CN105187067A[P].2016-01-27.

- [13] 林广栋,马宏星,朱家兵,等.一款 BD2/GPS 双模导航芯片 Soc 子系统设计方案[J].单片机与嵌入式系统应用,2018(3):59-63.

- [14] 孙金中,谢凤英.一种高速低功耗 LVDS 接收器电路的设计[J].电子科技,2012,25(6):95-97.

(收稿日期:2022-02-23)

#### 作者简介:

孙金中(1983-),男,博士,高级工程师,主要研究方向:模拟及混合集成电路设计。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所