# 存储系统中 L 波段射频直采技术设计与实现

林文成,董郑宇,李琼

(中国电子科技集团公司第五十二研究所,浙江 杭州 310012)

**摘要:** 随着军事科技技术的不断发展,存储关键敏感数据的存储系统在军事领域的重要性越来越突显出来。L 波段作为重要的数据信号工作频段,已广泛运用在卫星导航、警戒雷达、通信侦察等领域。介绍了一种基于 JESD204B 的高速串行总线技术、超低抖动时钟方案及最新高速 ADC 实现 L 波段射频直采,采样率可达 6 GS/s, SFDR(无杂散动态范围)实测可达 67 dBFS 以上,直采数据通过 FPGA 内部进行数字下变频后送给存储单元进行数据存储。

**关键词:** JESD204B; L 波段; 动态范围; 超低抖动

中图分类号: TN957

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.222939

中文引用格式: 林文成,董郑宇,李琼. 存储系统中 L 波段射频直采技术设计与实现[J]. 电子技术应用, 2022, 48(9): 22-26, 31.

英文引用格式: Lin Wencheng, Dong Zhengyu, Li Qiong. Design and implementation of L-band RF direct acquisition technology in storage system[J]. Application of Electronic Technique, 2022, 48(9): 22-26, 31.

## Design and implementation of L-band RF direct acquisition technology in storage system

Lin Wencheng, Dong Zhengyu, Li Qiong

(The 52nd Research Institute of CETC, Hangzhou 310012, China)

**Abstract:** With the continuous development of military science and technology, the storage system for storing key and sensitive data is becoming more and more important in the military field. As an important data signal working band, L-band has been widely used in satellite navigation, warning radar, communication reconnaissance and other fields. This paper introduces a high-speed serial bus technology based on JESD204B, an ultra-low jitter clock scheme and the latest high-speed ADC to realize L-band RF direct acquisition. The sampling rate can reach 6 GS/s, and the measured SFDR can reach more than 67 dBFS, the direct acquisition data is digitally down converted through FPGA and sent to the storage unit for data storage.

**Key words:** JESD204B; L-band; dynamic range; lowest jitter

## 0 引言

按标准的雷达频率命名法<sup>[1]</sup>,L 波段是指 1 000~2 000 MHz 的无线电波波段。按传统实现方式<sup>[2]</sup>,先采用射频模拟下变频模块在模拟端将 1 000~2 000 MHz 变频到 100~1 100 MHz,然后采用低采样率的 ADC 进行信号的采集。此方法由于采用了大量的包括低噪放、滤波器、衰减器和本振电路等模拟器件<sup>[3]</sup>,考虑到模拟器件本身易受干扰和有源器件容易引入噪声等因素,会大大降低系统的无杂散动态范围(Spurious-Free Dynamic Range, SFDR)值,一般只能做到 50~55 dBFS。本文提出了全新的一种真正实现 L 波段全频段射频直采的设计方案,采用超高采样率(采样率达到 6 GS/s)的 ADC 芯片实现射频直采,不但简化了前端的采样电路,而且使 SFDR 提高到了 65~70 dBFS。

## 1 存储系统中的射频采集存储方案

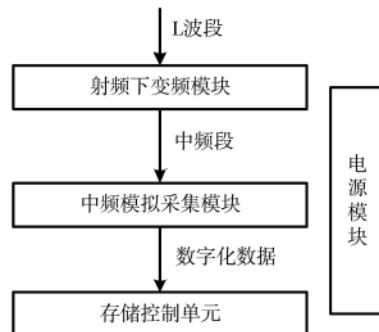

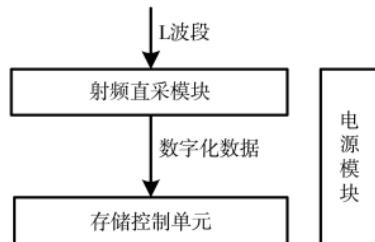

存储系统中传统的射频采集存储方案如图 1 所示。从图 1 中可以看出,方案中主要板卡包括射频下变

图 1 传统数据采集存储方案

频模块<sup>[4]</sup>、中频模拟采集模块、存储控制单元和电源模块等。此方案不但使得存储系统变得复杂,板卡数量较多,同时性能上受到了比较大的影响。

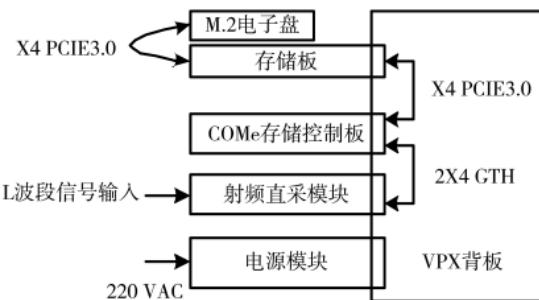

本项目采用如图2所示方案,与图1对比可知,本方案中少了射频下变频模块和中频模拟采集模块,取而代之为射频直采模块,大大降低了前端电路设计的复杂度。另外,射频直采模块主要由单片ADC+FPGA架构组成,硬件成本在5万元左右。两个方案的成本相差大概在7.5万元。

图2 本文采用的数据采集存储方案

根据Nyquist采样定理,  $f_s \geq 2f_h$ <sup>[5]</sup>,为了实现L波段的全频段射频直采,采样率需要满足  $f_s \geq 4000$  MHz,为了得到更好SFDR性能,本文将采用  $f_s = 6000$  Mz来实现L波段的全频段射频直采。本文采用ADC芯片为ADI公司的AD9213BBPZ-10G。该芯片支持最大的采样率为10.25 GS/s,量化位数为12 bit,最大接收带宽为6.5 GHz(-3 dB),SFDR值为70 dBFS,接收带宽满足L波段的设计需求。下面描述具体设计实现方案。

## 2 射频直采方案硬件设计

### 2.1 时钟电路

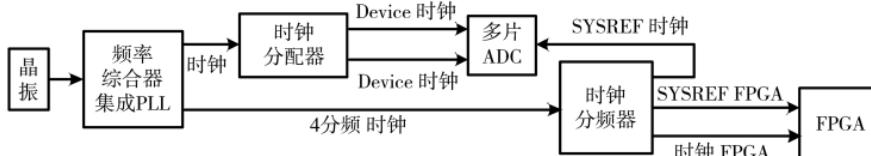

传统时钟电路采用超低抖动自带有支持JESD204B<sup>[6]</sup>总线的专用时钟芯片实现,但是目前采样率已达6 GS/s以上,市面上单片的时钟芯片解决方案已无法满足需求,需要采用多芯片级联构建的方式实现,具体实现框图如图3所示。

多芯片级联构建电路有如下特点:

- (1)支持JESD204B总线。

- (2)输出的频率范围灵活可调,输出范围更宽。既能兼容单芯片的方案,也能满足采样率不断提高的使用要求。

- (3)具备高可塑性,通过简单的模块更换,可以实现更高频率的输出,满足不同项目的不同采样率的使用需求。

频率综合器采用ADI公司的ADF4372,单芯片集成锁相环(Phase-Locked Loop, PLL),超低抖动值(38 fs)<sup>[7]</sup>,

图3 时钟电路原理框图

输出通道有3路,其中一路最高输出频率为16 000 MHz,剩余两路最高输出频率为8 000 MHz,内部集成固定分频比电路,分别是1/2/4/8/16/32/64。本设计中,采样率设计为6 GS/s,ADF4372输出1路Device Clock给时钟分配器,由分配器分成多路Device Clock送给多片ADC作为ADC的采样时钟。时钟分配器采用ADI公司的HMC987,支持最高工作频率为8 000 MHz,可以将1路时钟通过内部分配输出9路时钟。

时钟分频器采用TI公司的LMK04828,LMK04828时钟芯片是一款专用的JESD204B超低抖动时钟芯片,Device Clock和SYSREF Clock是成对输出的。由于其最高输出频率只能达到3 080 MHz,无法满足本项目的需求,但是可以运用其内部的分频电路和SDCLK和DCLK是成对输出的特性,作为Clock FPGA和SYSREF FPGA的输出接口。

前端采用高频率稳定度的晶振,晶振频率为100 MHz,频率稳定度达0.5 ppm。

整个电路工作原理如下:晶振产生的时钟输入给频率综合器,频率综合器产生两路时钟,分别为6 000 MHz和1 500 MHz,6 000 MHz送给时钟分配器,分配给多个ADC使用,1 500 MHz送给时钟分频器,输出SYSREF Clock、SYSREF FPGA、Clock FPGA分别给ADC和FPGA使用。此电路设计既保证了各时钟的同源性,又满足了ADC采样时钟和JESD204B总线对不同频率时钟的需求。

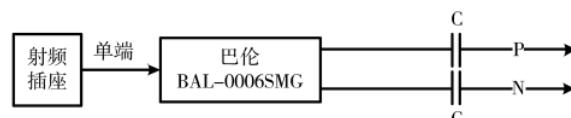

### 2.2 射频采集电路

本文采用ADI公司生产的最新ADC器件AD9213-BBPZ-10G,为了减少前端模拟电路对采样性能的影响,整个前端电路采用以巴伦为主要器件的无源器件搭建而成,如图4所示,巴伦为一种三端口器件,实现将匹配输入转换为差分输出而实现平衡传输线电路与不平衡传输线电路之间的连接的宽带射频传输线变压器<sup>[8]</sup>。

图4 前端采集原理框图

输入的射频信号通过巴伦转换为差分信号后,再通过交流耦合电容送给ADC器件,耦合电容的值需要依据实际工作频率值进行选取。公式如下:

$$C = \frac{1}{2 \times \pi \times f \times Z_c} \quad (1)$$

其中  $f$  为最小工作频率;  $Z_c$  为电容中的等效串联电阻 (ESR), 一般小于  $1\Omega$ 。L 波段电路中优选 COG(NPO) 材质的大封装电容, 大封装尺寸的比小封装尺寸的电容频率特性要好。

### 2.3 FPGA 处理电路

ADC 器件的后端接入现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA), FPGA 选用 Xilinx 公司的 VIRTEX 7 系列 690T 芯片。为了保证在全带宽模式下正常工作, 将 ADC 的 16Lane 接入 FPGA 的 GTH 总线上。VIRTEX 7 系列 690T 芯片最多含有 80 GTH 收发器, 最高速率支持 13.1 Gb/s, 满足 JESD204B 总线 7.5 Gb/s 的总线速率要求。

### 3 射频直采方案软件设计

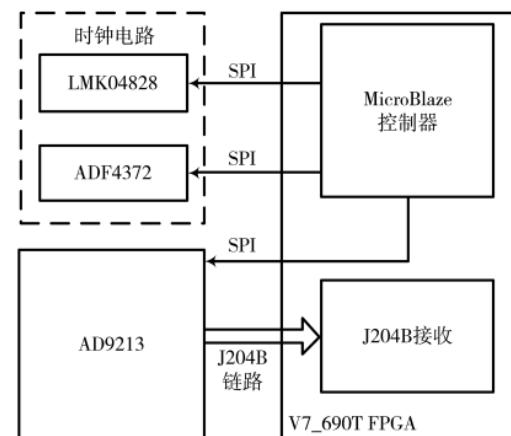

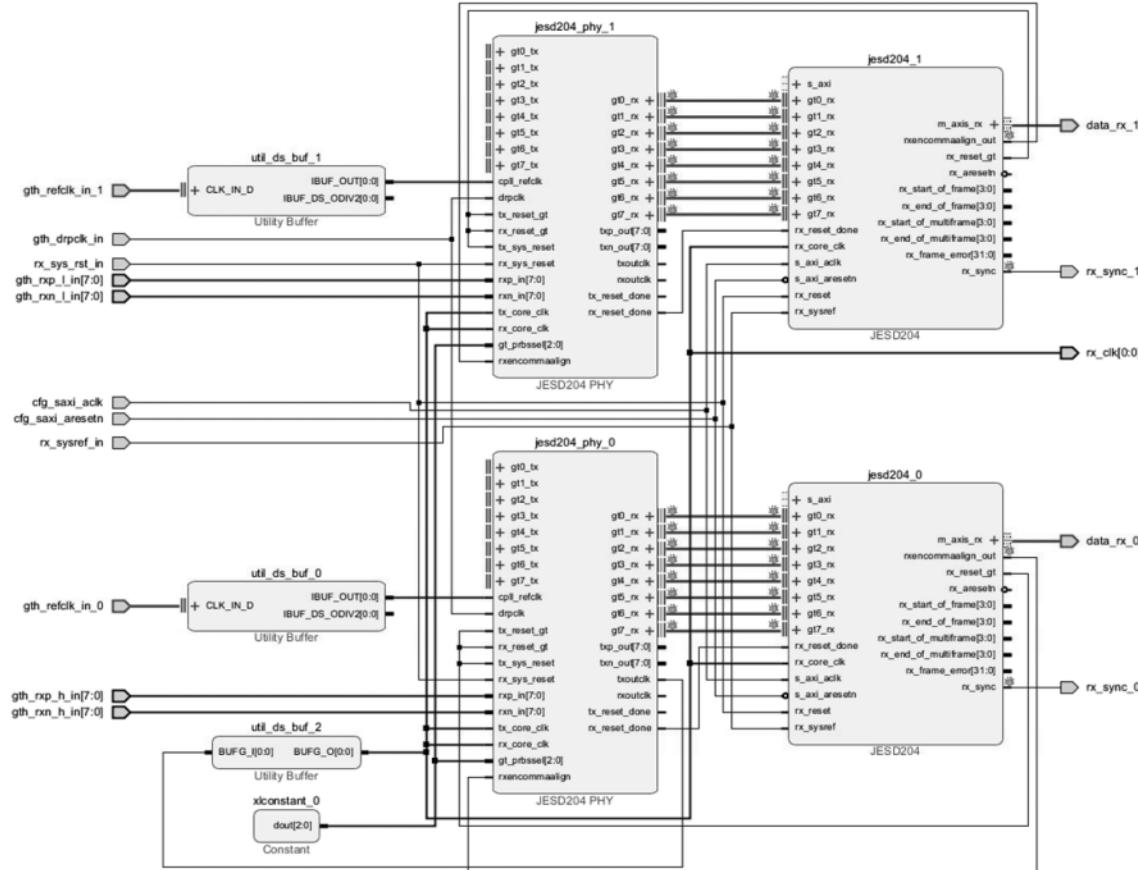

如图 5 所示,本系统通过在 V7\_690T FPGA 内嵌入 MicroBlaze 处理器软核并运行配置控制程序实现对时钟芯片 ADF4372、LMK04828 和 ADC 芯片 AD9213 进行配置控制。利用 Xilinx JESD204 IP 核搭建如图 6 所示的 Block Design 框图<sup>[9]</sup>,实现与 AD9213 JESD204Bx16 接口对接,接口协议采用 JESD204B Subclass1。

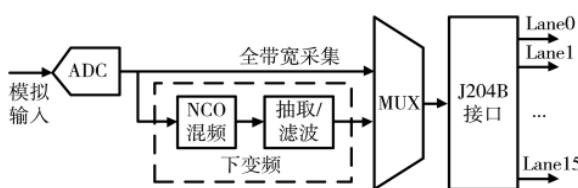

AD9213 内部结构简图如图 7 所示, 其内部自带数字

图 5 系统实现简图

下变频(Digital Down Converter, DDC)功能模块, 使用时可以根据需求配置相关寄存器选择 JESD204B 输出数据源。AD9123 可以预设 16 种固定中心频率, 通过 GPIO 或者 SPI 寄存器进行切换, 此种切换不需要对 JESD204B 链路重新进行同步, 若需要设置其他非预设的中心频率, 则需要对 JESD204B 链路进行重新同步操作, 整体响应时间较慢。本设计为了灵活配置中心频率且加快响应速度, 使 AD9123 工作在全带宽采集模式下, 在后端的 FPGA

图 6 FPGA\_JESD204Bx16 接收端 Block Design 框图

图 7 AD9213 内部结构简图

中实现 DDC 功能。

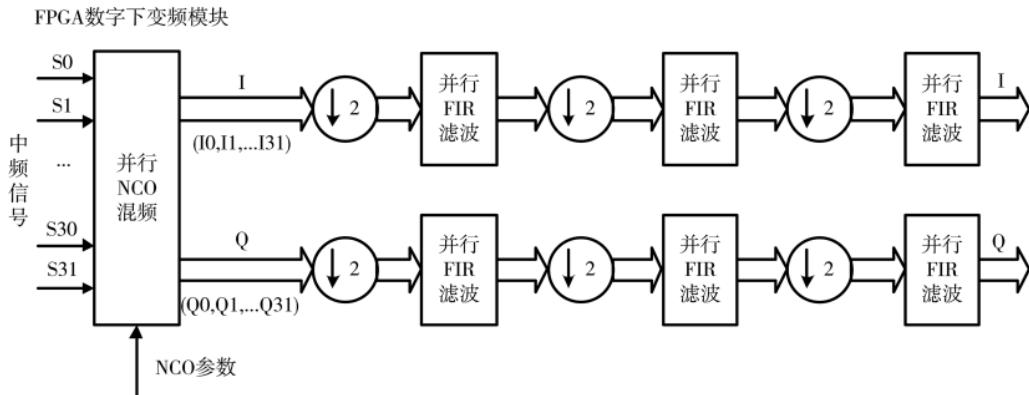

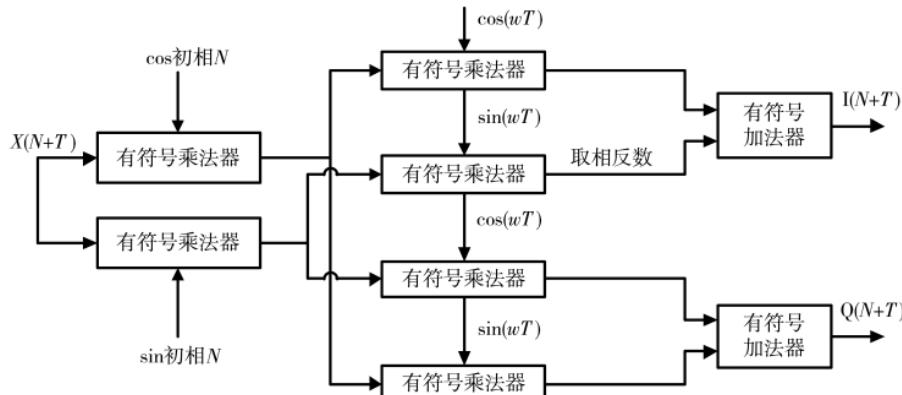

对 JESD204B 接收的数据按照 JESD204B 协议标准帧组成格式进行解析即可得到原始采集的中频信号。FPGA 端实现 DDC 功能框图如图 8 所示, 由于 AD9213 的采集带宽较大, 若按照典型的单路数据进行混频运算势必需要非常高的时钟频率, 故需要采用并行 NCO 混频设计, 然后对混频后的 I、Q 数据结果进行并行滤波、抽取。根据使用效果将不同的 NCO 混频参数传递至并行混频模块即可实现动态切换中心频率的效果。

并行 NCO 混频算法实现的原理推导过程如下<sup>[10-11]</sup>:

典型的混频运算数学公式如下:

$$y(n) = x(n) \times e^{-j2\pi n \times \frac{F_c}{F_s}} \quad (2)$$

其中  $F_c$  表示中心频率,  $F_s$  表示采样频率。

当采样数据按照并行输入时, 令  $n=k+n'S$  ( $k$  为某时刻的并行点序号,  $k=1, 2, 3, \dots, S$ ;  $S$  为并行采样点个

数), 则可得到如下公式:

$$\begin{aligned} y(k+n'S) &= x(k+n'S) \times e^{-j2\pi(k+n'S) \times \frac{F_c}{F_s}} \\ &= x(k+n'S) \times e^{-j2\pi(k+n'S) \times \frac{F_c}{F_s}} \times e^{-j2\pi n' \times \frac{F_c}{F_s/S}} \end{aligned} \quad (3)$$

对上式进行三角函数展开即可得到如图 9 所示的算法框图的计算过程。

#### 4 系统性能分析和实测

在存储系统中, 将前端射频直采的数据送至存储控制单元进行存储, 并通过存储控制单元的网络接口, 可以将已存储的数据进行快速地卸载到分析设备中, 以便于后续的数据分析和处理。当对 1 路射频模拟信号进行直采时, 采样率  $f_s$  采用 6 000 MS/s, 在 1 000 MHz 进行全带宽采集时, 记录的存储带宽计算可得:  $6000 \text{ MS/s} \times (12 \text{ bit}/8) = 9000 \text{ MB/s}$ , 单路的存储带宽为 9 000 MB/s; 单路按 1 000 MHz 带宽进行数字下变频后所得 I/Q 数据 (抽取倍数 4 倍, 采样率下降到 1 500 MS/s) 可得采集存储带宽为  $9000/4 \times 2 = 4500 \text{ MB/s}$ 。

整个系统选用 Intel i7 CPU 控制器+FPGA 可编程逻辑器件作为主控元件。采用基于 FPGA 的高速串行总线和 PCIE 互连技术的高性能存储系统构架实现数据的快速传输。详细实现框图如图 10 所示。

FPGA 自带的 GTH 高速串行总线接口按 8.0 Gb/s 速率进行传输, 每组 GTH X4 接口传输带宽理论可达

图 8 DDC 算法原理框图

图 9 并行 NCO 混频算法框图

图 10 详细系统框图

4 GB/s, 按 RapidIO 协议工作时的损耗, 1 组 X4 接口实际传输带宽具备 3.2 GB/s 传输能力, 射频直采模块用 2 组 X4 RapidIO 接口的存储带宽可达 6 400 MB/s, 满足前端 4 500 MB/s 的采集存储带宽。

射频直采模块将数据送往存储控制单元, 存储控制单元主要由 Intel i7 CPU 控制器和 m.2 电子盘组成, m.2 电子盘采用 PCIE3.0 X4 接口完成高速的数据存储。PCIE3.0 按 8 Gb/s 速率进行传输, 一组 PCIE3.0 X4 接口传输带宽理论可达 4 000 MB/s, 按 64% 效率进行计算, 其实际可用带宽为 2 560 MB/s, 因此采用 2 组 m.2 电子盘的存储带宽可达 5 120 MB/s, 满足前端 4 500 MB/s 的存储带宽。因此整个系统的采集处理和存储同步进行时, 实时效率可达 100%, 能将采集的数据实时完全地存储下来。

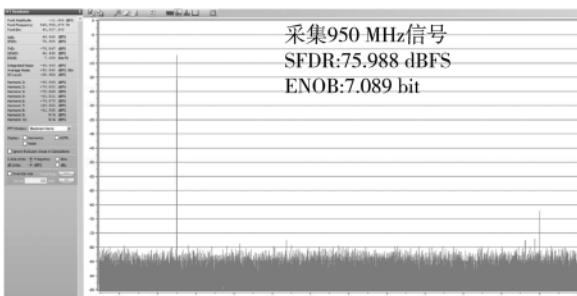

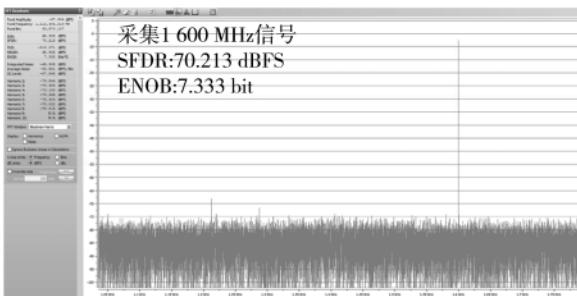

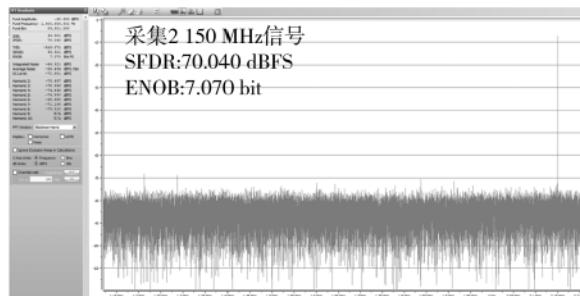

系统实际测试的数据如图 11~图 13 所示, 图中为 L 波段不同频点的射频直采频谱图, 从图中可以看出, 采用本文的射频直采方案, 可以将 SFDR 值提高到 67 dBFS~75 dBFS, ENBO 可达 7.0 bit~7.3 bit。

图 11 950 MHz 频点的性能图

图 12 1 600 MHz 频点的性能图

图 13 2 150 MHz 频点的性能图

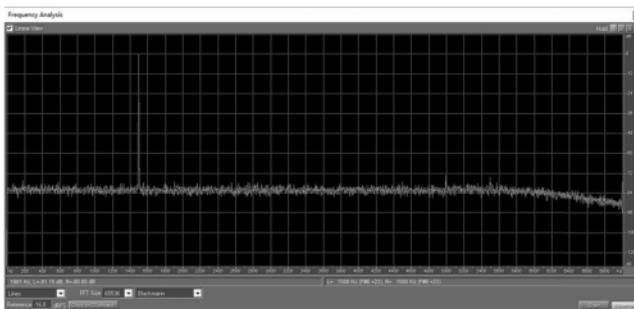

另外通过 DDC 算法后的数据的性能如图 14 所示, SFDR 性能可达 70 dB 以上, ENBO 可达 7.3 bit。

图 14 DDC 性能实测图

经过对系统性能的测试, 可以看出本文设计的 6 S/s 波段射频直采的存储系统在全频段上的 SFDR 值依然能保持在 67 dBFS 以上, 可见系统具有良好的采样存储性能。本文采用了高性能的 ADC、简单的前端电路设计及低抖动的时钟电路等设计方案, 最终实现高性能的 L 波段射频直采的存储系统。

## 5 结论

本文介绍一种运用在存储系统中的 L 波段射频直采设计和实现方案, 对整体的硬件方案、软件方案分别进行阐述, 最后对系统的性能指标进行实际测试, 测试结果表明了系统的良好性能。另外, 整个方案在减少系统复杂度、降低硬件成本的同时, 提高系统的 SFDR 值, 为存储系统提供更加纯净的信号数据, 同时也更有利于后续的数据分析处理。

## 参考文献

- [1] SKOLNIK M I. 雷达手册 [M]. 王军, 林强, 米慈中, 等译. 北京: 电子工业出版社, 2003.

- [2] 周苏萍. 基于 P 和 L 频段射频前端关键电路研究 [D]. 杭州: 杭州电子科技大学, 2011: 4~32.

- [3] 施福刚. L 波段收发组件的设计与实现 [D]. 成都: 电子科技大学, 2011: 37~39.

- [4] 安照辉. L 波段大动态范围的雷达接收机设计 [D]. 成都: 电子科技大学, 2017: 7~17.

- [5] ALAN V, OPPENHEIM A S, WILLSKY S, et al. 信号与系

(下转第 31 页)

法虽然能够有效提高非线性系统目标跟踪的精度,但目前只是在高斯噪声的环境下进行处理,若系统是在非高斯的环境下,则可能出现较大误差,笔者将会继续对非高斯的环境下算法的应用进行研究和改进。

## 参考文献

- [1] 朱洪峰,熊伟,崔亚奇,等.新的自适应转弯模型的IMM算法研究[J].计算机工程与应用,2019,55(17):252-258.

- [2] 何友,修建娟,关欣.雷达数据处理及应用[M].北京:电子工业出版社,2013.

- [3] ROONIZI A K.An efficient algorithm for maneuvering target tracking(Tips & Tricks)[J].IEEE Signal Processing Magazine,2021,38(1):122-130.

- [4] 齐立峰,惠小平.转弯机动目标跟踪算法研究[J].现代雷达,2014,36(9):40-43.

- [5] 程遥,吕植勇.基于自适应转弯模型的交互式多模型算法研究[J].武汉理工大学学报:交通科学与工程版,2020,44(2):369-372.

- [6] LIU Z X,WU D H,XIE W X,et al.Tracking the turn maneuvering target using the multi-target Bayes filter with an adaptive estimation of turn rate[J].Sensors,2017,17(2):373.

- [7] ZHU H,XIONG W,CUI Y,et al.Research on IMM algorithm of new adaptive turn model[J].Computer Engineering and Applications,2019,55(17):252-258.

- [8] LI X R,JILKOV V P.Survey of maneuvering target tracking. Part I.Dynamic models[J].IEEE Transactions on Aerospace & Electronic Systems,2004,39(4):1333-1364.

- [9] 于红娟,牛竹云,张春涛,等.基于变结构多模型的机动目标跟踪算法[J].火力与指挥控制,2012(S1):36-39.

- [10] WANG H,KIRUBARAJAN T.Precision large scale air traffic surveillance using IMM/assignment estimators[J].IEEE Transactions on Aerospace and Electronic Systems,1999,35(1):

(上接第 26 页)

- 统[M].刘树棠,译.北京:电子工业出版社,2003.

- [6] JESD204B.01,Serial Interface for data converters[S].JEDEC,2011-07.

- [7] DELOS P.Phase-locked loop noise transfer functions.high frequency electronics[Z].2016.

- [8] 祝毅.室内定位系统 L 波段射频前端设计与实现[D].哈尔滨:哈尔滨工业大学,2015:16-32.

- [9] JESD204 v7.2 LogiCORE IP product guide[Z].Xilinx,2017-10.

- [10] 杜勇.数字滤波器的 MATLAB 与 FPGA 实现[M].北京:电子工业出版社,2019.

255-266.

- [11] 彭志刚,李宝鹏,李大龙.基于 LMS 的多模型高机动目标跟踪方法[J].火力与指挥控制,2020,45(12):111-114,120.

- [12] 宁倩慧,张艳兵,刘莉,等.扩展卡尔曼滤波的目标跟踪优化算法[J].探测与控制学报,2016,38(1):90-94.

- [13] 温镇铭,刘松涛,姜宁.基于改进 UKF 的蛇形机动目标跟踪方法[J].电光与控制,2020,27(9):9-13,23.

- [14] 马晓杰,林雪原,孙巧妍,等.一种改进的 UKF 滤波算法在 BDS/SINS 组合导航系统中的应用研究[J].大地测量与地球动力学,2021,41(4):351-356.

- [15] 符强,赵鸿悦,孙希延,等.改进的强跟踪 UKF 在组合导航中的应用研究[J].计算机仿真,2021,38(2):29-33.

- [16] 马野,王孝通,戴耀.基于 UKF 的神经网络自适应全局信息融合方法[J].电子学报,2005,33(10):1914-1916.

- [17] 于耕,方鸿涛.基于 BP 神经网络改进 UKF 的组合导航算法[J].电子技术应用,2019,45(4):29-33.

- [18] 赖福天.机动目标跟踪方法研究[D].西安:西安电子科技大学,2020.

- [19] 刘国情,王锐,袁俊泉,等.基于改进当前统计模型的容积卡尔曼滤波算法[J].空军预警学院学报,2018,32(1):55-60.

(收稿日期:2022-06-14)

## 作者简介:

李盈萱(1997-),女,硕士研究生,主要研究方向:高速运动平台机动目标跟踪。

王中训(1965-),男,博士,教授,主要研究方向:信源信道编码。

董云龙(1974-),男,博士,教授,博士研究生导师,主要研究方向:雷达信息处理、多传感器信息融合。

扫码下载电子文档

- [11] 王森.宽带数字信道化接收机 FPGA 实现技术研究[D].成都:电子科技大学,2008.

(收稿日期:2022-05-06)

## 作者简介:

林文成(1984-),通信作者,男,硕士研究生,高级工程师,主要研究方向:智能采集处理存储系统,E-mail:linwencheng@cetc.com.cn。

董郑宇(1994-),男,硕士研究生,工程师,主要研究方向:高速模拟信号采集和存储技术。

李琼(1989-),男,硕士研究生,工程师,主要研究方向:高速模拟信号采集和存储技术的控制软件。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所