# 一种基于 MCU 芯片的 FPGA 原型验证平台设计

张文文, 唐映强

(无锡中微爱芯电子有限公司, 江苏 无锡 214072)

**摘要:**为了缩短 MCU 芯片开发周期,提出了一种基于 MCU 芯片 FPGA 原型验证平台设计。该设计是将传统 FPGA 原型验证过程中使用 FPGA 的 RAM 原型替换程序存储单元,改为使用 FPGA 双端口 RAM 替换。其中一个端口控制按照传统的接入方法,另一端口控制信号接到专门的控制逻辑上,独立控制,而且不影响原 MCU 芯片功能。该方法不仅节省多次 FPGA 综合实现的时间,而且可以灵活实时监测 RAM,方便查错。同时该方法具有通用性,可移植到类似的 SoC 系统架构 FPGA 原型验证系统中去。

**关键词:**MCU 芯片;FPGA 原型;验证平台;双端 RAM;可复用

中图分类号: TP368.1

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.222635

中文引用格式: 张文文, 唐映强. 一种基于 MCU 芯片的 FPGA 原型验证平台设计[J]. 电子技术应用, 2022, 48(9): 59–62.

英文引用格式: Zhang Wenwen, Tang Yingqiang. A FPGA prototype verification platform design based on MCU chip[J]. Application of Electronic Technique, 2022, 48(9): 59–62.

## A FPGA prototype verification platform design based on MCU chip

Zhang Wenwen, Tang Yingqiang

(Wuxi i-CORE Electronics Co., Ltd., Wuxi 214072, China)

**Abstract:** In order to shorten the development cycle of Microcontroller Unit(MCU) chip, this paper proposes a Field Programmable Gate Array(FPGA) prototype verification platform design based on MCU chip. The design is to change the FPGA Random Access Memory(RAM) IP replace program storage unit used in the traditional FPGA prototype verification process into the FPGA dual port RAM IP. One port is controlled according to the traditional method, and the other port control signal is connected to the special control logic for independent control without affecting the function of the original MCU. The method not only saves the times of multiple FPGA synthesis, but also can monitor RAM in real time, which is convenient for error detection. At the same time, this method is universal and can be transplanted to FPGA prototype verification based on similar System on Chip(SoC) architecture.

**Key words:** MCU chip; FPGA prototype; verification platform; dual port RAM; reusable

## 0 引言

随着对各种功能微控制单元(Microcontroller Unit, MCU)芯片的市场需求增加,怎么缩短 MCU 芯片开发周期成为抢占市场一个关键难点。MCU 芯片验证在研发中所占的比例越来越重,占据了整个研发周期的 70%以上,缩短验证周期就是直接有效的办法<sup>[1-3]</sup>。通常进行前仿真验证功能,后仿真验证时序性能,而仿真速度太慢,在遇到问题改设计后,如果只选择验证修改部分的功能,验证覆盖率达不到会减小流片的成功率。

用现场可编程逻辑门阵列(Programmable Gate Array, FPGA)验证功能可以比软件仿真速度高出 4~6 个数量级<sup>[4]</sup>,填补了仿真环境与实际芯片的巨大差距。对于仿真时间限制不能遍历的情况,FPGA 原型验证都可以轻松完成。同时,FPGA 可以给软件设计人员提供硬件验证平台,软件和芯片同时开发可以加快产品的面市时间。

综上可见 FPGA 原型验证平台<sup>[5-7]</sup>的构建在整个开发过程的重要性。如何快速构建 FPGA 原型验证平台,使其能担此重任,正是本设计的初衷。

## 1 FPGA 原型验证平台架构

FPGA 原型验证的原型指的就是专用集成电路(Application Specific Integrated Circuit, ASIC)。本文针对的是 MCU 芯片,其特点是内部带有一个微控制器即 MCU 核心,是一个小型的片上系统(System on Chip, SoC)。

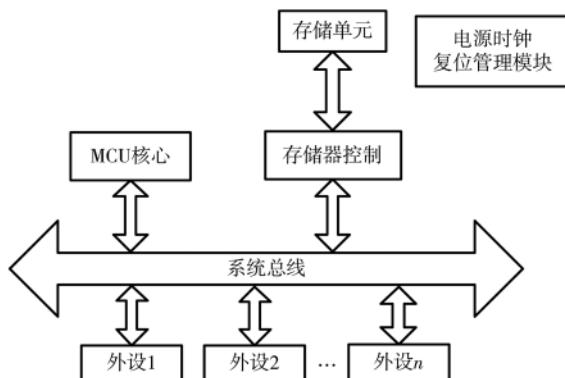

图 1 所示为 MCU 芯片的系统架构组成图。MCU 芯片的系统组成一般包括:MCU 核心、系统总线、存储控制器及存储单元、电源时钟复位管理模块、各种外设以及 debug 模块等。MCU 核心常用的有需要授权的 ARM 核、开源的 RISC-V<sup>[8-10]</sup>。系统总线常见的是 ARM 推出的 AMBA 总线中的高速总线(Advanced High Performance Bus, AHB)<sup>[11-13]</sup>。存储单元包括掉电易失随机存储(Random

图 1 MCU 芯片的系统架构组成图

Access Memory, RAM)、掉电不丢失只读存储(Read Only Memory, ROM)。外设主要看 MCU 芯片的应用场景,一般都有低速通信外设,如串行收发器。此外还有 debug 模块,它是 MCU 核心“肚里的蛔虫”,在 MCU 芯片正常工作时没有什么作用,但是当芯片内部有问题时,可以通过 debug 通道获取很多信息。但为了减小 MCU 核心设计复杂度以及设计面积,往往大多数系统中不包含 debug 模块。

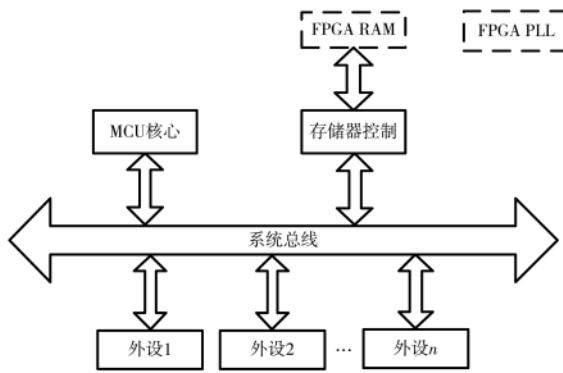

通常进行 FPGA 原型验证,为了尽可能保证与 ASIC 设计一致,FPGA 原型替换只进行独立 IP 的替换<sup>[14-15]</sup>,而其控制部分仍然会保留或做等价的微改动。替换后的架构如图 2 所示。一般 MCU 芯片中时钟分为快时钟和慢时钟,进行 FPGA 原型替换的时候,采用 FPGA 的锁相环(Phase Locked Loop,PLL)资源,将 FPGA 输入的时钟进行分频或者倍频处理后提供给各个功能模块使用。存储器进行 FPGA 原型替换,考虑到 FPGA 的 RAM 资源丰富和使用 FPGA 自带 IP 的性能高,一般不使用直接的逻辑替换,而使用 FPGA 的 RAM IP。

图 2 MCU 芯片 FPGA 原型系统架构组成

## 2 改进的 MCU 芯片的 FPGA 原型验证平台架构

通常 FPGA 原型验证遇到问题时，使用 FPGA 软件带的 debug 软核进行逻辑的内部查错。这个方法有以下几个缺点：(1)需要重新综合，浪费时间；(2)debug 软核占 FPGA 的逻辑资源，FPGA 选型要预留资源，增加成本；

(3)没有重复使用价值，对不同的问题需要重新设置，再综合。

对于 MCU 芯片，核心就是整个芯片运行的大脑，任何动作都由核心控制，而核心运作又是通过程序控制的，这个程序就放在存储单元中。前仿真验证时，为了节约仿真时间，不会按照芯片的实际工作流程去模拟仿真，一般选择通过后台直接把验证程序写入存储单元。由此启发，FPGA 原型验证也可以通过另外一个通道把验证程序写入存储单元。那怎么去实现呢？

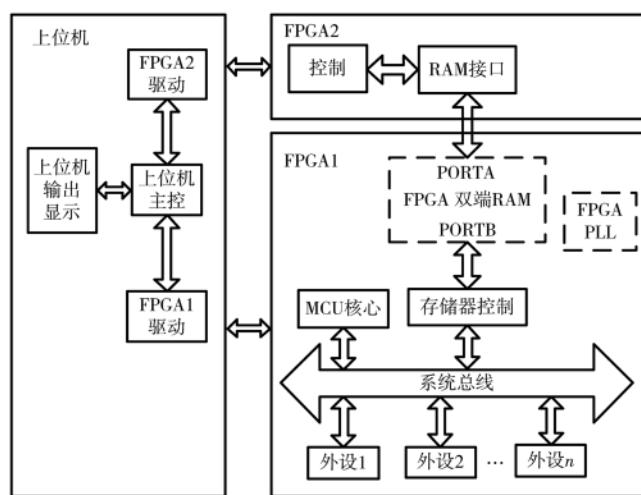

本文提出将传统 FPGA 原型验证过程中使用 FPGA 的 RAM 原型替换程序存储单元, 改为使用 FPGA 双端口 RAM 替换。其中一个端口控制按照传统的接入方法, 另一端口控制信号接到专门的控制逻辑上, 独立控制, 而且不影响原 MCU 芯片功能。首先想到专门的控制逻辑放到另外一块 FPGA2 连接, 由它独立控制。改进的 MCU 芯片的 FPGA 原型验证平台架构组成如图 3 所示。两块 FPGA 连接在到上位机, 上位机软件统一控制。

图 3 改进的 MCU 芯片的 FPGA 原型验证平台架构组成

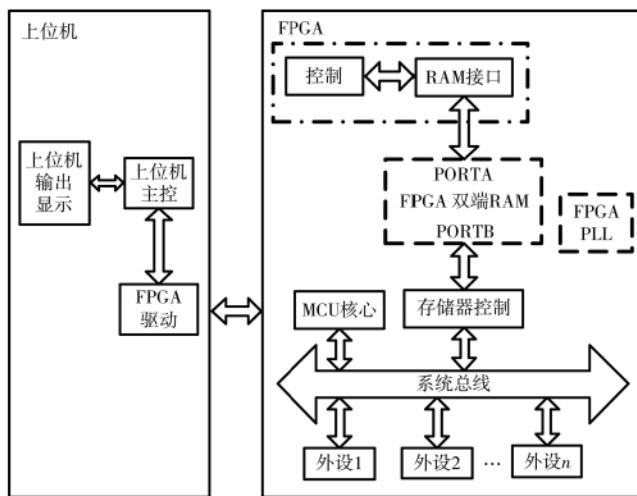

对于上述的改进方案,一个验证平台需要两块FPGA板卡,如果手头正好没有第二块FPGA开发板,那本方案也没有可行性。对此提供另外一种解决方案,即二次改进方案。该方案是在原来设计思想上,把双端RAM连接到FPGA2的逻辑,也放入FPGA1中。这样还有一个优势,使用同一时钟源,减少异步信号带来的同步处理的逻辑量,控制逻辑也相对简单了。二次改进的MCU芯片的FPGA原型验证平台架构组成如图4所示。

完整的验证平台还包括测试向量和测试结果输出。整个验证系统的工作流程可分为两大部分。第一部分是验证 MCU 芯片特殊工作情况下的功能。在验证 MCU 芯片特殊工作情况下的功能，使用 MCU 原有的烧录通道，将运行程序烧录到双端 RAM 口 PORTB，通过设计的通道从双端 RAM 口 PORTB 读出程序进行校验，验证烧录通道是否正常。如果不正常，那问题就定位在烧录通道上。

图 4 二次改进的 MCU 芯片的 FPGA 原型验证平台架构组成

第二部分是验证 MCU 芯片正常工作情况下的各个模块的功能。具体的流程步骤如下:(1)上位机取测试向量编译成可执行程序;(2)上位机将该程序通过双端 RAM 口 PORTA 写入;(3)上位机启动 FPGA 原型系统工作。运行结束后上位机收到测试结果进行保存分析,然后重复(1)~(3)的操作,直至所有测试完成。

### 3 实践与对比分析

使用曼彻斯特编码,单线通信的自定义协议进行逻辑实现;其中“01”代表逻辑 0,“10”代表逻辑 1,连续的

“00”代表传输开始,连续的“11”代表无数据传输;开始传输的是读写类型,紧接着传输的是长度,再是读写的起始地址,最后是读写的数据。

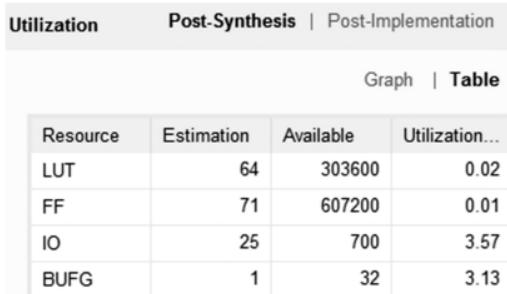

采用 Xilinx 的 v7-485t 芯片进行本设计的综合,使用的逻辑资源如图 5 所示。

图 5 FPGA 综合后逻辑分布图

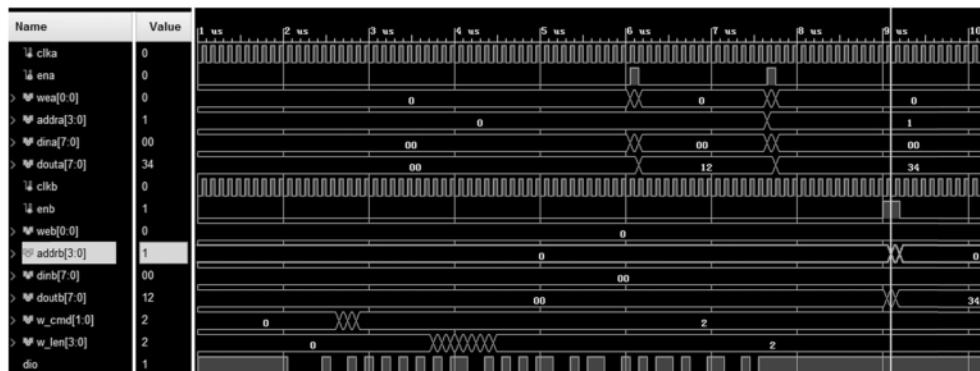

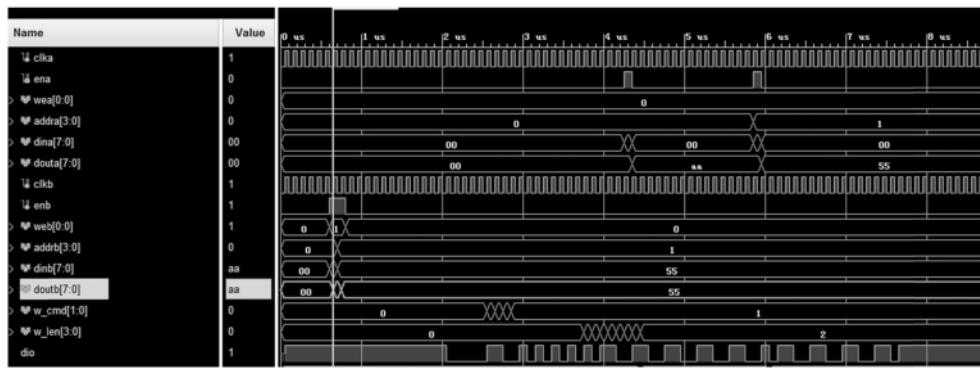

对本设计进行功能仿真,读写时序分别如图 6、图 7 所示。其中 dio 信号为单线通信数据。图 6 通过 dio 从 PORTA 往地址 0 和 1 写入数据 0x12 和 0x34,然后从 PORTB 读出校验正确;图 7 从 PORTB 地址 0 和 1 写入数据 0xAA 和 0x55,再通过 dio 从 PORTA 读出校验正确。

通过实践统计,将所述的三种验证平台设计进行对比分析,如表 1 所示。

经过对比,发现改进一和改进二的设计都能够完成 FPGA 原型验证的目标同时缩短验证周期。两者区别在

图 6 PORTA 写入 PORTB 读出时序图

图 7 PORTB 写入 PORTA 读出时序图

表 1 三种验证平台设计对比

| 对比项           | 传统平台 | 改进平台 | 二次改进平台 |

|---------------|------|------|--------|

| debug 需要再次综合  | 是    | 否    | 否      |

| 使用 FPGA 板卡数量  | 1    | 2    | 1      |

| 对 FPGA 板卡资源要求 | 较大   | 正常   | 微大     |

| 上位机逻辑复杂度      | 正常   | 较难   | 正常     |

| 可复用           | 否    | 是    | 是      |

| 验证周期          | 正常   | 缩短   | 缩短     |

于使用 FPGA 板卡的数量上的差异,当有现成的 FPGA 开发板时,在这里建议当 FPGA 原型的逻辑量已经接近 FPGA 板卡资源的 70%以上时,就选择改进一的方案。如果需要进行 FPGA 选型时,可以根据逻辑量的评估以及价格来综合考虑。选择两块 FPGA 时,对应的 FPGA2 不需要跟 FPGA1 一样,因为增加的那部分逻辑量比较小,可以选择比较便宜小容量的 FPGA,来减小成本。

#### 4 结论

本文提出了一种基于 MCU 芯片 FPGA 原型验证平台设计方法,相比传统的 FPGA 原型验证能够缩短验证周期,从而加快芯片产品的面世。本文中介绍了 MCU 系统的基本架构组成,FPGA 原型验证的基本方法;详细介绍了设计思路,给出了两种实施方案,并进行了实践对比分析,实际应用可以根据需求来选择。此设计方法具有通用性,可移植性,值得推广。

#### 参考文献

- [1] 王欣宇.MCU 技术及市场发展趋势分析[J].电子技术应用,2019,36(10):1-3.

- [2] 虞致国,魏敬和.基于 FPGA 的 ARM SoC 原型验证平台设计[J].电子与封装,2007(5):25-28.

- [3] 刘云晶,刘梦影.一种 32 位 MCU 的 FPGA 验证平台[J].电子与封装,2020,20(1):010205.

- [4] 王红卫,占杨林,梁利平.以覆盖率为导向的自动化验证平台[J].电子测试,2013(5):82-84.

- [5] 张跃玲,张磊,汪健,等.FPGA 的验证平台及有效的 SoC

(上接第 58 页)

- 的应用[J].计算机测量与控制,2007(9):1189-1191.

- [13] SHI Y H, EBERHART R C. Empirical study of particle swarm optimization[C]//Congress on Evolutionary Computation. IEEE, 2002.

- [14] 秦媛.粒子群算法改进及其应用研究[D].南京:南京邮电大学,2018.

- [15] 刘天舒.BP 神经网络的改进研究及应用[D].哈尔滨:东北农业大学,2011.

验证方法[J].单片机与嵌入式系统应用,2016,16(3):8-11.

- [6] 赵新超,陈岚,冯燕,等.基于混合原型平台的 UART IP 核设计与验证[J].电子技术应用,2015,41(10):39-42.

- [7] 梁文远,易晨.FPGA 在电动汽车电机控制器中的应用[J].机电工程技术,2020,49(11):231-232.

- [8] 折如义,李炳辉,姜佩贺.三级流水线 RISC-V 处理器设计与验证[J].电子技术应用,2020,46(5):44-49.

- [9] WATERMAN A, LEE Y, PATTERSON D A, et al. The RISC-V instruction set manual, volume I : user-level ISA [R]. CS Division, EECE Department, University of California, Berkeley, 2014.

- [10] WATERMAN A, LEE Y, PATTERSON D A, et al. The RISC-V instruction set manual, volume I : base user-level ISA [R]. California : University of California .EECS Department, 2011.

- [11] 王一楠,林涛,余宁梅.基于 AMBA 的 AHB 总线矩阵设计[J].微电子学与计算机,2019,36(2):73-77.

- [12] 郝振和,焦继业,李雨倩.基于 AHB 总线的 RISC-V 微处理器设计与实现[J].计算机工程与应用,2020,56(20):52-58.

- [13] 马鹏,刘佩,张伟.基于 UVM 的 AMBA 总线接口通用验证平台[J].计算机系统应用,2021,30(7):57-69.

- [14] 迟海明,周春良,赵东艳,等.宽带电力线载波通信芯片的 FPGA 验证[J].电子设计工程,2021(1):128-131.

- [15] 程翼胜.SoC 芯片 FPGA 原型的软硬件协同验证[J].单片机与嵌入式系统应用,2017(11):7-13.

(收稿日期:2022-02-12)

#### 作者简介:

张文文(1988-),女,硕士,工程师,主要研究方向:数字集成电路设计与验证。

唐映强(1988-),男,学士,助理工程师,主要研究方向:数字集成电路设计与验。

扫码下载电子文档

(收稿日期:2022-01-04)

#### 作者简介:

宋佳骏(1995-),男,硕士,助理工程师,主要研究方向:电力设备状态监测。

刘守豹(1983-),男,博士,高级工程师,主要研究方向:电力系统暂态分析与工程电磁场数值计算。

熊中浩(1994-),男,硕士,专责工程师,主要研究方向:智能算法、优化控制。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所