# 一种改进型高速 1553B 总线发送器斜率控制电路

刘士全, 唐海洋, 顾林

(中科芯集成电路有限公司, 江苏 无锡 214072)

**摘要:** 传统的 1553B 总线通信速率为 1 Mb/s, 难以满足目前电子设备对通信总线高速率的要求。设计了一种新型的发送器斜率控制电路, 并应用于高速 1553B 总线发送器芯片, 提升了发送器的速率, 改善了总线波形质量。测试表明, 采用本文设计的改进型 1553B 总线发送器, 通信速率最高可达 4 Mb/s, 达到现有标准速率的 4 倍, 性能提升效果显著。

**关键词:** 1553B 总线; 收发器; 芯片设计; 斜率控制

中图分类号: TN92

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.212385

中文引用格式: 刘士全, 唐海洋, 顾林. 一种改进型高速 1553B 总线发送器斜率控制电路[J]. 电子技术应用, 2022, 48(9): 63–66.

英文引用格式: Liu Shiquan, Tang Haiyang, Gu Lin. Design and performance test of high speed 1553B bus transceiver chip[J]. Application of Electronic Technique, 2022, 48(9): 63–66.

## Design and performance test of high speed 1553B bus transceiver chip

Liu Shiquan, Tang Haiyang, Gu Lin

(China Key System & Integrated Circuit Co., Ltd., Wuxi 214072, China)

**Abstract:** The traditional 1553B bus communication rate is 1 Mb/s, which is difficult to meet the requirements of military electronic equipment for high-speed communication bus. In this paper, a new transmitter slope control circuit is designed and applied to the high-speed 1553B bus transmitter chip, which improves the speed of the transmitter and the quality of bus waveform. The test shows that using the improved 1553B bus transmitter designed in this paper, the communication rate can reach 4 Mb/s, which is 4 times higher than the existing standard rate, and the performance improvement effect is remarkable.

**Key words:** 1553B; transceiver; chip design; slope control

## 0 引言

MIL-STD-1553 数据总线因其高可靠性等诸多优点被广泛应用于武器装备, 实现传感器、各个分系统的信息共享与传输<sup>[1-2]</sup>。但随着软件技术的革新和更快处理器的诞生, 传统 1553B 仅仅 1 Mb/s 的数据传输速度已无法满足现代武器装备研发的需求<sup>[3]</sup>, 这也就催生了很多更高更快的通信方式, 如时间触发网络(TTE)和 FC-AE-1553。

近年来, 时间触发网络的提出, 在传统以太网的基础上增加了时间同步机制和流量调度算法, 具有低误码率、低延时、高带宽、高速率等优势, 能够适用于未来航天技术的需求<sup>[4-5]</sup>, 但时间触发网络还处在协议完善阶段, 离投入实际应用还需要时间; FC-AE-1553 在光纤传输的基础上定义了对 MIL-STD-1553 的上层协议映射, 使其达到高速率的同时兼顾稳定性<sup>[6]</sup>, 但 FC-AE-1553 需要改变其物理层, 不同形式的信道, 其组网方式和连接介质均需重新选择和改变, 这也就导致了研发成本的上升<sup>[7]</sup>。

因此, 高速 1553B 通信的设计是一个行之有效的方式, 在提升通信速率的同时, 保留了组网方式、连接介质的一致性, 降低了武器装备研发的成本<sup>[8]</sup>。业内对高速 1553B 总线的研究也日趋增多, 文献[9]介绍了 2 Mb/s 速率 1553B 总线仿真卡的软硬件设计与实现; 文献[10]提供了一种 4 Mb/s 速率 1553B 总线测试平台的实现方法, 该测试平台能够支持 4 Mb/s 速率 1553B 的电气特性参数和总线协议功能测试。

本文设计了一种新型的收发器斜率控制电路, 并应用于高速 1553B 总线发送器芯片, 提升了发送器的速率, 改善了总线波形质量, 并与 1 Mb/s 收发器完全兼容, 其通信介质、变压器、耦合器等组网设备完全保持一致, 极大程度降低了装备升级的成本。测试表明, 设计的总线收发器通信速率满足 4 Mb/s 的性能要求, 斜率控制电路有效保证了发送器性能。

## 1 发送器功能与架构

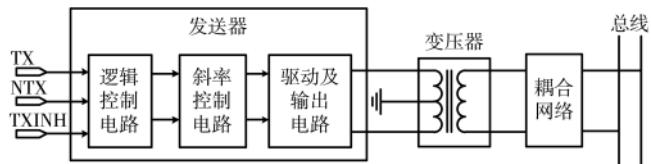

如图 1 所示, 电压型 1553B 发送器主要由逻辑控制

图 1 发送器电路原理图

电路、斜率控制电路、驱动及输出电路组成<sup>[11]</sup>。逻辑控制电路的作用是识别使能信号,当 TXINH 使能信号为低时,发送器使能有效;TXINH 为高时,发送器处于关闭状态;保证输入信号 TX、NTX 为一对曼彻斯特Ⅱ编码互补信号,如出现同时为高电平或低电平时,关断电路。输出及驱动电路将曼彻斯特Ⅱ编码信号转化为 BUS 端总线符合 1553B 信号特征的信号输出,驱动变压器,增强带载能力。斜率控制电路的作用是调节输出信号的上升时间、下降时间、总线幅值参数。

分析发送器的电路组成可知,发送器的逻辑控制电路由于都是由数字电路组成,不存在速率限制的瓶颈,其斜率控制电路因其负责总线信号关键参数的调节,在实现 1553B 发送速度提升中起到关键的作用。

## 2 斜率控制电路

### 2.1 一种典型的斜率控制电路

上升时间、下降时间、总线幅值是 1553B 通信规范的重要参数<sup>[12]</sup>。斜率控制电路通过调节主回路 PMOS 管驱动信号的上升时间和下降时间,并提供对主回路 PMOS 管的驱动能力,从而调节发送器总线输出信号的上升时间和下降时间,驱动能力越强,总线输出幅值越高。

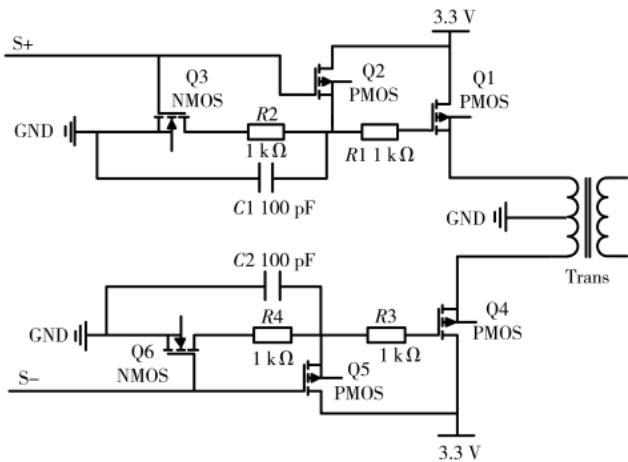

图 2 所示为某型号的 1553B 发送器的斜率控制电路,其工作原理是,输入控制信号 S+、S- 为曼切斯特Ⅱ编码互补信号,当输入控制信号 S+ 为高电平时,下级 NMOS 管 Q3 导通,上级 PMOS 管 Q2 截止,此时主回路 PMOS 管 Q1 导通,电流为后级的变压器充电,从而在 1553B 总线上输出信号;当输入控制信号 S+ 为低电平时,下级 NMOS 管 Q3 截止,上级 PMOS 管 Q2 导通,此时主回路 PMOS 管

图 2 典型的斜率控制电路原理图

Q1 截止,关断输出。驱动信号的上升下降时间由两部分电路调节,分别是电阻 R1、R2 的值和电容 C1, 电阻 R1、R2 电阻值调节驱动电路的电流,决定主回路 PMOS 管 Q1 的开启关闭速度,电容 C1 调节驱动信号的上升下降时间。同理,S- 的作用机理与 S+一致。

该型斜率控制电路应用在 1 Mb/s 标准速率下,能取得比较好的效果。但将其速度提高到 4 Mb/s 及以上速度时,就会出现如下问题,如图 3 所示。

(1) 驱动信号:低电平不到 0 V,且具有很大的杂波,导致驱动能力不足;

(2) 总线上波形幅值偏低,幅值为 2 V,离 1553B 规范要求 6 V~9 V 有较大差距,且具有很大的杂波。

图 3 典型斜率控制电路仿真波形图

分析原因如下,驱动信号驱动能力不足主要原因是电阻 R1、R2(也包括电阻 R3、R4)的阻值过大。考虑到后端连接的是变压器负载,工作在高频高速率的工况下,变压器的电感储存能量,在主回路的 PMOS 管 Q1(也包括 Q4,下文表述 Q1、Q4 的原理一致)开启关断时刻得不到有效释放,引起变压器次级线圈输出信号形成振荡,所以体现为杂波,振动消耗了能量,体现为总线上幅值偏低,并引起上升时间和下降时间偏慢。

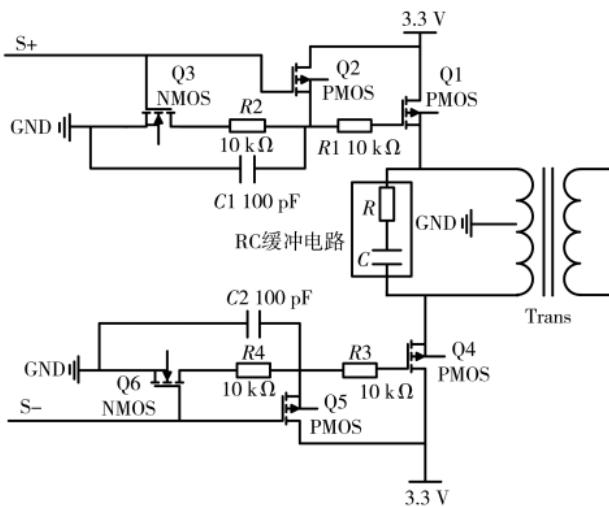

### 2.2 改进型斜率控制电路

本文提出一种改进型斜率控制电路,如图 4 所示。在图 2 的基础上,减少了主回路 PMOS 管 Q1 棚极驱动回路 R1、R2 电阻值,增强其驱动能力,有利于提升上升时间和下降时间,更适应高频高速率的工作场景。同时,在变压器的初级并联了 RC 缓冲电路,在主回路 PMOS 管导通与关断的瞬间,及时地将电感线圈中的储存电能释放掉。采用本文设计的斜率控制电路构建发送器,可沿用 1 Mb/s 接收器,其通信介质、耦合器均无需改变,保持与 1 Mb/s 1553B 的兼容性。

图 4 改进型斜率控制电路原理图

RC 缓冲电路的工作原理如下：在主回路 PMOS 管 Q1 关断的瞬间，变压器绕组等效成一个电感，电感阻止电流发生突变，并产生感应电压，与直流电源电压  $U_c$  串联一起加在 PMOS 管 Q1 两端，此时，Q1 两端的尖峰电压  $U_s$  为：

$$U_s = U_c + \frac{(L_c + L_s)di}{dt} \quad (1)$$

式中： $U_s$  为 PMOS 管 Q1 两端的尖峰电压； $U_c$  为直流电源电压； $L_c$  为变压器等效电感， $L_s$  为电路杂散电感， $di/dt$  为 Q1 管源极和漏极电流变化速率。

RC 缓冲电路的作用是吸收 Q1 管关断时产生的过电压，其本质是靠吸收电容  $C$  来吸收掉变压器等效电感和杂散电感产生的能量，即能量的转移，因此确定吸收电容  $C$  的容值大小<sup>[13]</sup>。电路中存储在总电感中的能量为：

$$E_1 = \frac{1}{2}(L_c + L_s)I^2 \quad (2)$$

吸收电容上需要吸收的能量为：

$$E_2 = \frac{1}{2}C\Delta U^2 \quad (3)$$

$\Delta U$  为总电感产生的过电压，即  $\Delta U = U_m - U_c$ ，其中， $U_m$  可通过示波器测试电感得到， $U_c$  为直流电压。

假设关断前存储电感中的磁能在 Q1 关断时完全转化为  $C$  中电能。因此就有：

$$\frac{1}{2}(L_c + L_s)I^2 = \frac{1}{2}C\Delta U^2 \quad (4)$$

从而求得吸收电容的容值为：

$$C = \frac{(L_c + L_s)I^2}{\Delta U^2} \quad (5)$$

因为吸收电容  $C$  在 Q1 管导通时存储的能量为：

$$E_0 = \frac{1}{2}CU_c^2f \quad (6)$$

其中  $f$  为电路的开关频率。

存储在总电感上的能量为：

$$E_0' = \frac{1}{2}(L_c + L_s)I_0^2f \quad (7)$$

式中， $I_0$  为 Q1 管的关断电流。

因此，消耗在吸收电阻  $R$  上的功率  $P$  为：

$$P = \frac{1}{2}CU_c^2f + \frac{1}{2}(L_c + L_s)I_0^2f \quad (8)$$

因为 RC 缓冲电路是随着 Q1 管的开关而循环工作的，因此在 Q1 管导通期间，存储在吸收电容  $C$  中的能量必须通过电阻  $R$  消耗掉，只要满足  $\tau = RC$  小于 1/4 的 Q1 管导通时间，就可以保证电容  $C$  中绝大部分能量的释放，不会影响下一次吸收<sup>[14]</sup>，因此吸收电阻可以通过下式来确定：

$$R \leq \frac{\tau_0}{4C} \quad (9)$$

式中， $\tau_0$  为 Q1 管的导通时间。

但是  $R$  也不是越低越好的，因为吸收电路中存大电流振荡，Q1 管导通时的电流峰值也会相应增加<sup>[15]</sup>，因此在满足上式的情况下尽量使  $R$  设得高一点，具体可参考式(10)：

$$R \geq 2\sqrt{(L_c + L_s)/C} \quad (10)$$

综上所述吸收电阻  $R$  为：

$$2\sqrt{(L_c + L_s)/C} \leq R \leq \frac{\tau_0}{4C} \quad (11)$$

根据图中器件所给出的参数按照式(5)和式(11)可得出吸出电阻大约为  $20 \Omega$ ，吸收电容大约为  $12 \text{ nF}$ 。

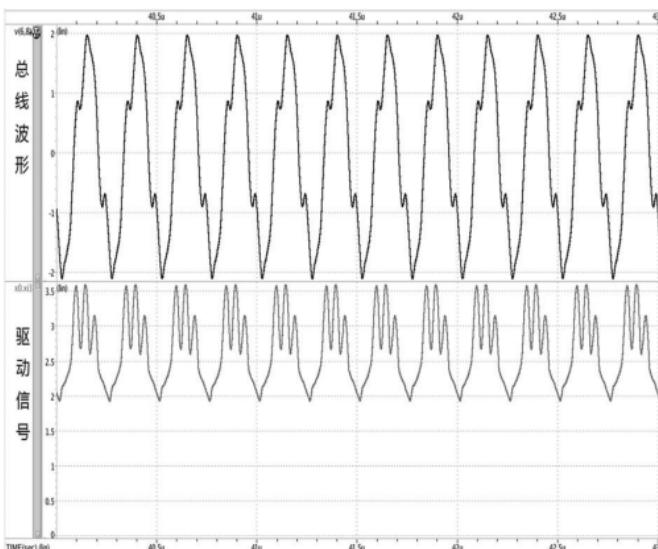

### 2.3 电路仿真与分析

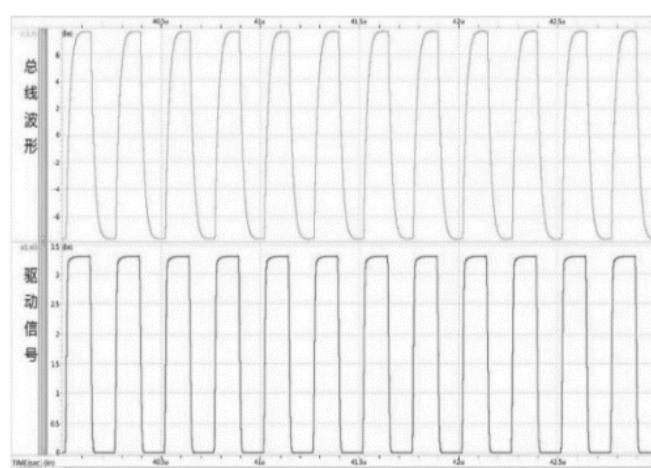

使用电路仿真工具，对改进型斜率控制电路进行仿真，得到总线波形和 PMOS 管 Q1 栅极驱动信号的仿真波形如图 5 所示。

图 5 改进型斜率控制电路仿真波形图

对比图 3 和图 5 可以看出：

(1) 驱动信号：典型斜率控制电路在 4 Mb/s 速率下，驱动信号低电平为 2 V，体现对主回路 PMOS 管的驱动能

力不足,导致总线波形幅值不够,因为驱动信号具有很大的杂波,导致总线信号毛刺太大。图5显示驱动信号波形平滑且低电平可以达到0 V,对于主回路的PMOS管驱动能力有了较大提高。

(2)总线波形:典型斜率控制电路总线输出幅值为2 V,改进型斜率控制电路输出波形幅值为7 V,且波形平滑无毛刺,说明RC缓冲电路的引入,对总线波形的改善效果明显。

### 3 收发器性能测试

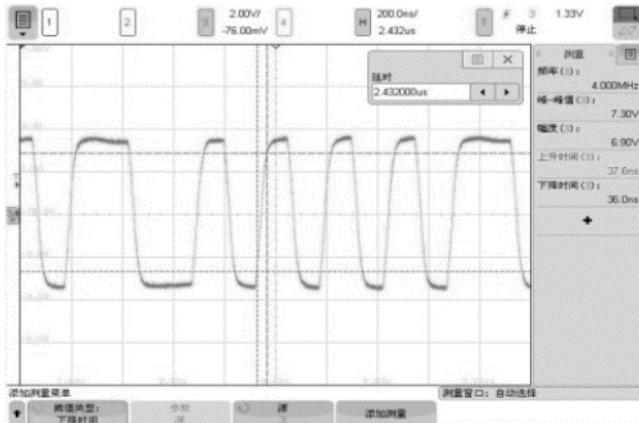

使用0.5 μm COMS工艺流片,封装后按照1553B规范对其进行测试。4 Mb/s速率下总线波形如图6所示。从图6可以看出,在4 Mb/s速率下,总线波形平滑无毛刺,跟仿真结果一致,说明改进型斜率控制电路,特别是RC缓冲电路取得了较好效果。表1列举了该发送器在4 Mb/s速率下其主要电参数的值,各项指标符合规范要求。

图6 总线波形图

表1 发送器主要电参数表

| 测试参数            | 合格判据  | 测试值  | 结论 |

|-----------------|-------|------|----|

| $t_r$ (上升时间)/ns | 30~60 | 37.6 | 合格 |

| $t_f$ (下降时间)/ns | 30~60 | 36   | 合格 |

| $V_o$ (输出电压)/V  | 6~9   | 6.9  | 合格 |

### 4 结论

本文设计了一种新型的收发器斜率控制电路,并应用于高速1553B总线发送器芯片,提升了发送器的速率,改善了总线波形质量,并与1 Mb/s收发器完全兼容,其通信介质、变压器、耦合器等组网设备完全保持一致,极大程度降低了装备升级的成本。测试表明,设计的总线收发器通信速率满足4 Mb/s的性能要求,斜率控制电路有效保证了收发器性能。

### 参考文献

- [1] 刘士全,隽扬,蔡洁明,等.1553B总线应用发展研究[J].电子与封装,2013(12):12~15.

- [2] 王新亮,陈凯,薛琪琪,等.基于1553B总线的飞控软件测试仿真平台设计[J].计算机测量与控制,2020,28(11):12~14.

- [3] 蔡洁明,魏敬和.高速1553总线分立器件收发器设计[J].微型机与应用,2016,35(20):34~36.

- [4] 马跃,朱纪洪,杨佳利,等.基于时间触发通信的机载网络可靠性[J].计算机工程与设计,2020,41(5):1201~1206.

- [5] 赵漫菲,姚蕊,王浩枫,等.TTE时间触发以太网技术在国产化平台中的应用[J].计算机工程与设计,2021,42(11):3018~3025.

- [6] 凤雷,冯牧,乔家庆,等.FC-AE-1553设备光纤接口电路的设计与实现[J].电子测量技术,2012(7):62~65.

- [7] 闫华,杨煜.应用于10 Gbit/s光通信及背板传输的自适应均衡器设计[J].电子与封装,2020,20(5):050301~050307.

- [8] 樊彬,唐艺菁,王剑峰,等.一种新型高速1553B总线控制器的应用验证[J].微电子学与计算机,2014(5):87~89,93.

- [9] 淮治华,田泽,杨峰,等.2M1553B总线仿真卡的设计与实现[J].计算机技术与发展,2015,25(4):229~232.

- [10] 牛文娟,张方,饶张飞.一种高速1553B总线控制器自动测试平台的开发[J].计算机测量与控制,2020,28(10):7~10.

- [11] 王晋,田泽,张文博,等.一种COMS 1/2Mbps 3.3V1553B收发器[J].计算机技术与发展,2014,24(11):250~253.

- [12] 印琴,于宗光,魏敬和,等.一种3.3V低电源电压的1553B总线收发器设计[J].电子器件,2015,38(3):646~649.

- [13] 姜栋栋,王烨,卢峰,等.IGBT过电压产生机理分析及RC缓冲电路的设计[J].电力科学与工程,2011,27(4):23~29.

- [14] 易灵芝,朱和潇,龙谷宗,等.基于耦合电感式缓冲电路全软开关DC/DC变换器[J].电力系统及其自动化,2020,32(10):83~89.

- [15] 荆明亮,贺智昌.RC缓冲电路的优化设计[J].中文科技期刊数据库工程技术,2016(8):157.

(收稿日期:2021-11-28)

### 作者简介:

刘士全(1982-),男,高级工程师,主要研究方向:1553总线技术、TTE网络通信技术。

唐海洋(1986-),男,工程师,主要研究方向:1553总线技术、自动化检测技术。

顾林(1986-),男,高级工程师,主要研究方向:多芯片集成技术。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所