# 一种片上嵌入式 Flash 测试接口的设计

钱劲宇, 强小燕, 屈凌翔

(中国电子科技集团公司第五十八研究所, 江苏 无锡 214072)

**摘要:** Flash 存储器具有功耗低、存储容量大、体积小等特点, 被广泛应用于嵌入式系统。目前 Flash 存储器多数使用串行接口进行擦写测试, 存在着测试效率低、测试成本高等问题。针对以上问题, 设计并实现了一种片上嵌入式 Flash 的测试接口。结合片上嵌入式 Flash 的接口特点和时序要求, 设计了基于多线 SPI 的测试接口, 并在确保稳定性的情况下实现了对多块 Flash 存储器并行测试的设计, 提高了测试速度。通过 NCVerilog 仿真结果表明, 该设计有效缩短了测试时间, 达到了测试要求, 并成功应用于一款 32 位浮点微处理器中。

**关键词:** Flash; 测试接口; 测试速度; 微处理器

中图分类号: TN402

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.222693

中文引用格式: 钱劲宇, 强小燕, 屈凌翔. 一种片上嵌入式 Flash 测试接口的设计[J]. 电子技术应用, 2022, 48(10): 31-35.

英文引用格式: Qian Jinyu, Qiang Xiaoyan, Qu Linxiang. Design of an on-chip Flash memory test interface[J]. Application of Electronic Technique, 2022, 48(10): 31-35.

## Design of an on-chip Flash memory test interface

Qian Jinyu, Qiang Xiaoyan, Qu Linxiang

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** Flash has the characteristics of low power consumption, large storage capacity and small volume, is widely used in embedded systems. Flash usually uses serial interface for erasing and programming test, which has the problems of low test efficiency and high test cost. The design and implementation of a test for Flash on chip is presented in this paper. By analyzing the interface and timing requirements of Flash on chip, a test interface based on multi-line SPI is designed, and the parallel test design of Flash memories is realized under the condition of ensuring stability, which improves the test speed. The NCVerilog simulation results show that the design effectively shortens the test time, meets the test requirements, and is successfully applied to a 32-bit floating-point microprocessor.

**Key words:** Flash; test interface; test speed; microprocessor

## 0 引言

随着信息技术的飞速发展, 用户对数据存储系统的容量、功耗、速度等要求也越来越严格<sup>[1-2]</sup>。Flash 存储器相对传统的存储器件 RAM 而言, 具有集成度高、体积小、成本低等优点<sup>[3-4]</sup>, 因而随着集成电路的规模越来越大, Flash 存储器飞速发展, 逐渐成为系统芯片主流的容量存储媒体<sup>[5]</sup>。

目前 Flash 存储器在完成设计后, 通常将串行标准接口作为测试接口进行擦写测试, 而串行时钟频率比较低, 传输数据慢, 测试效率低。另一方面, Flash 存储器的测试往往存在着擦除、编程数据比较慢的问题, 这对存在多块 Flash 的芯片产生了巨大的测试量, 需要进行大量重复的测试, 导致需要的测试时间较长<sup>[6-7]</sup>, 因此, 如何提高测试效率, 简化测试流程, 在 Flash 测试中显得尤为重要。

本文对片上 Flash 存储器增加了测试接口, 设计了

片外测试通道, 实现了片上嵌入式 Flash 的可测试性。为了提高测试速度, 降低测试成本, 一方面, 设计了基于 1/2/4/8 线多线传输的 SPI 测试接口, 在兼容串行传输数据的同时支持并行传输数据, 另一方面, 在确保稳定性的情况下, 实现了灵活选定 1/2/3 块 Flash 存储器并行擦写测试的设计。

## 1 总体设计

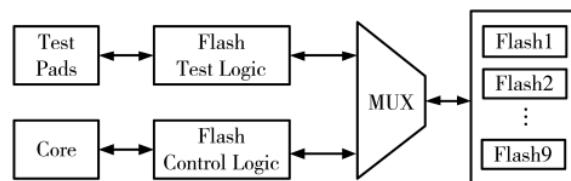

Flash 存储器的总体设计主要由 Flash 控制器模块和 Flash 测试器模块两部分组成, 如图 1 所示, 正常工作模

图 1 Flash 总体设计

式时由 Flash 控制器模块控制, 实现 Flash 与内核之间的交互, 测试模式时由 Flash 测试器模块控制, 通过外部测试引脚来实现对 Flash 的编程、读取和擦除操作。Flash 控制器模块和 Flash 测试器模块通过选通模块来实现对 9 块 Flash 的控制, 选通信号可以通过内部寄存器配置来进行模式切换。

本文选用的 Flash 是一款 CMOS 页擦除、附带 ECC 校验的字编程嵌入式存储器, 数据输入总线位宽为 36 bit, 数据输出总线位宽为 144 bit, 地址总线位宽为 15 bit。内部存储空间可以分为存储块和信息块两部分, 其中存储块的空间为  $32 \text{ K} \times 144 \text{ bit}$ , 512 页, 每页容量为 1 KB, 信息块的空间为  $64 \times 144 \text{ bit}$ , 8 页, 每页容量为 1 KB。Flash IP 的接口信号如表 1 所示。

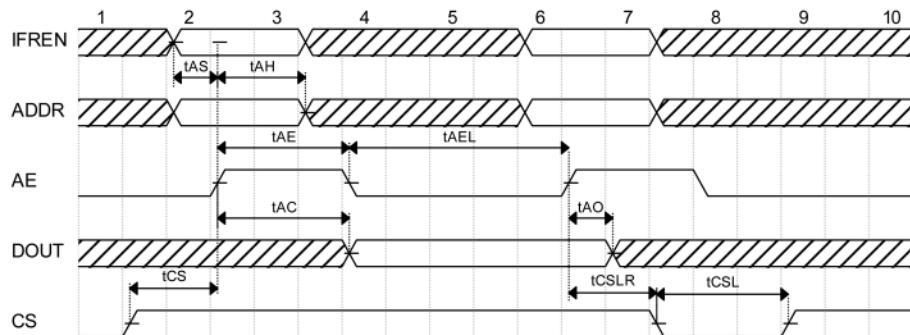

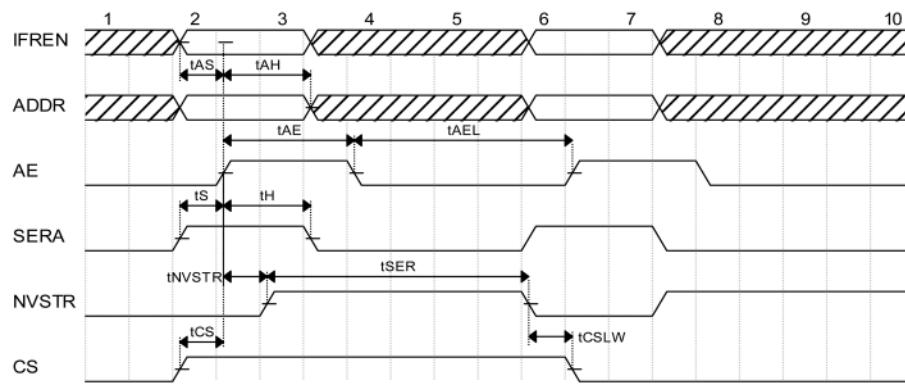

在进行编程、读取和擦除操作期间, CS 都必须保持为 1, 若 CS 变为 0, 则忽略其余所有控制信号和地址信号。Flash IP 在进行读取、编程以及擦除时接口信号都必须满足相应的时序要求, 测试 Flash IP 的读取操作的时序图如图 2 所示, 其中 IFREN 为 1 时选定信息块, 为 0 时选定存储块。首先将 CS 置为 1, ADDR 和 IFREN 在 AE 上升沿到来前后都需要保持相应的建立时间 tAS 和保持时间 tAH, 在 AE 置为 1 后, 等待 tAC 后, 数据输出总线 DOUT 将相应地址的数据输出。在读操作期间时,

表 1 Flash 接口信号

| 管脚名称        | 方向 | 描述       |

|-------------|----|----------|

| ADDR[14:0]  | 输入 | 地址总线     |

| DIN[35:0]   | 输入 | 数据输入总线   |

| DOUT[143:0] | 输出 | 数据输出总线   |

| AP[1:0]     | 输入 | 地址映射使能   |

| CS          | 输入 | 片选控制     |

| AE          | 输入 | 地址使能     |

| IFREN       | 输入 | 信息块使能    |

| NVSTR       | 输入 | 非易失存储使能  |

| PROG        | 输入 | 编程使能     |

| SERA        | 输入 | 页擦除使能    |

| MASE        | 输入 | 全擦除使能    |

| TBIT        | 输出 | Flash 可用 |

PROG、SERA、MASE、NVSTR 将保持为 0 直到操作完成。

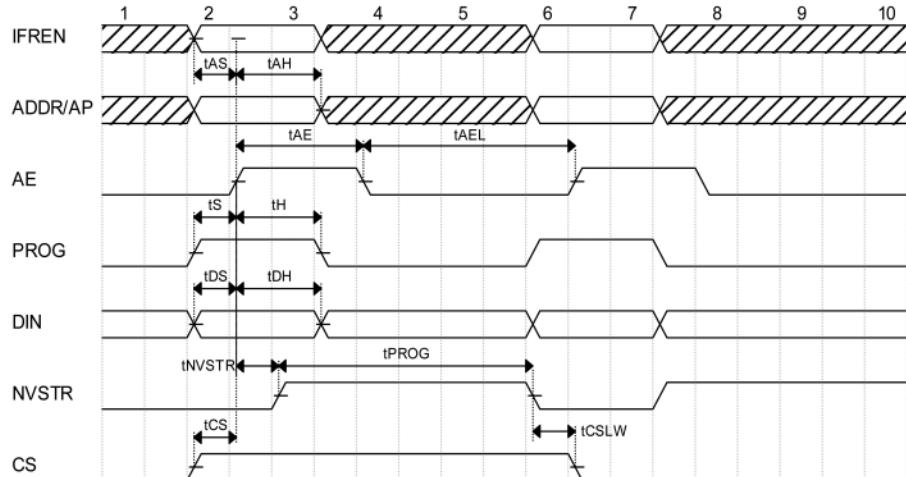

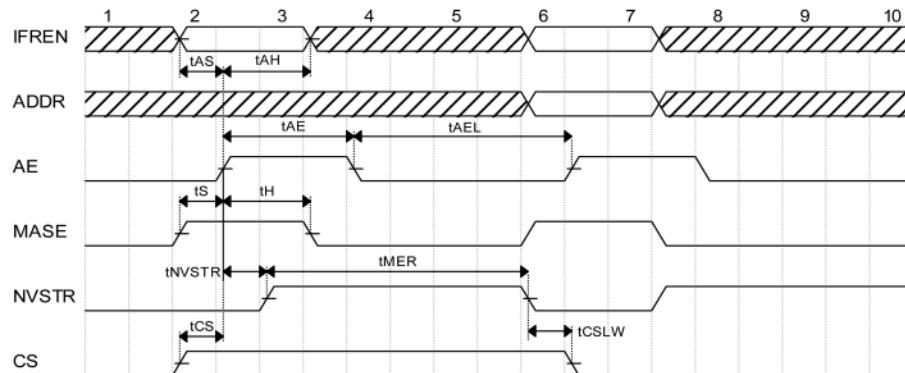

测试 Flash IP 的编程操作的时序图如图 3 所示, 其中 AP 为 2'b11 时 DIN[35:0] 对应于编程位[143:108], AP 为 2'b10 时 DIN[35:0] 对应于编程位[107:72], AP 为 2'b01 时 DIN[35:0] 对应于编程位[71:36], AP 为 2'b00 时 DIN[35:0] 对应于编程位[35:0]。进行编程操作时, AE 类似于时钟信号, IFREN、ADDR、AP、PROG、DIN、CS 在 AE 的上升沿到来前后都需要保持相应的建立时间和保持

图 2 Flash 读取时序

图 3 Flash 编程时序

时间。在 AE 置为 1 后, 等待 tNVSTR 后, NVSTR 置为 1, tPROG 为编程时间, 编程结束后, NVSTR 置 0, 等待 tCSLW 后, CS 置 0。在编程操作期间, SERA、MASE 将保持为 0 直到编程操作结束。

测试 Flash IP 的擦除操作的时序图如图 4 和图 5 所示, Flash IP 被分成 512 页的相同的 1 KB 空间, 擦除方式有页擦除和全擦除 2 种方式, 页擦除可以对任何单独一页进行擦除, 全擦除直接对整块 Flash 进行擦除, 其中 SERA 为页擦除使能信号, MASE 为全擦除使能信号, 两种擦除方式不能同时触发, 同一时间仅一种擦除使能信号置位, NVSTR 根据擦除方式保持相应的擦除时间。

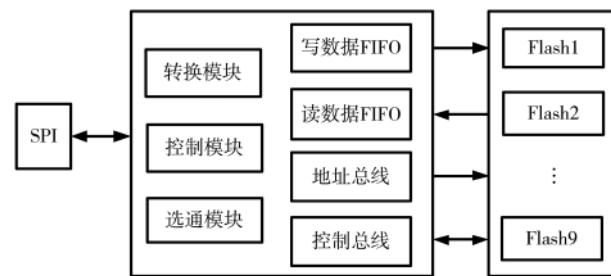

## 2 测试逻辑设计

Flash 测试器的结构如图 6 所示, 可以将其分为 3 个模块: 转换模块、控制模块和选通模块。转换模块连接外部 SPI 接口选择 1/2/4/8 线进行传输, 提取出指令、数据和地址, 进行相应的转换, 控制模块根据测试指令, 输入满足 Flash IP 操作时序的控制信号, 选通模块根据片选指令, 来选择 1/2/3 块 Flash 进行测试。在编程指令时, 由于 Flash IP 的数据输入总线位宽为 36 bit, 因此先要将 SPI 传输的数据转换为 36 bit 数据暂存在写数据 FIFO 中, 再依次等待控制模块输入对应的编程操作的控制信号时, 传入对应的 Flash IP 数据输入总线 DIN 中。读取指令时, 控制模块先执行读取操作将数据输出总线 DOUT 中, 数据读出, 暂存在位宽为 144 bit 的读数据 FIFO 中,

图 6 Flash 测试结构图

通过转换模块将 144 bit 数据转换为 1/2/4/8 bit 数据, 等待 SPI 工作时传输到片外比较器中。

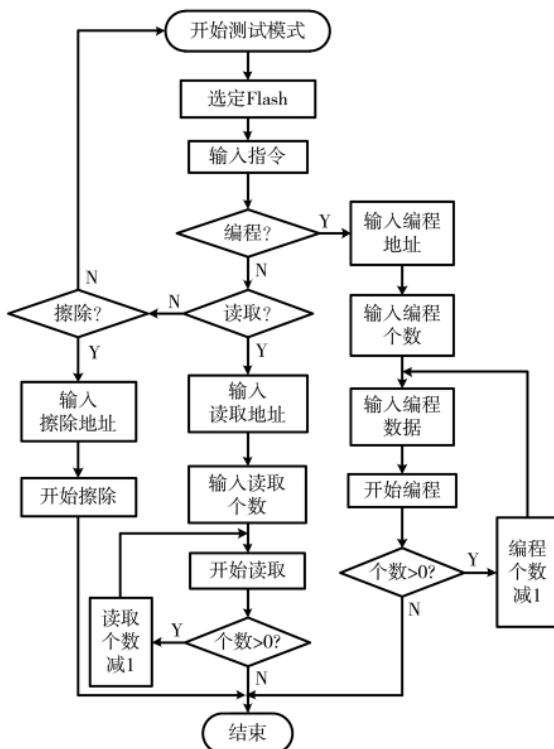

Flash 测试器模块的具体操作流程如图 7 所示。首先通过内部控制信号进入测试模式, 在进入测试模式后, 通过配置 SPI 可以实现 1/2/4/8 线数据传输, SPI 接口持续输入测试序列, 来确定对 Flash 测试器的操作。其次经 SPI 接口输入片选指令, 来选定需要进行操作的 Flash IP, 可以灵活选定 1/2/3 块 Flash。选定 Flash 后, 再输入操作指令, 来控制对 Flash 进行编程操作、读取操作或者擦除操作。如果是编程操作, 会继续等待 SPI 接口输入编程地址以及操作编程个数, 连续输入编程数据至对应的 Flash IP, 直到编程个数为 0 后, 此次编程测试结束。如果是读取操作, 则继续等待输入读取地址以及操作读取个数, 随后读取对应地址的数据至片外比较器进行校验, 读取个数为 0 后, 此次读取测试结束。如果是擦除操

图 4 Flash 页擦除时序

图 5 Flash 全擦除时序

图 7 Flash 测试流程图

作,则输入擦除地址后直接进行擦除操作。待操作结束

后,则可以输入下一次测试指令继续进行测试。

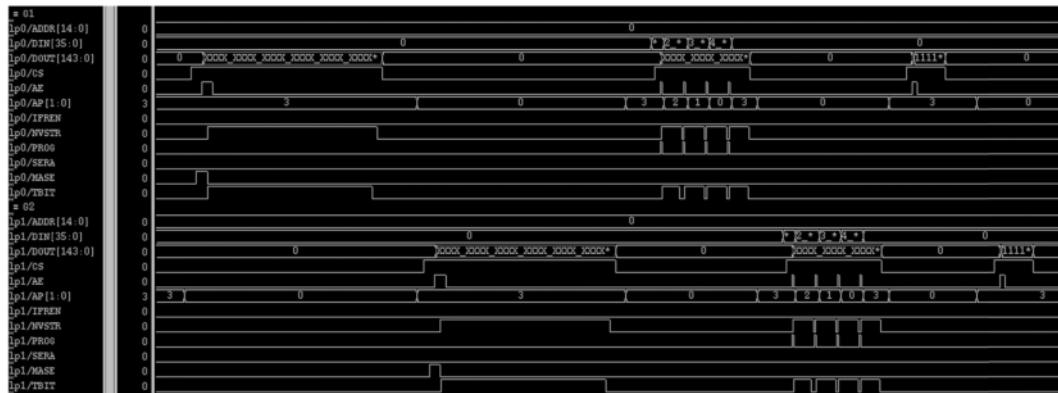

### 3 仿真验证

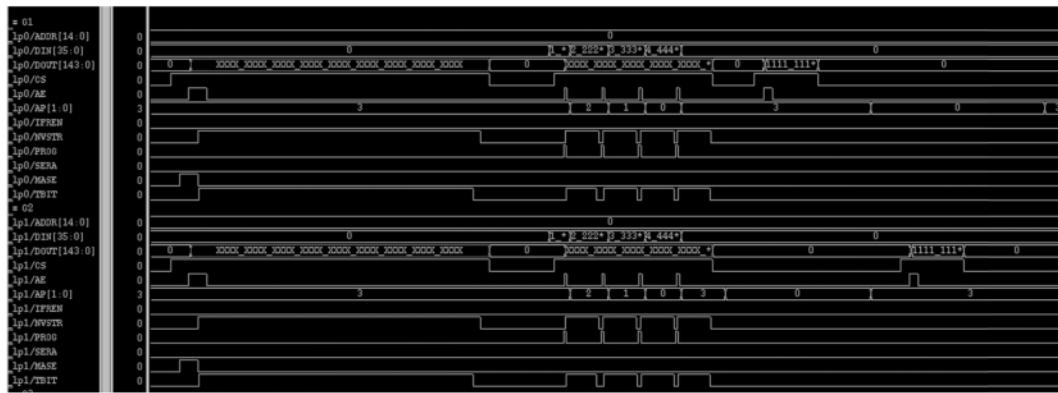

在 Linux 平台上利用 NCVerilog 对 Flash 存储器测试接口设计进行仿真。Flash 存储器的编程操作只能把数据位从 1 变 0,而不能将数据位从 0 转换为 1,只有擦除操作可以实现数据位从 0 到 1 的转换<sup>[8]</sup>,因此为了仿真测试的正确性,在编程和读取操作前,首先应该对 Flash 进行一次全擦除操作。图 8 所示是对 Flash1、Flash2 进行的串行仿真测试,首先依次对 Flash1、Flash2 进行一次全擦除操作,然后再通过 SPI 分别向 Flash1、Flash2 输入一个 144 bit 数据,由于数据输入总线 DIN 位宽为 36 bit,因此需要 4 次编程操作,通过地址映射控制信号 AP 来写入 0 地址的 144 bit 中,随后再读取 0 地址的数据,读出的数据与写入的数据相符。

为了加快测试速度,可以将上述串行测试转换为并行测试,如图 9 所示,对 Flash1、Flash2 同时进行擦除操作和编程操作,然后依次读取对应地址的数据,可以发现,与单独操作 Flash 相比,简化了整体操作流程。由仿真测出,进入测试模式后编程一片 Flash 全空间的时间在 3.2 s 左右,则串行编程 9 片 Flash 的时间大概在 28.8 s,若每次并行测试 3 片 Flash,则只需要 9.6 s 左右即可完成,由此可见,并行测试大大降低了测试成本,提高了测试效率。

图 8 Flash 串行测试

图 9 Flash 并行测试

## 4 结论

本文设计并实现了一种片上嵌入式 Flash 存储器的测试接口,测试接口能够在外部操作指令的控制下实现对 Flash 存储器的编程、读取和擦除操作,实现了 Flash 存储器的可测试性,并进一步实现了基于多线 SPI 的测试接口以及 Flash 存储器并行测试的设计,有效提高了 Flash 存储器的测试速度,降低了测试成本。通过仿真验证,实现了测试功能的要求,并成功应用于一款 32 位浮点微处理器中。

## 参考文献

- [1] COUGHLIN T A timeline for flash memory history[J]. IEEE Consumer Electronics Magazine, 2017, 6: 126–133.

- [2] 王江涛, 赖文豫, 孟小峰. 闪存数据库: 现状、技术与展望[J]. 计算机学报, 2013, 36(8): 1549–1567.

- [3] 赵倩, 唐磊. 一种基于 NAND Flash 的多通道存储系统编址方式研究与实现[J]. 微电子学与计算机, 2018, 35(9): 32–36.

(上接第 30 页)

- accuracy of EEG emotion recognition by combining valence lateralization and ensemble learning with tuning parameters[J]. Cognitive Processing, 2019, 20: 405–417.

- [4] VERMA G K, TIWARY U S. Multimodal fusion framework: a multiresolution approach for emotion classification and recognition from physiological signals[J]. Neuroimage, 2018, 20(1): 162–172.

- [5] KOLODYAZHNIY V, KREIBIG S D, GROSS J J. An affective computing approach to physiological emotion specificity: toward subject-independent, stimulus-independent classification of film-induced emotions[J]. Psychophysiology, 2011, 48(7): 908–922.

- [6] KOELSTRA S, MUHL C, SOLEYMANI M, et al. DEAP: a database for emotion analysis; using physiological signals[J]. IEEE Transactions on Affective Computing, 2012, 3(1): 18–31.

- [7] Zheng Weilong, Lu Baoliang. Investigating critical frequency bands and channels for EEG-based emotion recognition with deep neural networks[J]. IEEE Transactions on Autonomous Mental Development, 2015, 7: 162–175.

- [8] 朱嘉祐. 基于脑电信号的情绪识别[D]. 上海: 上海交通大学, 2013.

- [9] 张冠华, 余曼婧, 陈果, 等. 面向情绪识别的脑电特征研究综述[J]. 中国科学: 信息科学, 2019, 49(9): 1097–1118.

- [10] Wang Xiaowei, Nie Dan, Lu Baoliang. EEG-based emotion recognition using frequency domain features and support

- [4] 解同同, 李天阳. 一种嵌入式 NOR Flash 控制器 IP 的设计[J]. 电子与封装, 2016, 16(7): 18–21, 43.

- [5] 徐立国, 李德建, 于宝东, 等. 一种支持在线升级的 NOR Flash 控制器设计[J]. 电子技术应用, 2019, 45(10): 50–57.

- [6] 闵嘉维, 王亚刚, 焦继业, 等. 高速串行 Flash 控制器的设计与实现[J]. 信息技术, 2018, 42(7): 148–150, 161.

- [7] 罗军, 王小强, 蔡志刚, 等. Flash 存储器并行耐久测试方法[J]. 中国测试, 2016, 42(5): 24–27.

- [8] 杨富征. Flash 存储器的测试技术[J]. 电子制作, 2020(18): 62–63.

(收稿日期: 2022-03-01)

## 作者简介:

钱劲宇(1993-), 男, 硕士研究生, 助理工程师, 主要研究方向: 数字 IC 设计。

强小燕(1978-), 女, 本科, 工程师, 主要研究方向: SoC 集成电路设计和验证。

屈凌翔(1981-), 男, 本科, 工程师, 主要研究方向: SoC 集成电路设计和验证。

扫码下载电子文档

vector machines [J]. Lecture Notes in Computer Science (Including Subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics), 2011, 7062(1): 734–743.

- [11] Yan Tongtong, Wang Dong, Xia Tangbin, et al. Investigations on generalized Hjorth's parameters for machine performance degradation assessment[J]. Mechanical Systems and Signal Processing, 2021, 168: 108720–108734.

- [12] 杨富. 基于 EEG 的跨被试情绪识别研究[D]. 西安: 西北工业大学, 2020.

- [13] Shi Lichen, Jiao Yingying, Lu Baoliang. Differential entropy feature for EEG-based vigilance estimation [C]// Annual Conference, 2013: 6627–6630.

- [14] RAHMAN M A, HOSSAIN M F, HOSSAIN M, et al. Employing PCA and t-statistical approach for feature extraction and classification of emotion from multichannel EEG signal[J]. Egyptian Inform, 2020, 21: 23–35.

- [15] 陈振洲, 李磊, 姚正安. 基于 SVM 的特征加权 KNN 算法[J]. 中山大学学报(自然科学版), 2005, 44(1): 17–20.

(收稿日期: 2022-01-05)

## 作者简介:

蔡婧(1979-), 通信作者, 男, 硕士, 高级工程师, 主要研究方向: 医疗仪器, E-mail: caijing1979@jlu.edu.com。

袁守国(1999-), 男, 本科, 主要研究方向: 生物信号检测。

李锐(2000-), 男, 本科, 主要研究方向: 生物信号检测。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所