# 一种基于海思芯片的网络监控图像处理平台设计

张 禹,钱宏文,王 毅

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

**摘要:** 针对目前工业现场、安防监控领域、汽车电子行业摄像采集环境搭建复杂、成本高、功能单一的现状,设计和开发了一种基于海思芯片的网络监控图像处理平台。平台设计采用 NVR 与 DVR 相结合的方式,既可以同时观看、浏览、回放、管理、存储多个网络摄像机视频流,又可以进行图像计算,具有对图像/语音和动态帧控制的功能。系统采用海思 HI3559AV100+HI3531DV200 双 CPU 的设计架构,利用 HI3559AV100 出色的视频处理能力,HI3531DV200 优异的编解码能力,系统包含 CPU 基本系统、高清视频接口电路和电源电路等。该平台能够通过网络接收视频流,最高解码能力达到 16 路 1080p30,支持 2 组高清异源输出。该设计经过实际工程样机验证,图像输出清晰流畅,系统运行稳定。可满足不同场景下应用要求,并且还具有操作简单、适用性广的优点。

**关键词:** NVR; DVR; HI3559AV100; HI3531DV200; 网络监控

中图分类号: TN02

文献标识码: A

DOI: 10.16157/j.issn.0258-7998.222597

中文引用格式: 张禹,钱宏文,王毅. 一种基于海思芯片的网络监控图像处理平台设计[J]. 电子技术应用, 2022, 48(10): 118-122, 128.

英文引用格式: Zhang Yu, Qian Hongwen, Wang Yi. Design of a network monitoring image processing platform based on Hisilicon chip[J]. Application of Electronic Technique, 2022, 48(10): 118-122, 128.

## Design of a network monitoring image processing platform based on Hisilicon chip

Zhang Yu, Qian Hongwen, Wang Yi

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** Aiming at the current status quo that in industrial site, security monitoring field and automotive electronics industry camera acquisition's environment building is complex, the cost is high, and the function is single, this paper designs and develops a network monitoring image processing platform based on HiSilicon chip. The platform is designed to use a combination of NVR and DVR, which can not only view, browse, play back, manage, and store multiple network camera video streams at the same time, but also perform image calculations, with the function of image/voice and dynamic frame control. The system adopts the design architecture of HiSilicon HI3559AV100+HI3531DV200 dual CPU, utilizes the excellent video processing capability of HI3559AV100, the excellent codec capability of HI3531DV200, the basic system of the system package CPU, the high-definition video interface circuit and the power supply circuit. The platform can receive video streams through the network, with a maximum decoding capacity of 16 channels of 1080p30, and supports 2 sets of high-definition heterologous outputs. The design has been verified by the actual engineering prototype, the image output is clear and smooth, and the system runs stably. It can be used to meet the application requirements of different scenarios, and also has the advantages of simple operation and wide applicability.

**Key words:** NVR; DVR; HI3559AV100; HI3531DV200; network monitoring

## 0 引言

随着社会经济的快速发展,数字图像处理的应用愈来愈广泛,现在在安防监控、工业现场、汽车电子等领域数字图像处理的要求进一步提升。图像处理系统一般由视频采集、视频处理、视频传输、视频显示、视频记录五部分组成<sup>[1]</sup>。目前主流的监控相机接口有 SDI<sup>[2]</sup>、S-Video、MIPI、DVP、网口等,其中 MPI 与 DVP 不适合长距离传输应用场景;SDI 是利用同轴电缆来传输非压缩的数字视频信号,S-Video 是一种五芯接口,由两路视亮度信号、

两路视颜色度信号和一路公共屏蔽地线共五条芯线传输视频信号,这两种制式信号理论上可以长距离传输,但是线缆成本及长距离传输线缆上的损耗永远是个难以均衡的因素。至此网络摄像头就脱颖而出,可以长距离传输有能保障信号质量,对高视频分辨率的要求仅受限于网络传输带宽。通过高压缩率的编码技术,可以解决实现高分辨率全景视频的网络传输。其次现有的 NVR、DVR 设备或图像处理系统,要么仅在编解码或处理方向功能出色,要么系统体积庞大、移动不便、安装困难<sup>[3]</sup>。

基于以上背景和需求,本文设计开发了一种基于海思芯片的网络监控图像处理平台,解决当前所面临的一系列问题,对于推动图像处理系统的发展具有重大的意义。

## 1 设计思路及系统组成

### 1.1 设计思路

本设计中主板电路采用双 CPU 硬件架构,其中主 CPU 选用海思 HI3559AV100。HI3559AV100 是专业的 8K Ultra HD Mobile Camera SoC,它提供了 8K30/4K120 广播级图像质量的数字视频录制,支持多路 Sensor 输入,支持 H.265 编码输出或影视级的 RAW 数据输出,并集成高性能 ISP 图像处理功能<sup>[4]</sup>,在图像处理方面有独立的 DSP 和 GPU,支持 OpenGL 和 OpenCL,提供了卓越的图像处理能力,集成了双核 A73 和双核 A53,大小核架构和双操作系统,同时支持 DDR4/LPDDR4,且有 SATA3.0、USB2.0/3.0、PCIE2.0、RGMII、UART、I<sup>2</sup>C、SPI 等丰富的外设接口。

协处理 CPU 选用海思 HI3531DV200。海思 HI3531-DV200 是针对多路高清/超高清(1080P)DVR 产品应用开发的新一代专业 SoC 芯片。海思 HI3531DV200 集成了 ARM A53 四核处理器和性能强大的神经网络推理引擎,支持多种智能算法应用<sup>[5]</sup>,同时支持 DDR4/DDR3,且有 SATA3.0、USB2.0/3.0、PCIE2.0、RGMII、UART、I<sup>2</sup>C、SPI 等丰富接口。

两个 CPU 通过 PCIE 进行级联,主 CPU 可完成目标识别、环视拼接、神经网络学习等图像处理能力,协处理 CPU 可专注于流媒体存储/转发及回放。两个 CPU 协同工作,完成视频信号采集、视频信号处理、通信、存储、视频输出等功能。

### 1.2 系统组成

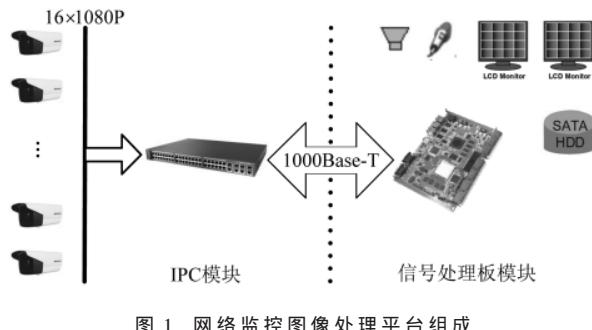

系统主要由信号处理板模块和网络 IPC 模块两部分组成(如图 1 所示),信号处理模块主要完成视频信号采集、视频信号处理、通信、存储、视频输出功能;IPC 模块

图 1 网络监控图像处理平台组成

主要完成多路网络接口的扩展,通过网络对视频进行传输和显示<sup>[6]</sup>。两个模块可独立工作,当两个模块协同工作时可完成最多 16 路网络视频的同时采集。

## 2 系统设计

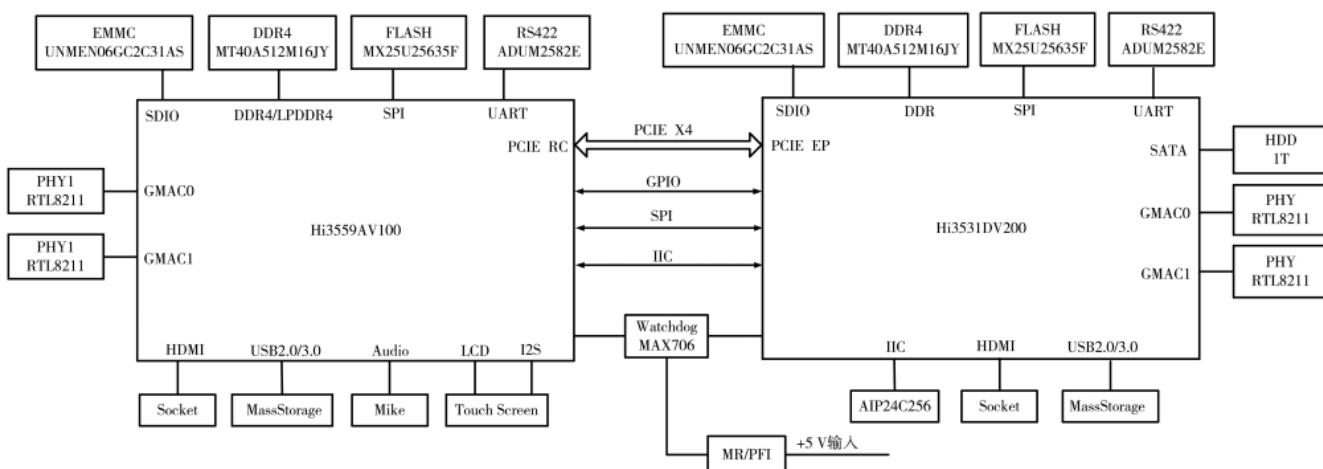

图 2 是系统框图,包括 HI3559、HI3531 基本系统、网络接口、高清输出接口、音频 codec 接口、串口、SATA 等。

CPU 采用外挂 SPI NOR Flash 来实现 BIOS 的引导,同时对外引出串口、网络接口、HDMI 显示接口、SATA 存储接口,CPU 和 CPU 之间通过 PCIE 总线来进行数据交互。

### 2.1 DDR4 SDRAM 电路

HI3559AV100 处理器内部集成有 DDRC(DDR SDRAM Controller)实现对动态存储器 DDR4/LPDDR4 SDRAM 的存取控制。DDRC 支持 DDR4/LPDDR4 SDRAM 总线最高工作频率为 1 333 MHz,即数据速率为 2.666 Gb/s。可支持最大存储空间为 8 GB,支持 DDR4/LPDDR4 SDRAM 的 Power Down、Self Refresh 等低功耗模式。DDR4 SDRAM 支持 burst8 传输模式,LDDR4 SDRAM 支持 burst16 传输模式,支持 INCR 和 WRAP 命令,不支持 FIXED。

HI3531DV200 处理器内部集成有 DDRC(DDR SDRAM Controller)实现对动态存储器 DDR3/DDR4 SDRAM 的存取控制。DDRC 的功能特点:支持最大存储空间为 8 GB。仅支持小端存储模式。支持 DDR3 SDRAM 接口最高工作

图 2 网络监控图像处理平台整体框图

频率为 1 066 MHz, 即数据速率为 2.13 Gb/s。支持 DDR4 SDRAM 接口最高工作频率为 1 200 MHz, 即数据速率为 2.4 Gb/s。支持 DDR3/DDR4 SDRAM 的 Power Down 低功耗模式。支持双通道设计选用 4 片的 MT40A512M16JY 实现总容量 4 GB 的内存扩展。该芯片具有 16 根数据线和 15 根地址线, 选用标准 DDR4 电源供电和上电时序要求。

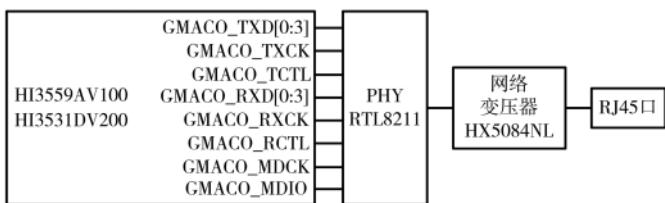

## 2.2 以太网接口电路

HI3559AV100 及 HI3531DV200 均支持 2 个 GMAC 模块, 千兆以太网模块实现网络接口数据的接收和发送, 支持 10/100/1000 Mb/s 自适应的工作模式, 支持全双工、半双工的工作模式, 可实现和 CPU 端口间的数据通信和交互。以太网口设计框图如图 3 所示。

图 3 以太网口设计框图

网口设计是本设计核心接口, 其他 HI3559AV100 的两个 MAC, 一个用于 TELNET 调试, 一个接二级交换机扩展, 上下行均 1 000 Mb/s 带宽, 可实现多路网络摄像头视频流采集, 在特殊场景下, 两个 MAC 均可进行二级交换机扩展, 在此需要针对网络摄像头数据带宽具体核算系统采样带宽是否满足要求, 本系统网络摄像头带宽为 4 MB/s, 前端采用 H.265 进行压缩, H.265 编码在传输相同质量视频情况下能够大约节省一半带宽<sup>[7]</sup>。

HI3531DV200 的两个 MAC, 一个用于 RTSP 流媒体转发、网络视频的点播、异地读取等功能, RTSP 是一种网络远程视频播放协议, 可以使用户远程观看并控制网络视频<sup>[8]</sup>。另一个网络接口作为调试。

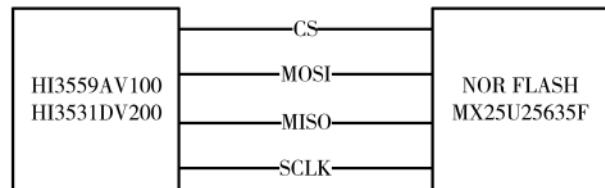

## 2.3 系统启动电路

海思 HI3559AV100 和 HI3531DV200 处理器支持 eMMC、UFS、SPI NOR Flash、SPI NAND Flash、NAND、PCIE 五种系统启动输入方式, 本设计选用 SPI NOR Flash 启动方式。海思处理器集成的 SPI 控制器实现数据的串并、并串转换, 可以作为 Master 与外部设备进行同步串行通信。支持 MOTOROLA 的 SPI、TI 串行同步、MicroWire 三种外设接口协议。SPI 接口设计选用 MX25U25635F 用于 U-Boot 存放和系统启动。系统启动部分的硬件设计框图如图 4 所示。

## 2.4 SATA 接口电路

HI3531DV200 支持 4 个 SATA 接口, 支持 NCQ(Native Command Queuing)、热拔插、PM(Port Multiplier)、FBS(Frame information structure-Based Switching)、eSATA(externalSATA)、电源管理等特性; 支持 SATA3.0 和 AHCI1.3 协议, 向下

图 4 系统启动硬件设计框图

兼容 SATA2.6 和 AHCI1.2 协议; 支持 PIO、Legacy DMA、NCQ 操作; 支持电源管理特性。支持 PM 和 FBS 特性。支持 4 个 SATA 接口; 支持 1.5 Gb/s、3.0 Gb/s 和 6.0 Gb/s 速率的自动协商; 支持错误中断上报机制, SATA 协议采用差分线进行信号传输, 具备更好的抗干扰性能<sup>[9]</sup>。设计选用 HT10MCNNNN-1TB 实现 SATA 存储功能。

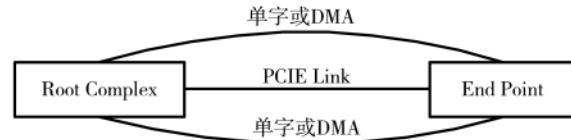

## 2.5 PCIE 部分设计

HI3559AV100 及 HI3531DV200 中 PCIe 控制器, 支持一个 PCIe Gen2X2 控制器, 支持 RC 模式, 支持 EP 模式, 支持 DMA 功能, 支持 INTx 中断机制。支持 MSI 中断机制。其中将 HI3559AV100 作为根节点(RC)设备, 另一块做端点设备(EP), RC 设备作为系统的 CPU 通过枚举过程配置这个系统, 包括自身 EP 设备。枚举结束之后, 通过 HI3559AV100 向 HI3531DV200 发送需要存储的视频流。

图 5 PCIE 部分设计框图

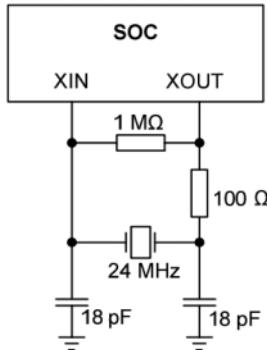

## 2.6 时钟设计电路

CPU 系统时钟通过芯片内部的反馈电路与外部的 24 MHz 晶体振荡电路一起构成系统时钟, 按照官方推荐选择选用 4 pin 贴片晶振, 其中 2 个 GND 管脚与单板地充分连接, 增强系统时钟抗干扰能力。其他的走线远离晶振区域, 防止对系统造成干扰。

图 6 时钟设计框图

另外, 海思内置 RTC, 当需要开关机实时显示时间数据时, 单板需要给 RTC 提供时钟电路。RTC 晶体选型的约束: 晶体内阻不超过 70 kΩ; 晶体的最大功耗(DL)为 0.5 μW。

## 2.7 EEPROM 接口电路

EEPROM 是带电可擦可编程只读存储器, 是一种掉电后数据不丢失的存储芯片, 因此能够有效地存放一些关键的监控信息和系统的温度数据等。EEPROM 设计选用 AiP25C256, 其容量为 256 Kb, 存储器的结构为 32 768 ×

8 bit, 内部分为 512 页, 每页 64 B, 采用 I<sup>2</sup>C 接口, 广泛应用于低功耗、低电压系统。

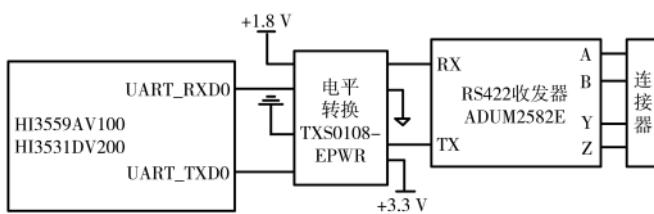

### 2.8 RS422 接口电路

海思 HI3559AV100 及 HI3531DV200 处理器主 SoC 子系统提供 5 个 UART 单元, 该控制器兼容国际工业标准半导体设备 16550A, 通过 APB 总线与总线桥通信。其他 UART0 主要用于调试。

RS422 收发器芯片使用 ADUM2582E, 电平转换芯片选用 TXS0108EPWR 来实现 3.3 V 对 1.8 V 的电平转换。RS422 接口的硬件设计框图如图 7 所示。

图 7 RS422 电路设计框图

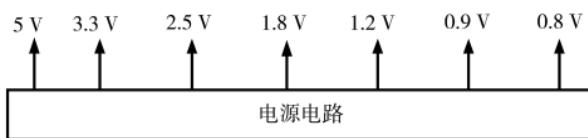

### 2.9 电源设计

该系统的电源包括 5 V、3.3 V、2.5 V、1.8 V、1.5 V、1.2 V、1.0 V、0.9 V、0.8 V 等多路, 0.8 V、0.9 V 分别为 HI3559AV100、HI3531DV200 的核供电, 1.2 V 为 DDR 控制器和 DDR4 供电, 1.8 V 为 Flash、HI3559AV100 PHY 供电, 5 V 为视频 Buffer 及 SATA 盘供电, 3.3 V 为 HI3531-DV200 IO 及外设供电, 2.5 V 为 HI3531DV200 PHY 供电。电源部分有上电顺序控制, 满足海思 CPU 对各部分上电顺序要求。

图 8 电源电路设计框图

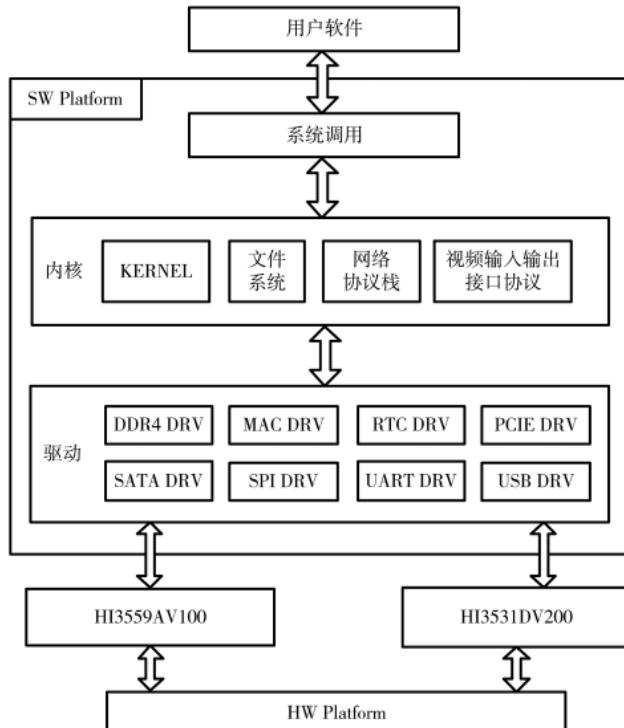

## 3 软件设计

软件运行于控制板, 由系统引导软件、操作系统软件和驱动接口软件组成, 各软件功能如下。

### 3.1 系统引导软件

系统引导软件是控制板上电后首先加载的一段程序软件, 该软件负责对控制板主处理器, 即处理器资源进行初始化, 包括初始化中断、内存、串口、GPIO、以太网以及启动 TFTP 服务、调试等功能。本项目的系统引导软件选用 UBOOT 软件。UBOOT 是一个兼有 BIOS 和 BOOTLOADER 部分功能的软件代码, 多用于嵌入式系统, 其支持 ubifs、ext2、ext3 和 ext4 等文件系统, 支持网络、PCIE、EMMC、Nor/Nand Flash 引导。系统引导软件主要用于引导以及升级操作系统软件, 并与其他软件相互独立, 与用户上层应用不对接, 用户所需功能均在操作

系统软件和驱动接口软件代码中实现。

### 3.2 操作系统软件

操作系统软件是系统运行的基础, 该软件提供应用所需的进程管理、内存管理、文件系统、网络通信、安全机制、驱动程序等基础功能, 为实现系统控制、数据通信提供可能。

操作系统软件采用 Linux 操作系统, Linux 系统由于具有内核源码开放、免费使用、可移植性高、跨平台支持性好、易于裁剪等特点, 被广泛应用于嵌入式领域。

### 3.3 软件架构

系统完成引导系统并加载用户程序后, 其软件总体架构如图 9 所示。

图 9 网络监控图像处理平台 Linux 软件整体框图

## 4 测试与验证

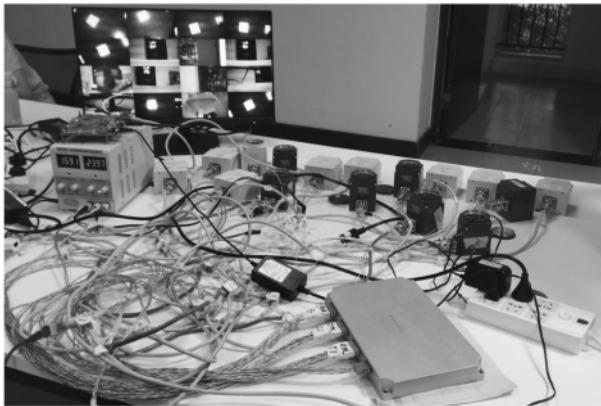

利用本次设计开发的平台进行测试和验证, 板卡通过对接 16 路的网络摄像头, 可以完成最多 16 路不同 1080P 的网络摄像头数据的获取, 板卡通过拼接和裁剪处理后, 发送至 HDMI 高清视频输出接口进行显示。系统设计开发平台如图 10 所示, 视频处理完成后多路视频测试显示图如图 11 所示, 通过测试完成了该平台的设计开发和验证。

## 5 结论

本文设计研发的基于海思芯片的网络监控图像处理平台, 通过实际样机验证, 可实现对高清 IPC 和 DVR 视频流解码, 视频流存储。同时实现了图形裁剪, OpenCL 图层叠加、环视拼接、流媒体点播等功能, 图像清晰流畅, 运行稳定, 成本低廉, 达到预期设计目标。系统具有

图 10 系统设计测试环境

操作简单方便、成本低、适用性广的优点,具有较高的推广和应用价值。

#### 参考文献

- [1] 杨念,李峰.基于 B/S 的嵌入式视频监控系统的设计与实现[J].计算机工程与设计,2008(21):5576-5579.

- [2] 徐大鹏.HD-SDI 视频嵌入式图像采集设计[J].计算机测量与控制,2015,23(9):3214.

- [3] 陈明伟,徐丹.球面坐标定位校正鱼眼图片并合成全景

(上接第 117 页)

用短数据报传输信息且级联规模不大的局域网系统。

#### 4 结论

本文介绍了一种在国产化 FPGA 平台上使用光导纤维传输介质实现万兆通信的 UDP/IP 协议接口。该协议接口充分运用开源的万兆以太网 MAC IP 核与 PCS/PMA IP 核,使得开发过程便捷、简单。应用分支预测机制,进一步减少局域网内短数据报的发送时延。使用本文方法实现的 UDP/IP 协议接口占用资源低,能够灵活应用到其他的设计中。研究内容对高速数据采集、远距离信息传输、片上数据高速处理等应用场景有一定的借鉴意义。此外,对航天、能源、国防等使用国产化器件要求较高的特定领域具有一定的参考价值。

#### 参考文献

- [1] 冯一飞,丁楠,叶钧超,等.领域专用低延迟高带宽 TCP/IP 引擎设计与实现[J].计算机工程,2021.

- [2] 王祎辰.基于 FPGA 的万兆以太网 TCP 协议栈设计[D].北京:北京理工大学,2016.

- [3] 熊雪均,谭力波,张俊杰,等.基于 FPGA 的低延迟 TCP 协议栈实现[J].电子测量技术,2020(10):43-48.

- [4] 于波,李建成,张强,等.基于 FPGA 的振动采集监控系统[J].电子测量技术,2021,44(14):33-37.

- [5] 于波,栾海鹏,韩玉斌.基于 FPGA 的以太网视频传输系统[J].电子测量技术,2020,43(8):138-142.

- [6] 柯洋.基于 FPGA 的高速数据传输板设计与开发[D].武汉:华中师范大学,2020.

图 11 多路视频测试显示图

图的方法[J].云南民族大学学报(自然科学版),2004(3):214-217.

- [4] 华为海思半导体有限公司.Hi3559A/C V100 ultra-HD Mobile Camera SoC 用户指南[Z].2018.

- [5] 华为海思半导体有限公司.Hi3531DV200 H.265 编解码 AI 处理器用户指南[Z].2018.

- [6] GUALDI G, PRATI A, CUCCHIARA R. Video Streaming for mobile video surveillance[J]. IEEE Transactions on Multimedia, 2010, 12(1): 1-10.

- (下转第 128 页)

- [7] 吴惑,刘一清.基于 FPGA 的万兆以太网 TCP/IP 协议处理架构[J].电子设计工程,2020,28(9):81-87.

- [8] Liu Nianyun, Xu Zhiqiang. The design of high-speed hardware UDP/IP stack based on FPGA for large-scale sensing systems[J]. 因特网技术学刊,2017,18(3):579-587.

- [9] 刘源,张刚.可靠 UDP 协议栈的 FPGA 实现[J].火力与指挥控制,2017,42(7):139-143.

- [10] 孔德伟,袁国顺,刘小强.基于 FPGA 的万兆以太网链路的设计与实现[J].微电子学与计算机,2019,36(12):21-25.

- [11] 李涛,韩鹏,候冠东,等.基于 FPGA 的 ORUDP 协议栈设计与实现[J].计算机工程,2020,46(6):155-163.

- [12] 王文,郑建生.基于 FPGA 的 TCP/IP 网络通信系统的设计与实现[J].现代电子技术,2018,41(8):5-9.

- [13] 王永超,刘超,王健,等.基于 FPGA 的多角度周转箱图像采集系统设计[J].自动化仪表,2019,40(10):35-38.

- [14] 许川佩,刘华颖.通用型芯片级光纤通信接口设计[J].微电子学与计算机,2019,36(11):24-29.

(收稿日期:2022-02-10)

#### 作者简介:

赵世超(1995-),通信作者,男,硕士研究生,主要研究方向:通信保密,E-mail:zhaoshichao\_cn@qq.com。

左金印(1967-),男,硕士,高级工程师,主要研究方向:通信保密。

魏晓(1990-),男,硕士,工程师,主要研究方向:通信保密。

扫码下载电子文档

关管  $S_1$ 、 $S_2$  的驱动电压  $V_{GS1}$  和  $V_{GS2}$ ；中间部分为开关管  $S_1$ 、 $S_3$  的驱动电压，可以看出，由于单元  $M_1$  的电压比单元  $M_2$  高，驱动信号移相， $V_{GS1}$  超前于  $V_{GS3}$ ；下面部分为  $L_1$ 、 $C_1$  串联支路两端电压  $V_{LC}$  和流过电感  $L_1$  的电流  $i_{L1}$ ，可以看出其波形和理论分析基本一致。

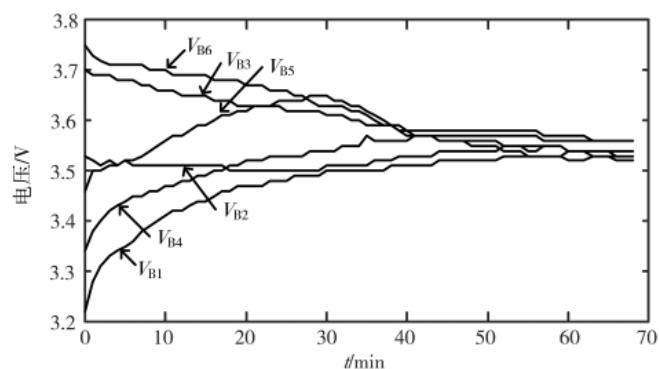

然后，以 6 节电池(3 个单元)为均衡对象，其初始电压分别为  $V_{B1}=3.22$  V,  $V_{B2}=3.53$  V,  $V_{B3}=3.70$  V,  $V_{B4}=3.34$  V,  $V_{B5}=3.46$  V,  $V_{B6}=3.75$  V。均衡过程中的电池电压波形如图 16 所示，其中电压数据的测量间隔时间为 1 min。可以看出，在 57 min 时 6 节电池的最大电压差就已经从初始的 0.53 V 降低到 0.04 V，验证了该均衡电路的有效性。

图 16 电池电压实验波形

#### 4 结论

本文提出了一种基于开关电感和 Star 型连接的 LC 串联支路的均衡电路，两层均衡电路共用一组开关管，具有开关管数量少、拓扑简单和易于工程实现的优点。根据该均衡电路的结构和工作原理，本文建立了相应的数学模型并提出了一个简单有效的移相控制的电压均衡策略。仿真和实验结果与模型推导结果基本一致，验证了理论分析的正确性；同时，仿真和实验均实现了电池的电压均衡，从而表明了所提出的均衡电路的有效性。

#### 参考文献

- [1] 林小峰, 王志浩, 宋绍剑. 基于双层结构的锂电池主动均衡控制系统[J]. 电子技术应用, 2016, 42(1): 119–122.

- [2] 郭俊. 光伏储能主从式锂电池管理系统设计与实现[D].

- ……

- (上接第 122 页)

- 2008, 10(6): 1142–1154.

- [7] 刘国梁. 从 H.264 向 H.265 的数字视频压缩技术升级[J]. 铁路通信信号工程技术, 2011, 8(3): 43–47.

- [8] 李罗涛. 基于 RTSP 的 H.264 实时流媒体传输方案的研究与实现[D]. 广州: 华南理工大学, 2014.

- [9] ZHANG F Q, LI Z Y. The technical differences between serial ATA and ultra ATA technology[C]//2009 International Forum on Information Technology and Applications. Chengdu: IEEE.

成都: 电子科技大学, 2020.

- [3] PASCUAL C, KREIN P T. Switched capacitor system for automatic series battery equalization[C]//Proceedings of APEC 97—Applied Power Electronics Conference, 1997: 848–854.

- [4] GAO J, SCHOFIELD N, EMADI A. Battery balancing methods: a comprehensive review[C]//Vehicle Power and Propulsion Conference, 2008: 1–6.

- [5] 李泉, 周云山, 王建德, 等. 基于双层准谐振开关电容的锂电池组均衡方法[J]. 电工技术学报, 2017, 32(21): 9–15.

- [6] KIM M, KIM C, KIM J, et al. A chain structure of switched capacitor for improved cell balancing speed of lithiumion batteries[J]. IEEE Transactions on Industrial Electronics, 2014, 61(8): 3989–3999.

- [7] FUKUI R, KOIZUMI H. Double-tiered switched capacitor battery charge equalizer with chain structure[C]//39th Annual Conference of the IEEE Industrial Electronics Society, 2013: 6715–6720.

- [8] 文楚强, 赵世伟. 基于 Delta 型准谐振开关电容的锂电池组电压均衡电路[J]. 电子技术应用, 2020, 46(5): 97–101.

- [9] YE Y, CHENG K W E, FONG Y C, et al. Topology, modeling, and design of switched-capacitor-based cell balancing systems and their balancing exploration[J]. IEEE Transactions on Power Electronics, 2017, 32(6): 4444–4454.

- [10] 廖武兵, 陈渊睿, 刘润鹏. 基于星型零电流开关电容的电压均衡电路[J]. 广东电力, 2021, 34(3): 77–84.

- [11] JI W, LU X, JI Y, et al. Low cost battery equalizer using buck-boost and series LC converter with synchronous phase-shift control[C]//Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition(APEC), 2013: 1152–1157.

(收稿日期: 2022-03-07)

#### 作者简介:

吴磊威(1996-), 男, 硕士研究生, 主要研究方向: 直流微电网、电池管理系统。

赵世伟(1977-), 男, 博士, 副教授, 主要研究方向: 直流微电网、电机控制。

杨向宇(1963-), 男, 博士, 教授, 主要研究方向: 新型特种电机设计、电机及其系统的智能控制。

扫码下载电子文档

2009: 659–663.

(收稿日期: 2022-01-25)

#### 作者简介:

张禹(1993-), 男, 本科, 工程师, 主要研究方向: 数字信号处理、DSP、FPGA 应用。

钱宏文(1975-), 男, 本科, 研究员级高级工程师, 主要研究方向: 集成电路应用和微系统。

王毅(1991-), 男, 硕士, 工程师, 主要研究方向: 数字图像处理、DSP、FPGA 应用。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所