# 一种用于 PCIe 多通道的 De-skew 电路设计

王可扬,吉 兵,屈凌翔

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

**摘要:** 在 PCIe 多通道数据传输过程中,当各通道数据到达时间不一致时,会引入相位偏移(Skew)问题。为了保证每条通道的接收端能够同时且正确处理接收到的数据,需要对传输数据进行预处理。提出了一种 De-skew 逻辑电路,利用同步 FIFO 实现了多通道的 De-skew,完成了相应的逻辑设计。并利用 UVM 以及 VIP 技术搭建了验证平台,测试结果验证了设计的正确性和可行性。与其他常用解决方案对比表明,该逻辑设计具有全面性、优越性和可复用性。

**关键词:** PCIe ; De-skew ; 多通道 ; FIFO

中图分类号: TN402

文献标识码: A

DOI:10.16157/j.issn.0258-7998.222775

中文引用格式: 王可扬,吉兵,屈凌翔. 一种用于 PCIe 多通道的 De-skew 电路设计[J]. 电子技术应用, 2022, 48(11): 63–66, 73.

英文引用格式: Wang Keyang, Ji Bing, Qu Lingxiang. De-skew circuit design for PCIe multi-lane[J]. Application of Electronic Technique, 2022, 48(11): 63–66, 73.

## De-skew circuit design for PCIe multi-lane

Wang Keyang, Ji Bing, Qu Lingxiang

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214072, China)

**Abstract:** In the process of multi-lane data transmission in PCIe, when the arrival time of data in each lane is inconsistent, the issue of skew will be introduced. In order to ensure that the receiver of each lane can process the received data simultaneously and correctly, it is necessary to preprocess the transmitted data. This paper presents a De-skew logic circuit, which explains how to use synchronous FIFO to realize multi-lane De-skew and complete the corresponding logic design. UVM and VIP technology are used to build a verification platform, the test results verify the correctness and feasibility of the design. Compared with other common solutions, the logic design has comprehensiveness, advantages and reusability.

**Key words:** PCIe ; De-skew ; mult-lane ; FIFO

## 0 引言

PCI-Express(Peripheral Component Interconnect Express, PCIe)作为第三代高性能通用 I/O 总线技术,可以视作是 PCI 总线的改进版本。它不单继承了 PCI 的一些良好特性,实现了 PCI 总线协议全部软件的向下兼容<sup>[1-2]</sup>,同时,在总线结构上进行了革命性的改变:一是从并行式变为了串行式,二是采用了点对点的互连技术<sup>[3]</sup>。此外,PCIe 也支持如热插拔、功耗管理、质量服务等高级特性<sup>[4]</sup>。

目前 PCIe5.0 可支持最快 32 GT/s 的传输速率,同时,不仅支持单通道数据传输,也可以支持 2 路、4 路、甚至 32 路的多通道数据传输。然而,在 PCIe 进行多通道数据传输时,即使使用同样的时钟源从发送端进行数据发送,如果不在接收端进行处理,仍然无法保证所有通道的数据能够同时抵达接收端<sup>[5]</sup>。因此各个通道间就会存在时差,这是因为实际电路中存在数据的传输延时。导致延时的因素有:(1)各通道信号线的长度不同;(2)线路板在印刷时的阻抗存在差别;(3)由于数据的串

化和解串引入延迟;(4)外部因素例如温度的影响等<sup>[6-7]</sup>。

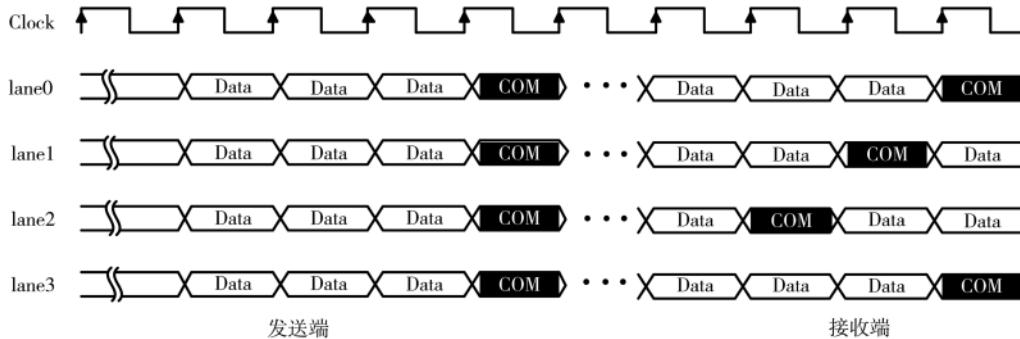

因为各通道的延时来源不尽相同,必然使得各通道上的延时也有所区别。这也给消除多通道数据传输的延时误差带来了更大的设计压力。图 1 所示为以四通道为例的情况。

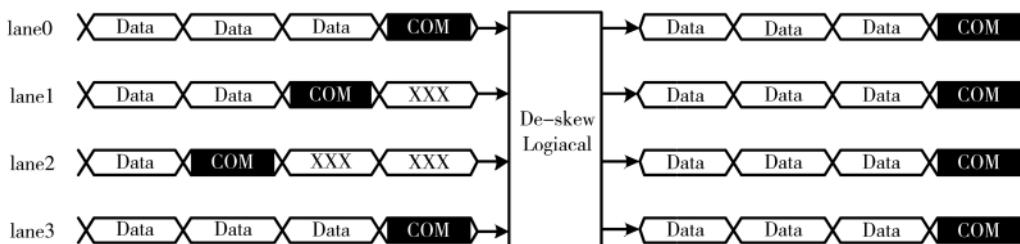

如图 1 所示,接收端在接收到各通道传送来的数据后需要经过反数据剥解逻辑,即由数据发送时的剥解顺序来进行数据合并。如果各通道上的数据在同一时间点并未对齐,那么接收端就无法正确地进行数据合并,从而产生顺序混乱的数据包并发送到数据链路层。这是不被允许的,所以接收端必须对各通道间的相位偏移进行消除,以保证多通道数据能够在同一时间点到达接收端进行后续处理。该过程被称为链路的多通道纠偏(Lane-to-Lane De-skew),图 2 所示为四通道的 De-skew 过程。

本文提出了一种 De-skew 逻辑电路设计,能够在不预先知晓哪路数据先到达的情况下消除各通道间的偏移现象,同时满足通道间 skew 最大值的约束要求。该逻

图 1 数据传输中产生的 skew 现象

图 2 接收端的 De-skew 处理

辑方案也可以应用于 PCIe 以外的其他任何电路中多通道间相位偏移的处理。

## 1 De-skew 逻辑设计

### 1.1 常见 De-skew 实现方法

PCIe 协议规范中对多通道 De-skew 做了一些规则要求,但并未规定实现 De-skew 的具体方法。目前主要的实现方法是借助 TS1/TS2 以及 FTS 等有序集。因为这些有序集具有特定的结构和长度,且在所有通道上遵循同时发送的规则,因此可以用来作为衡量各通道间偏移量的标志。在 PCIe 协议规范中,针对第一代/第二代(Generation one/Generation two, Gen1/Gen2)和第三代/第四代(Generation three/Generation four, Gen3/Gen4)所要实现的 De-skew,建议利用不同的有序集,具体如下<sup>[8]</sup>:

(1)Gen1/Gen2 中建议使用以下一个或多个作为衡量标志:TS1/TS2 有序集的 COM 字符(有序集的头字节)、EIEOS 有序集的 COM 字符、在 FTS 序列后紧接着的第一个 SKP 有序集的 COM 字符、不使用 SRIS 时在训练序列中的 SKP 有序集的 COM 字符。

(2)Gen3/Gen4 中建议使用以下一个或多个作为衡量标志:SDS 有序集、退出 L0s 状态时的 EIEOS 有序集、Gen3 时的 SKP 有序集、Gen4 时的 FTS 序列后紧跟的第一个 SKP 有序集。

目前,国内外常见的 De-skew 电路设计思路多是利用计数器和多个寄存器进行设计实现。该方法使用多个寄存器进行数据的缓存移位,每两个寄存器间加一个选择器用来控制数据是否进入寄存器进行缓存。同时,在每条通道上添加一个计数器,当每一路的数据到达第一个寄存器时就开始计数<sup>[9]</sup>。计数器可以用来观察各条通

道上的数据何时到达,也可以观察各通道数据分别经过了多少个寄存器。更重要的是,通过各通道计数器的数值做差可以算出各通道间的 skew 大小并判断其是否超过所允许的最大值。但该方法实现需要的寄存器数量较多,尤其在 Gen3/Gen4 速率下,由于每秒内传输数据量的加大,代码实现会更为冗长复杂。即使速率不变,随着设计频率以及数据位宽的改变,寄存器数量也会发生改变,因而整个 De-skew 代码的实现需要进行大量变动。针对上述问题,本文提出了一种新颖的逻辑设计,可有效降低逻辑设计的复杂度,同时拥有很强的代码复用性。

### 1.2 利用 FIFO 的 De-skew 逻辑设计

针对如何消除多通道的 skew 问题,本文提出了一种利用同步 FIFO 实现 De-skew 的逻辑电路。

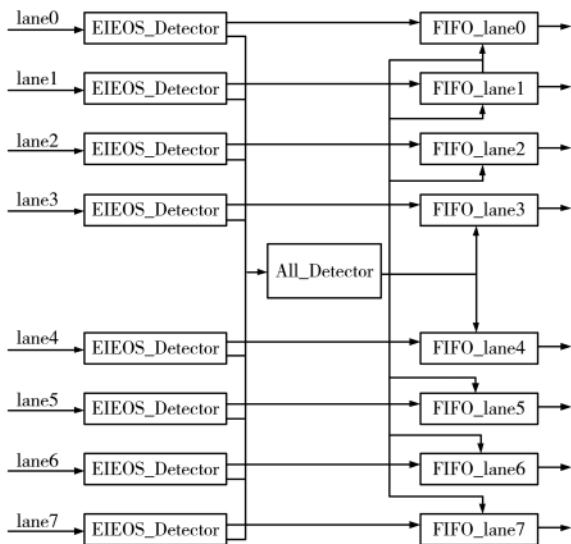

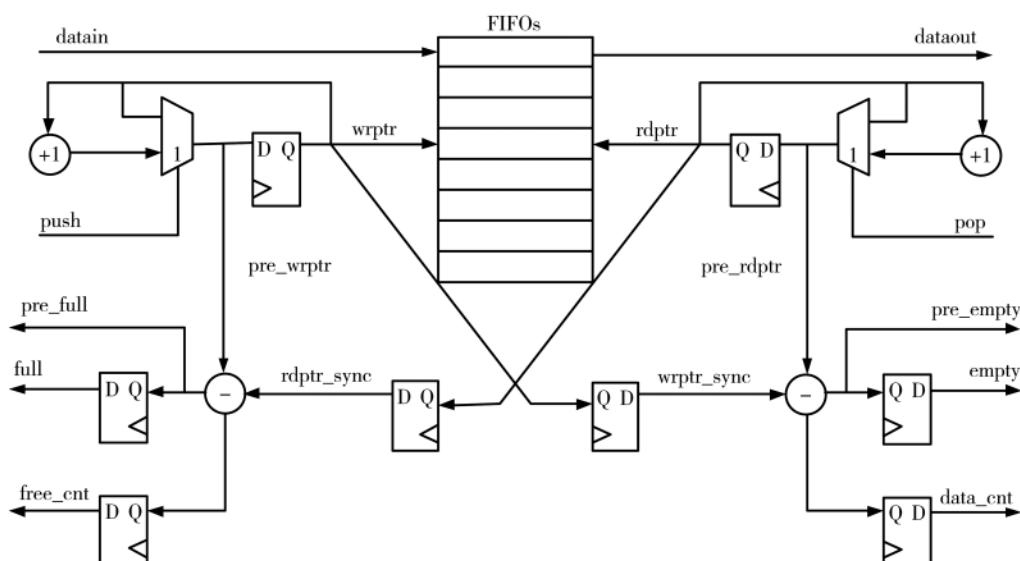

以 Gen3 速率下的八通道传输情况为例,结构如图 3 所示。在每条通道后接入一个同步 FIFO(FIFO 结构如图 4 所示),FIFO 作为一种先进先出的数据寄存器,保证了数据流按顺序写入且按顺序读出。在此基础上,本文所提出的 FIFO 结构还能够准确地对 FIFO 的空/满状态进行判断,以保证数据正确地写入或者读出。具体实现方式为:采用 EIEOS 有序集作为 Gen3 条件下的 De-skew 衡量标志,当某条通道上检测到 EIEOS 的有序集时,该通道的 FIFO 便会将 push 信号拉高,此时通道上的数据块将会被写入到 FIFO 中进行暂时的缓存。当所有通道上 FIFO 的 push 信号均被拉高时,即所有通道均检测到 EIEOS 有序集且每条通道上的数据块均已写入各个 FIFO 中后,将所有通道上 FIFO 的 pop 信号同时进行拉高。这样,所有通道将同时输出 EIEOS 有序集以及之后的所有数据块,从而实现了各条通道数据的对齐校正功能,

图 3 利用 FIFO 的 De-skew 逻辑电路

完成了通道的 De-skew。

值得注意的是，该逻辑电路所使用的 FIFO 支持位宽和深度的自由配置。通过对这两个参数的配置，进而满足各种不同数据传输速率下的 De-skew 需求。在本设计中，设备工作在 Gen3 条件下，每条通道的数据位宽为 32 bit，时钟频率为 250 MHz，规定各条通道间的 skew 最大值为 32 ns。因此 FIFO 的位宽设置为 32 bit，并合理设置 FIFO 的深度(Deepht)使之能够满足最大 skew 值的要求。由于此时传输的数据流中每个 symbol(字符，长度为 8 bit)对应的传输时间为 1 ns，则各条通道间的 skew 最大为 32 个 symbol 的位置。此时 FIFO 的位宽为 32 bit，即 4 个 symbol 的大小。将 FIFO 的深度设置为 8，这样 FIFO 中能够缓存的数据最多为 32 个 symbol，从而确保了最大 skew 值的要求。假设 lane0 的数据流最先到达接收端并被 push 进其对应的 FIFO 中。而 lane7 的数据流则比

lane0 要晚到 36 ns，即 36 个 symbol 的位置。这样当 lane7 的数据流到达接收端并被 push 进其对应的 FIFO 时，lane0 上的 FIFO 已经被填满。而此时因为 8 条通道的 push 并未全部完成，各 FIFO 的 pop 信号不会被拉高，lane0 会同 lane7 一起往各自 FIFO 中送入数据，这会造成 lane0 的 FIFO 的数据溢出，产生错误，进而产生 De-skew 错误信号。De-skew 错误信号会通知发送端重新进行数据发送，直到通道间 skew 不超过最大规定值，或者超时传输终止。

针对前文所述的传输情况：时钟频率为 500 MHz、数据位宽为 8 bit、最大 skew 值为 20 ns 的 Gen2 速率，只要将 FIFO 配置为位宽为 8 bit，深度为 10，同时将 EIEOS 有序集的检测改为对 COM 字符的检测，便能够轻松实现该情况下的 De-skew 设计。因此，本文提出的逻辑电路结构不仅具有全面性和可实现性，还具有很好的代码复用性。

## 2 仿真与验证

本文采用 Synopsys 公司的 PCIe VIP 以及 AMBA AXI VIP 搭建了验证平台。VIP 作为验证知识产权模块，它是一种预先验证过的内建验证结构，能够提供完整且灵活的应用机制。通常，VIP 是基于标准协议的，可以很方便地将其插入到基于仿真的确认测试中，从而显著提高验证的可复用性及验证效率。PCIe 控制器可以作为 RC(根联合体)或者 EP(终点设备)，将 PCIe VIP 作为 RC，而将待测设计作为 EP 进行验证。

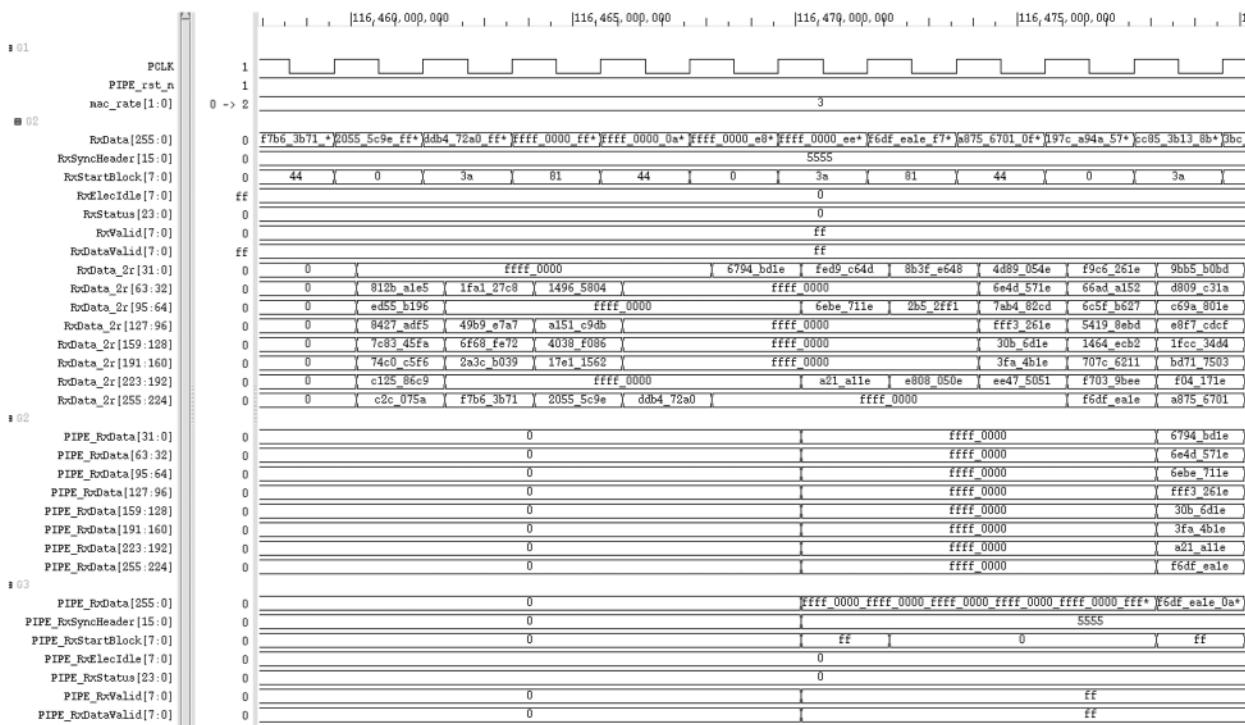

基于所搭建的验证平台，本文采用 Synopsys 公司的仿真工具以及 Novas 公司的 Verdi 工具进行了仿真联调。图 5 为对逻辑电路进行验证仿真的波形。此时的输入数据为连续 4 个 64'hffff\_0000，即为 Gen3 条件下的 EIEOS 有序集。从图 3 中可以看到，输入 8 条通道的数据中，EIEOS 有序集并未对齐，而经过该 De-skew 逻辑

图 4 FIFO 结构图

图 5 De-skew 功能仿真图

电路后最终的输出数据——8 条通道的 EIEOS 有序集完成了对齐。仿真结果验证了该 De-skew 逻辑电路功能的正确性和可行性。

表 1 所示为本文 De-skew 逻辑设计方案同现有常用方案的对比,可以看到,虽然利用计数器和多个寄存器进行数据缓存的方案也能正确实现 De-skew 功能,并对通道间 skew 是否超过最大规定值进行判断,但本文提出的方案更为简便,代码量更少,通过配置 FIFO 的位宽和深度也能适用于 Gen3/Gen4 等更高的速率情况,具有全面性、优越性和可复用性。

表 1 De-skew 逻辑电路方案对比

| 对比          | 现有常用方案                       | 本设计                              |

|-------------|------------------------------|----------------------------------|

| 基本实现方法      | 利用计数器和多个寄存器实现 <sup>[9]</sup> | 利用同步 FIFO 实现                     |

| 使用寄存器数量     | 多                            | 少                                |

| 基准通道        | 需要                           | 不需要                              |

| 能否判断最大 skew | 能                            | 能                                |

| 适用时钟频率      | 低                            | 高                                |

| 代码复用性       | 差                            | 好                                |

| 适用范围        | Gen1/Gen2                    | Gen1/Gen2/Gen3/Gen4<br>及其他多通道间纠偏 |

### 3 结论

由于 PCIe 多通道间的延迟差异,必然会导致数据传输中的 skew 现象。本文提出了一种逻辑电路,在通道数据到达接收端的先后顺序未知的情况下,实现 De-skew 功能,同时满足 PCIe 规定的最大 skew 值需求。最后搭

建测试平台并通过仿真验证了该逻辑设计方案。结果表明,本文所提出的逻辑设计有效实现了 PCIe 多通道的 De-skew 功能,同时,该逻辑电路具有普适性,能够适用于 PCIe 的各种速率、位宽、时钟频率等搭配情况,可应用于其他高速电路的多通道传输。本设计为消除通道间的 skew 问题提供了良好的借鉴意义。

### 参考文献

- [1] SOLARI E , CONGDON B .The complete PCI express reference : design implications for hardware and software developers [M]. Intel Press Inc ., 2003 .

- [2] BUDRUK R , ANDERDSON D , SHANLEY T .POE system architecture [M]. Mind Share Inc ., 2003 : 9–11 .

- [3] Li Chen , Sun Yifan , Jin Lingling , et al .Priority-based PCIe scheduling for multi-tenant multi-GPU systems [J]. IEEE Computer Architecture Letters , 2019 , 18(2) : 157–160 .

- [4] 刘勇,董乾,袁娜 .PCIExpress 物理层链路训练一致性测试状态设计 [J].计算机光盘软件与应用, 2013 , 16(9) : 114–116 .

- [5] ROHILLA G , MATHUR D , GHANEKAR U .Functional verification of MAC-PHY layer of PCI express Gen5.0 with PIPE interface using UVM [C]//2020 International Conference for Emerging Technology(INCET) , 2020 .

- [6] 王齐 .PCI Express 体系结构导读 [M]. 北京 : 机械工业出版社 , 2010 .

- [7] SHAN L , FREIDMAN D , KENNEDY C , et al .Backward compatible connectors for next generation PCIe electrical I/O [C]//

(下转第 73 页)

出版社, 2005.

- [14] HE Z, WANG C, FAN G, et al. Design of a high input impedance OPA with Bi-JFET Technology[C]//2019 IEEE 2nd International Conference on Electronics Technology (ICET), 2019: 233–236.

- [15] SHMAKOV N M. Dual precision operational amplifier with zero adjustment[C]//2001 Siberian Russian Student Workshop on Electron Devices and Materials. Proceedings 2nd Annual(IEEE Cat.No.01EX469), 2001.

(收稿日期: 2022-03-14)

(上接第 66 页)

- 2018 IEEE 68th Electronic Components and Technology Conference(ECTC), 2018.

- [8] PCI-SIG. PCI Express base specification revision 4.0[S], 2017.

- [9] KWON W, KWON H, PARK K. PCI express multi-lane De-skew logic design using embedded SERDES FPGA[C]// International Conference on Solid-State and Integrated Circuit

#### 作者简介:

何贵昆(1997-),男,硕士研究生,主要研究方向:模拟集成电路设计。

马奎(1985-),男,博士,教授,主要研究方向:半导体集成技术、模拟集成电路设计及应用、半导体芯片的可靠性。

杨发顺(1976-),通信作者,男,博士,副教授,主要研究方向:半导体功率器件与功率集成技术、半导体集成电路设计,E-mail:fashun@126.com。

扫码下载电子文档

Technology. ICSICT, 2004.

(收稿日期: 2022-03-21)

#### 作者简介:

王可扬(1996-),男,硕士,主要研究方向:数字集成电路设计。

吉兵(1988-),男,硕士,主要研究方向:数字集成电路设计。

屈凌翔(1981-),男,硕士,高级工程师,主要研究方向:数字集成电路设计。

扫码下载电子文档

## “健康医疗微电子”专栏征稿

以集成电路为代表的微电子技术不断改变着世界的面貌,如今其应用正在从“计算机、通信、信息处理”等传统IT领域向“健康医疗、能源、环保”等多学科交叉融合的崭新领域拓展。微纳电子技术与生命科学的融合,形成了形式多样、功能强大的创新性的工具和方法,助力生命科学、健康医疗的研究及应用。为了及时、集中地反应我国健康医疗领域微电子技术的最新发展及应用成果,《电子技术应用》拟在2023年第1期出版“健康医疗微电子”专栏,主要刊登反应微纳电子技术在健康医疗领域中具有创新性的科研成果和应用技术进展的论文、简报、综述和消息。欢迎相关领域的专家学者、科研人员踊跃投稿!

### 1. 专栏特约主编

中国科学院微电子研究所/中国科学院大学 黄成军 研究员/教授

华中科技大学光学与电子信息学院/武汉光电国家研究中心 刘欢 教授

北京信息科技大学仪器科学与光电子工程学院 朱疆 教授

### 2. 征稿范围

征文涉及的领域包括但不限于:

(1)应用于生命健康的新型传感材料、器件与系统;((2)生物-微电子机械技术(Bio-MEMS),生物传感器;(3)柔性电子技术,可穿戴及植入式微纳传感器,芯片技术及微系统;(4)先进脑机接口器件、芯片及微系统;(5)微流控技术与芯片实验室系统,光流控技术;(6)用于新冠病毒快速检测的新型生物传感技术;(7)量子点材料生物医学应用;(8)面向疾病早筛的人体呼出气传感器;(9)健康医疗成像技术及图像处理。

3. 稿件要求:文章需具有创新性且未在其他期刊公开发表过。文中图表需清晰,文字规范。详见《电子技术应用》投稿须知(<http://www.chinaaet.com/paper/notice/>)。

4. 截稿日期:2022年11月30日。

5. 投稿方式:请登录《电子技术应用》官网(<http://www.ChinaAET.com/>),投稿页面中选择“健康医疗微电子”专栏投稿,按要求提交。

专栏编辑:毕晓东 (010-82306085; bixd@chinaaet.com)

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所