# 一种高线性度的 2.4 GHz CMOS 功率放大器设计

王家文<sup>1,2</sup>,潘文光<sup>1,2</sup>

(1.中国科学院大学 微电子学院,北京 100049;2.南京中科微电子有限公司,江苏 南京 210018)

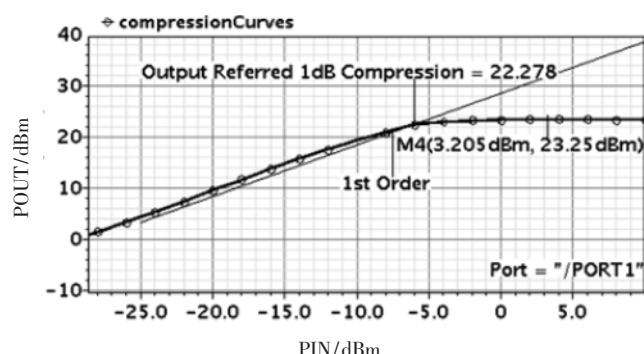

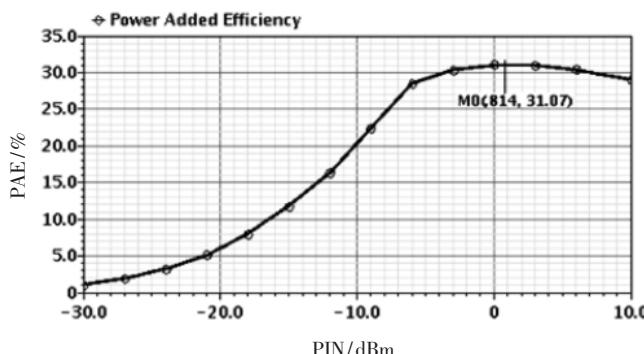

**摘要:**为了满足目前物联网低成本、低功耗与较高线性度的市场应用需求,提出了一种高线性度的 2.4 GHz 功率放大器(PA)。该功率放大器为两级结构,为了提高增益的同时保持较低的静态功耗其驱动级采用了电流复用两级共源放大结构,并且使用了两级失真抵消的方法减小了晶体管跨导非线性的影响,同时采用二极管线性化偏置来补偿寄生电容非线性导致的增益压缩现象。该功率放大器采用 0.18 μm CMOS 工艺,后仿真结果表明,在 2.4 GHz 工作频率下,该 PA 小信号增益为 30 dB,输出 1 dB 压缩点为 22 dBm,静态功耗为 53 mW,功率附加效率峰值为 31%。

**关键词:**功率放大器;电流复用;失真抵消;二极管线性化偏置

中图分类号: TN722

文献标识码: A

DOI:10.16157/j.issn.0258-7998.212409

中文引用格式: 王家文,潘文光. 一种高线性度的 2.4 GHz CMOS 功率放大器设计[J]. 电子技术应用,2022,48(12):65-69.

英文引用格式: Wang Jiawen, Pan Wenguang. Design of a 2.4 GHz CMOS power amplifier with high linearity[J]. Application of Electronic Technique, 2022, 48(12):65-69.

## Design of a 2.4 GHz CMOS power amplifier with high linearity

Wang Jiawen<sup>1,2</sup>,Pan Wenguang<sup>1,2</sup>

(1.School of Microelectronics, University of Chinese Academy of Sciences, Beijing 100049, China;

2.Nanjing Zhongke Microelectronics Co., Ltd., Nanjing 210018, China)

**Abstract:** In order to meet the market demand of low-cost, low-power consumption and high linearity of the Internet of Things, a 2.4 GHz power amplifier(PA) with high linearity is proposed. The power amplifier has a two-stage structure. In order to improve the gain while maintaining low static power consumption, the driver stage of the PA adopts a current multiplexing two-stage common source amplifier structure, uses a two-stage distortion cancellation method to reduce transconductance nonlinearity, and adopts diode linearization bias to compensate gain compression phenomenon caused by parasitic capacitance nonlinearity. The PA uses a 0.18 μm CMOS process. Simulation results show that at 2.4 GHz operating frequency, the PA has a small signal gain of 30 dB, an output 1 dB compression point of 21.7 dBm, a static power consumption of 53 mW, and a power-added efficiency peak of 31%.

**Key words:** power amplifier; current multiplexing; distortion cancellation; diode linearization bias

## 0 引言

作为信息技术产业第三次革命的物联网技术高速发展,对应用于物联网的无线收发机也提出了低成本、低功耗与高集成度的新需求<sup>[1-2]</sup>,作为无线收发机中核心模块的 CMOS 功率放大器(PA)也得到了广泛的关注与研究。降低功耗的主流方法为栅极偏置技术,通过调整不同的偏置来达到降低功耗的目的,但通过调整偏置电压降低功耗会恶化 PA 线性度,电流复用技术凭借其可以在保证较高增益的同时降低功耗的优点也在射频 CMOS 电路设计中得到了广泛应用<sup>[3-6]</sup>。随着现代通信调制方式的复杂化程度越来越高,对 PA 的线性度要求也在不断地提高,这就常会要求 PA 工作在功率回退状态下,但这是通过降低效率来提高线性度。针对 CMOS PA 同样有很多线性化方法被提出,主要有最佳偏置技术、预失真技术、多栅晶体管技术、电容补偿技术等,这些线

性化方法通常会被结合起来使 PA 线性度达到满意的水平<sup>[7-12]</sup>。

为了达到低功耗高线性度的要求,本文基于 0.18 μm CMOS 工艺设计了一种两级线性功率放大器,其中驱动级使用电流复用结构提供较高增益的同时保持较低的静态功耗,同时使用了两级失真抵消与二极管线性化技术改善 PA 线性度。该 PA 为射频前端芯片的一部分,整体射频前端芯片主要包括 PA、低噪声放大器(LNA)与射频开关,目前整体射频前端芯片已完成版图设计与后仿真验证并递交制造厂进行流片。

## 1 原理分析与设计

### 1.1 电流复用的驱动级电路设计

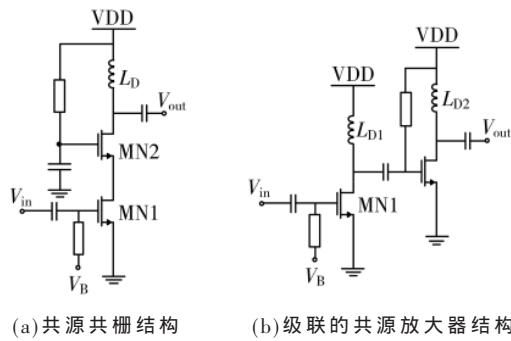

驱动级主要是为了提供一个大的增益以实现对功率级的驱动,经典的共源共栅电路结构如图 1(a)所示,由共源管与共栅管级联组成共源共栅结构,共源共栅电

路结构被广泛应用于模拟射频放大器中,这种结构可以提高输出阻抗与增益、增强输出与输入之间的隔离度,并且能够减小 Miller 电容的影响。为了进一步提高增益,经常会使用多级级联的共源放大器结构,如图 1(b)所示的两级级联共源放大电路将交流信号放大两次,虽然其增益显著增大,但是其存在两路静态电流功耗,静态功耗比共源共栅电路大很多。

图 1 经典的驱动级结构

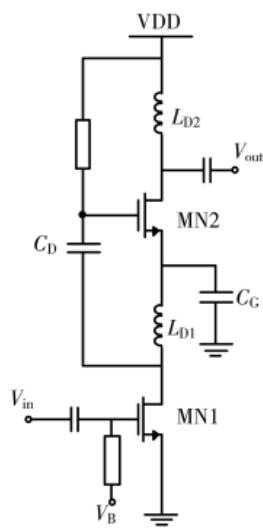

为了获得较高的增益并且不增加额外的静态功耗,将一路直流复用,结合上述两种电路的优点提出电流复用两级级联放大电路。此电流复用电路核心在于级间网络设计,如图 2 所示, $C_D$ 、 $L_{D1}$  与  $C_G$  组成了级间网络, $L_{D1}$  作为扼流电感起到阻塞射频信号的功能, $C_D$  对射频信号为低阻通路将 MN1 放大后的射频信号传送到 MN2 输入端, $C_G$  为旁路电容。采用电流复用结构在不增加额外功耗的情况下,达到了两级放大的效果。

## 1.2 两级失真抵消分析

放大器电路的非线性主要来自于有源器件的非线性。跨导  $g_m$  非线性是 CMOS 晶体管非线性的主要来源,寄生电容的非线性也会导致增益压缩的发生,而衬底泄露网络的非线性很小<sup>[13-15]</sup>。

因为其谐波失真中二次谐波与三次谐波失真起到决定性作用,因此交流信号漏电电流  $I_{ds}$  可近似为:

$$I_{ds}(V_{gs}) = g_{m1} V_{gs} + g_{m2} V_{gs}^2 + g_{m3} V_{gs}^3 \quad (1)$$

跨导  $g_m$  可表示为:

$$g_m = g_{m1} + g_{m2} V_{gs} + g_{m3} V_{gs}^2 \quad (2)$$

此时在输入端加入两个频率相近的等幅值信号  $V_{gs}(t) = A(\cos\omega_1 t + \cos\omega_2 t)$ , 通过三角函数的积化和差公式与倍角公式转化, 并且只保留基频信号和与基频信号很接

近难以滤除的三阶交调分量后得到  $I_{ds}$  为:

$$\begin{aligned} I_{ds}(t) &= (g_{m1}A + \frac{9}{4}g_{m3}A^3)(\cos\omega_1 t + \cos\omega_2 t) + \\ &\quad \frac{3}{4}g_{m3}A^3[\cos(2\omega_1 - \omega_2)t + \cos(2\omega_2 - \omega_1)t] \end{aligned} \quad (3)$$

由式(3)可以看出三阶跨导  $g_{m3}$  对功率放大器三阶非线性干扰有很大的影响, 并且当  $g_{m3}$  为负数时还会降低增益, 致使出现幅值  $A$  不断增大, 增益不断减小的现象。

跨导被定义为:

$$g_m = \frac{\partial I_{ds}}{\partial V_{gs}} \quad (4)$$

由式(2)可知忽略二次以上谐波时二阶跨导和忽略三次以上谐波时三阶跨导的定义为:

$$\left\{ \begin{array}{l} g_{m2} = \frac{1}{2} \frac{\partial^2 I_{ds}}{\partial^2 V_{gs}} \\ g_{m3} = \frac{1}{6} \frac{\partial^3 I_{ds}}{\partial^3 V_{gs}} \end{array} \right. \quad (5)$$

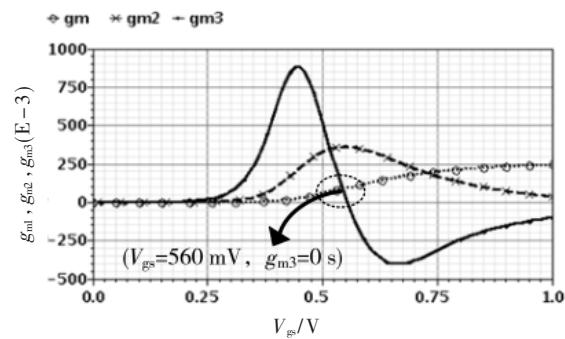

由二阶跨导、三阶跨导的定义可以仿真得到  $g_{m1}$ 、 $g_{m2}$ 、 $g_{m3}$  随  $V_{gs}$  变化的图像, 图 3 所示为 NMOS 管 ( $L=180$  nm,  $W=8$   $\mu$ m, Finger=30, Multiplier=2) 的  $g_{m1}$ 、 $g_{m2}$ 、 $g_{m3}$  随  $V_{gs}$  变化的曲线图,  $g_{m3}$  曲线呈现先正后负趋势, 并存在一个过零点; 很容易想到将偏置电压偏置于  $g_{m3}=0$  的电压处就是最佳偏置电压, 但是最佳偏置电压对工艺敏感, 且输入电压摆幅过大时最佳偏置电压失效<sup>[16]</sup>。

图 2 电流复用两级级联放大电路

图 3  $g_{m1}$ 、 $g_{m2}$ 、 $g_{m3}$  随  $v_{gs}$  变化的曲线图

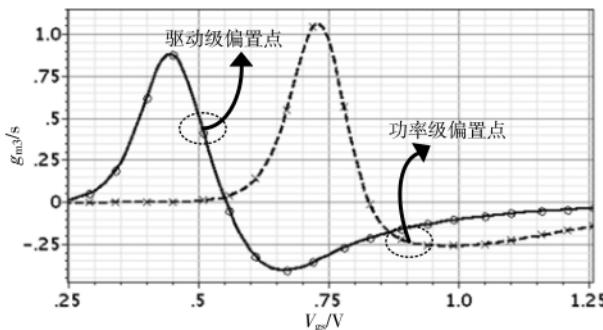

因为设计的功率放大器为两级功率放大器,且驱动级输入管采为薄栅晶体管提高增益,功率级输入管为厚栅晶体管,考虑能否通过调整两级偏置使得两级的三阶交调失真(IMD3)相互抵消从而改善 IMD3。图 4 所示为驱动级薄栅晶体管三阶跨导  $g_{m3\_drive}$  与功率级厚栅晶体管三阶跨导  $g_{m3\_power}$  曲线, 调整两级的偏置使得两级的  $g_{m3}$  符号相反就可以实现三阶交调失真相互抵消。使驱动级产生的三阶交调失真电流  $i_{3rd\_drive}(t)$  与功率级产生的三阶交调失真电流  $i_{3rd\_power}(t)$  抵消则有:

$$i_{3rd\_drive}(t) + i_{3rd\_power}(t) = 0 \quad (6)$$

与式(3)计算方法相同最终可解得:

$$|g_{m3\_power}| = \frac{-g_{m3\_drive}}{2} |g_{m3\_drive}| \alpha_{drive} \quad (7)$$

图 4 驱动级与功率级  $g_{m3}$  曲线

当  $g_{m3\_drive}$  与  $g_{m3\_power}$  符号相反且满足式(7)时三阶交调失真电流抵消, 实际设计中应多次调整两级的偏置电压, 不断迭代得到最优的线性度。本设计中经过不断迭代仿真验证将驱动级偏置于 518 mV, 功率级偏置于 900 mV, 均工作在 AB 类模式下, 兼顾了线性度与效率。

### 1.3 二极管线性化偏置电路分析

MOS 晶体管的寄生电容在栅端的等效电容  $C_{gg}$  的存在会导致输入信号的部分功率泄露到地, 且  $C_{gg}$  越大输入信号功率泄露越多使得功率增益下降, 由于  $C_{gg}$  容值会随  $V_{gs}$  电压的增加而增加, 因此当输入功率不断增加时  $C_{gg}$  增加, 功率增益会进一步下降, 也就是说  $C_{gg}$  的非线性会加重增益压缩现象。

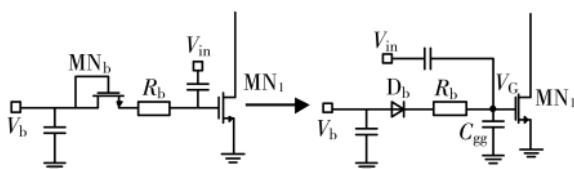

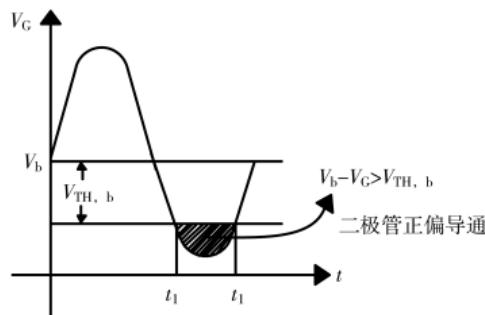

为了补偿寄生电容非线性导致的增益压缩现象, 提出了二极管线性化偏置电路, 图 5 所示为二极管线性化偏置电路及其等效电路, 二极管形式的晶体管  $MN_b$  可以简单地等效为一个二极管  $D_b$ , 晶体管  $MN_b$  的阈值电压为  $V_{TH,b}$ ; 输入晶体管  $MN_1$  的栅端等效电容为  $C_{gg}$ , 栅端电压为  $V_G = V_b + V_{in}$ ; 在输入信号功率较小时  $V_b - V_G$  始终小于  $V_{TH,b}$ , 二极管  $D_b$  一直处于反偏状态; 输入信号功率不断增大, 输入信号摆幅增大, 如图 6 所示, 当信号下摆负压

图 5 二极管线性化偏置电路及其等效电路

图 6 输入信号功率大时栅端电压  $V_G$  波形

很大时  $V_b - V_G$  会在  $t_1 \sim t_2$  时间段里大于  $V_{TH,b}$ , 此时二极管  $D_b$  正偏导通, 其导通电流会给  $C_{gg}$  充电抬高  $V_G$  的直流电平。

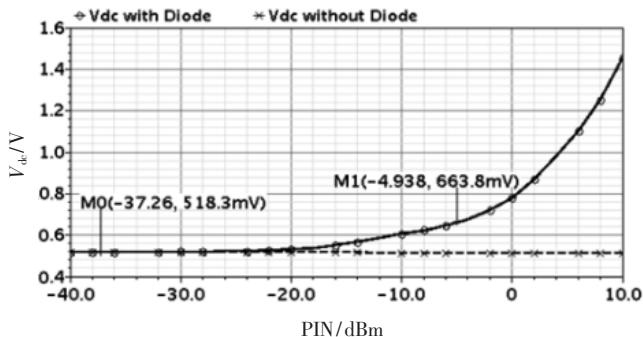

图 7 为仿真得到的输入管栅极直流电压随输入信号功率 PIN 的变化曲线, 可以明显看出没有使用二极管偏置的栅极直流电压为一恒定值, 而使用了二极管偏置后栅极直流电压会随着输入信号功率的增加而升高。

图 7 有无二极管偏置时直流电压  $V_d$  随 PIN 变化对比图

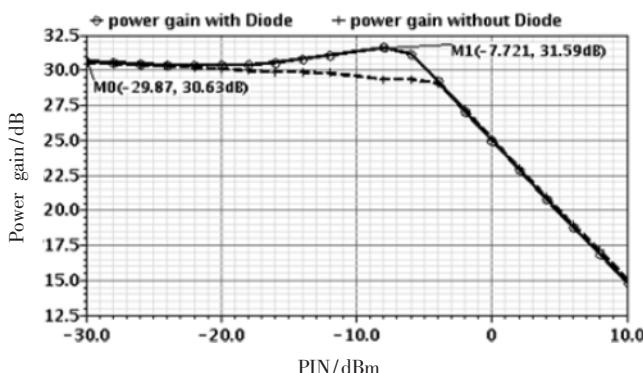

偏置电压的升高可以提高增益, 因此二极管线性化偏置电路可以补偿寄生电容非线性导致的增益压缩现象, 如图 8 所示的功率增益随输入信号功率变化曲线, 可以明显看出二极管线性化偏置电路使得增益压缩现象得到了极大的改善。

图 8 有无二极管偏置时功率增益随 PIN 变化对比图

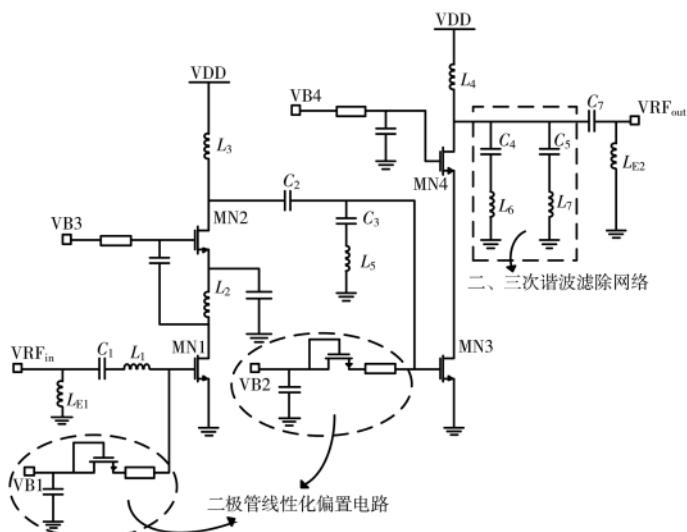

### 1.4 整体电路结构

本文 PA 电路结构如图 9 所示, 其中驱动级采用了电流复用结构, 提高增益的同时保持了较低的功耗, 功率级采用共源共栅结构, 驱动级与功率级偏置均采用二极管线性化偏置补偿寄生电容非线性, 并且调节两级偏置电压以达到两级失真抵消效果; 输入输出匹配网络均采用 L 型阻抗变化网络, 其中电容电感  $C_4, L_6, C_5$  与  $L_7$  在输出端构成二、三次谐波滤除网络, 消减了二阶与三阶谐波失真, 提升了 PA 的线性度; 由于二次谐波与基频信号混频会产生与基频很接近的三阶互调失真, 因此在功率级输入端加入  $C_3, L_5$  构成的二次谐波短路网络来消

图 9 本文 PA 电路结构图

减二次谐波影响，减小三阶互调失真。

## 2 后仿真结果与版图设计

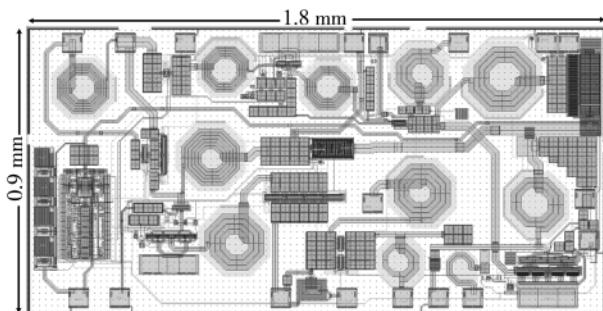

本文设计的功率放大器为射频前端芯片一部分，整个射频前端芯片采用 180 nm CMOS 工艺完成电路设计与版图布局，其整体版图布局如图 10 所示，整体芯片面积为 0.9 mm×1.8 mm。

图 10 整体版图设计

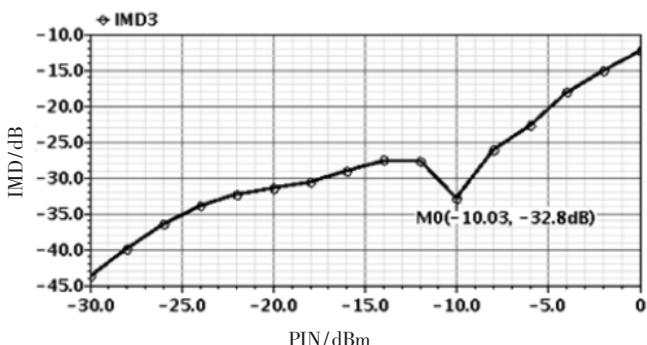

三阶交调失真(IMD3)反映了相邻信道的干扰程度，因此 IMD3 可以用来衡量功率放大器线性度，图 11 为 IMD3 仿真结果，结果显示在输入功率为 -10 dBm 时，三阶交调失真量为 -30 dB，具有较高的线性度。

图 11 三阶交调失真(IMD3)仿真

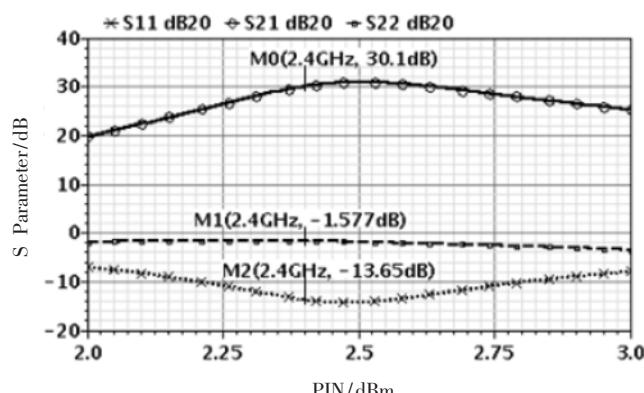

图 12 是 S 参数仿真曲线，仿真结果显示，小信号增益 S21 为 30 dB，增益较高；S11 为 -13.5 dB 小于 -10 dB，输入匹配较好；S22 为 -1.5 dB，由于输出采用负载线匹配，S22 参数小于 0 即可。

图 12 S 参数仿真

输出 1 dB 压缩点可以体现 PA 线性度，图 13 为谐波平衡仿真得到输出功率曲线，结果显示饱和输出功率为 23.2 dBm，输出 1 dB 压缩点 22 dBm。

图 13 输出 1 dB 压缩点仿真

DC 仿真得到在电源电压 3.3 V 下整个 PA 静态电流为 16 mA，静态功耗为 53 mW，图 14 为功率附加效率(PAE)仿真曲线，结果显示 PAE 峰值为 31%，其静态功耗较低且 PAE 较高。

图 14 功率附加效率(PAE)仿真

### 3 结论

本文设计了一种高线性度的 2.4 GHz 功率放大器,采用 0.18  $\mu\text{m}$  CMOS 工艺完成电路搭建与版图设计,电路版图面积为 0.9 mm×1.8 mm,后仿真结果显示在工作电压为 3.3 V 下其小信号增益为 30 dB,输出 1 dB 压缩点为 22 dBm,静态功耗为 53 mW,PAE 峰值为 31%,具备较低的功耗与较高的线性度,满足物联网中 2.4 GHz PA 应用的需求。

### 参考文献

- [1] 吕士羽.物联网技术研究综述[J].产业技术创新,2019,26(1):36–37.

- [2] 射频前端发展状况[J].半导体信息,2019(4):24–27.

- [3] Zhao Mingfu, Sun Lingling, Wen Jincai, et al. A 2.45 GHz CMOS power amplifier with high linearity[C]//ASICON'09. IEEE 8th International Conference, 2009: 383–386.

- [4] WEI X, NIU G, LI Y, et al. Modeling and characterization of intermodulation linearity on a 90-nm RF CMOS technology[J]. IEEE Transactions on Microwave Theory and Techniques, 2009, 57(4): 965–971.

- [5] TERAJIMA K, FUJII K, SONODA T, et al. A 2.0 GHz CMOS triple cascode push-pull power amplifier with second harmonic injection for linearity enhancement[C]//2014 9th European Microwave Integrated Circuit Conference, 2014: 321–324.

- [6] KANG S, BAEK D, HONG S, et al. A 5-GHz WLAN RF CMOS power amplifier with a parallel-cascoded configuration and an active feedback linearizer[J]. IEEE Transactions on Microwave Theory and Techniques, 2017, 65(9): 3230–3244.

- [7] 刘斌, 刘祖华, 黄亮, 等. 2.45 GHz 0.18  $\mu\text{m}$  CMOS 高线性功率放大器设计[J]. 电子技术应用, 2014, 40(2): 46–48.

- [8] LIN C, YANG J A. 1.8/2.6 GHz CMOS high linearity power amplifier for LTE application[C]//2016 IEEE International Meeting for Future of Electron Devices, Kansai(IMFEDK), 2016.

- [9] KHAN M A, NEGRA R. Common-drain CMOS power amplifier; an alternative power amplifier[C]//2017 12th European Microwave Integrated Circuits Conference(EuMIC), Nuremberg, Germany, 2017.

- [10] 林俊明, 郑耀华, 张志浩, 等. CMOS 射频功率放大器高效率和高线性度研究进展[J]. 电子技术应用, 2015, 41(11): 17–23.

- [11] JIN Y, HONG S. A 2.4-GHz CMOS common-gate combining power amplifier with load impedance adaptor[J]. IEEE Microwave and Wireless Components Letters, 2017, 27(9): 836–838.

- [12] ZHAI C, CHENG K K M. Linearity-enhanced dual-power-mode CMOS RF power amplifier design using post-distortion[C]//2019 IEEE Asia-Pacific Microwave Conference (APMC), 2019.

- [13] DE CARVALHO N B, PEDRO J C. Large- and small-signal IMD behavior of microwave power amplifiers[J]. IEEE Transactions on Microwave Theory and Techniques, 1999, 47(12): 2364–2374.

- [14] FAGER C, PEDRO J C, DE CARVALHO N B, et al. Prediction of IMD in LDMOS transistor amplifiers using a new large-signal model[J]. IEEE Transactions on Microwave Theory and Techniques, 2002, 50(12): 2834–2842.

- [15] KANG S, CHOI B, KIM B. Linearity analysis of CMOS for RF application[J]. IEEE Transactions on Microwave Theory and Techniques, 2003, 51(3): 972–977.

- [16] 任志雄. 片上功率合成器的建模及其在 CMOS 射频放大器中的应用研究[D]. 武汉: 华中科技大学, 2015.

(收稿日期: 2021-11-30)

### 作者简介:

王家文(1998-),男,硕士研究生,主要研究方向:射频集成电路设计。

潘文光(1983-),通信作者,男,博士,副研究员,主要研究方向:模拟集成电路设计,E-mail:panwenguang@csmic.ac.cn。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所