# 一种用于核与粒子物理实验数字化的多重数触发判选电路设计\*

刘尚铭<sup>1,2</sup>,曹平<sup>1,2</sup>,李超<sup>1,2</sup>,汪晓虎<sup>1,2</sup>

(1.中国科学技术大学核探测与核电子学国家重点实验室,安徽合肥230026;

2.中国科学技术大学近代物理系,安徽合肥230026)

**摘要:**核与粒子物理实验中,因实验本底与探测器噪声影响,实验需要通过触发判选机制筛选出有效物理事例,剔除掉本底噪声。针对物理实验高事例率情况下基于击中多重数(Hit multiplicity, NHit)的触发判选需求,设计了一种高性能数字触发判选电路。该电路具有13路高速串行通信接口,支持光纤数据传输与千兆网络通信;板载32 Gb DDR4缓存与高性能FPGA,以支持大容量高速存储与实时数据处理。基于该电路可运行实时的硬件NHit触发算法,从而实现对前端数据的快速触发判选与数据读出,同时该电路便于扩展,可灵活地用在不同的物理实验上。经过测试验证,数字触发判选电路单路光纤接口传输速率可达8.125 Gb/s,上行网络传输速率达949.3 Mb/s,DDR4缓存实际读写速率可达102.6 Gb/s,满足数字触发判选电路设计的数据传输与缓存需求。

**关键词:**触发判选;数据读出;光纤;SiTCP;DDR

中图分类号: TL822+3

文献标志码: A

DOI: 10.16157/j.issn.0258-7998.222927

中文引用格式:刘尚铭,曹平,李超,等.一种用于核与粒子物理实验数字化的多重数触发判选电路设计[J].电子技术应用,2023,49(1):124-129.

英文引用格式:Liu Shangming, Cao Ping, Li Chao, et al. Design of a digital NHit trigger circuit for nuclear and particle physics experiment[J]. Application of Electronic Technique, 2023, 49(1): 124-129.

## Design of a digital NHit trigger circuit for nuclear and particle physics experiment

Liu Shangming<sup>1,2</sup>, Cao Ping<sup>1,2</sup>, Li Chao<sup>1,2</sup>, Wang Xiaohu<sup>1,2</sup>

(1.State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei 230026, China;

2. Department of Modern Physics, University of Science and Technology of China, Hefei 230026, China)

**Abstract:** In nuclear and particle physics experiments, due to the influence of the experimental background and detector noise, the experiment needs to pick out valid physical events by the trigger selection, and eliminate the background noise. Aiming at the trigger selection requirements based on hit multiplicity (NHit) in the cases of high event rates in physical experiments, this paper designs a high-performance digital trigger circuit. This circuit has 13 high-speed serial communication interfaces, which support optical fiber data transmission and Gigabit network communication; onboard 32 Gbit DDR4 cache and high-end FPGA to support large-capacity high-speed storage and real-time data processing. Based on this circuit, the real-time hardware NHit trigger algorithm could be run, which could realize fast trigger selection and data readout for the front-end data. At the same time, the circuit is easy to expand and could be flexibly used in different physical experiments. After testing and verification, the transmission rate of one single optical fiber interface could reach 8.125 Gb/s, the uplink transmission rate of SiTCP could reach 949.3 Mb/s, and the actual read and write rates of the DDR4 cache could reach 102.6 Gb/s, which meet the data transmission and caching requirements of digital trigger circuit design.

**Key words:** trigger selection; data readout; optical fiber; SiTCP; DDR

## 0 引言

核与粒子物理主要研究原子核内部及以下层次的

微观结构,为研究粒子间相互作用,人们通过数量庞大的探测器阵列和电子学设备对实验物理现象进行观测<sup>[1-2]</sup>。物理实验采用触发判选机制来滤除实验本底与探测器噪声,通过触发系统的设计从前端原始信息中筛

\* 基金项目:核探测与核电子学国家重点实验室项目(SKLPDE-ZZ-202105,

SKLPDE-ZZ-202206)

选出有效物理事例，从而降低后端数据传输与缓存压力。

核与粒子物理实验中的触发判选技术主要有模拟硬件触发、无硬件触发、数字硬件触发三种方式。早期实验的触发系统因技术限制，通常使用模拟硬件触发方式提取前端信号特征参量并进行触发判选，如中国原子能院GTAF谱仪<sup>[3]</sup>，这些触发系统大多专用且固定，具有一定死时间，无法适应物理实验高事例率的发展需要。随着数据传输处理能力的快速提高，压缩重物质实验<sup>[4]</sup>、反质子湮灭实验<sup>[5]</sup>、大型高海拔宇宙线观测站<sup>[6]</sup>等实验开始采用无硬件触发的数据读出方法，将前端所有数据传输至后端，由后端高性能计算单元进行触发判选，但对所有数据不加区分的读出给读出系统与数据获取系统带来了更大的设计压力与资源消耗。近年来在某些实验上，如反角白光中子源GTAF-II谱仪<sup>[7]</sup>、江门中微子实验<sup>[8]</sup>，逐渐开展了基于FPGA实时硬件的全数字化硬件触发技术研究，充分利用FPGA并行处理能力强和实时性高的优点，对原始数据进行实时的触发判选与数据筛选。

物理实验中的触发判选一般根据有效物理事例与本底噪声的特点，设置相应的判选条件。击中多重数(Hit multiplicity, NHit)是一种常用的判选依据，在反角白光中子源GTAF-II谱仪、大型高海拔宇宙线观测站、江门中微子实验、暗物质探测<sup>[9]</sup>等实验中被广泛应用。触发系统需要接收汇聚前端所有原始数据，并从中快速统计NHit信息，从而完成全局触发判选。在高事例率情况下，基于数字硬件方式的NHit触发相比于无硬件触发方式具有更好实时性，同时可以有效降低实验成本资源开销，而数字硬件触发方式需要依托具体硬件电路的实现，才能完成实际的触发判选。

针对核与粒子物理实验中的数字NHit触发处理需求，本文设计了一种高性能数字触发判选电路。该电路支持多个通道的光纤数据传输与千兆网络通信，使用大容量高速DDR4缓存与高性能FPGA支持高速数据缓存与实时硬件数字触发处理。该电路灵活可扩展，可应用在不同的物理实验场景中，通过多块该电路组合可实现灵活的触发处理；同时具有一定兼容性，可作为机箱标准插卡并入某些物理实验电子学系统。通过对数字触发硬件电路的数据传输与缓存接口的测试，结果表明数字硬件电路可以实现与多个硬件间的光纤数据传输，以及与上位机间的千兆网络通信，同时支持高带宽的DDR4数据缓存，满足电路设计需求。

## 1 数字触发方案

在核与粒子物理实验中，基于光纤的数据传输是一种高效的远距离数据传输方式，被广泛应用在各个物理实验中。数字触发判选电路可通过光纤与前端电子学

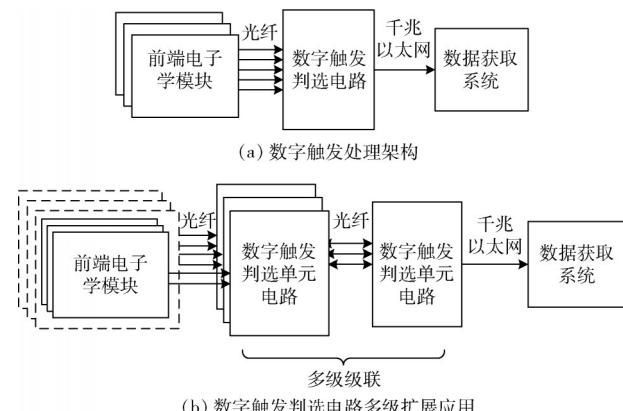

硬件相连，通过多个光纤链路汇聚前端原始数据，同时在内部通过高速大容量缓存将其缓存在本地等待后续触发处理；在硬件上使用高性能FPGA运行实时的NHit触发算法，通过分析原始数据的时间信息得到NHit统计结果并进行全局触发判选；在得到触发结果后，数字触发判选电路挑选读出本地缓存中的有效物理事例数据，并通过千兆网络发送给后级数据获取系统，其触发处理架构如图1(a)所示。

由于物理实验通道数众多，在某些多通道高事例率的物理实验中，单块数字触发判选电路难以实现对所有前端数据的汇聚、读出以及触发处理。该情况下可根据物理实验的前端通道数、原始事例率、有效事例数据率等具体情况，使用多块数字触发判选单元电路进行级联扩展，从而实现灵活的触发处理操作，图1(b)展示了多块数字触发判选电路扩展的应用方式。

图1 数字触发判选电路

数字触发判选电路具备多通道光纤数据传输与千兆网络通信、大容量高带宽数据缓存、实时数据处理与触发判选能力，该电路实现不依赖具体的机箱平台，出于兼容性考虑，将数字触发判选电路设计成标准的MTCA机箱插卡<sup>[10]</sup>，实际使用时可作为单独的电子学模块独立运行，也可兼容某些物理实验的电子学系统，可插到MTCA机箱内实现与其他插卡的数据交互，从而大大增强数字触发判选电路的灵活性与可扩展性。此外，本方法也不完全依赖于光纤技术，当前端原始数据率不高情况下，也可利用电缆技术进行数据的传输收集。

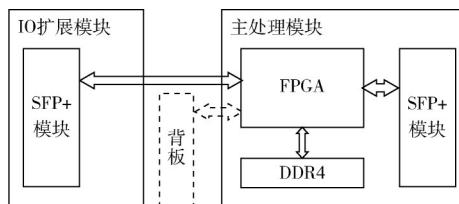

由于光纤数据传输需使用较多数量的SFP+模块，因用户插卡面板空间限制，数字触发判选电路实际上由一个负责数据传输与处理的主处理模块与一个IO扩展模块组成，其电路结构框图如图2所示。在主处理模块上使用1颗高性能FPGA芯片负责数据传输与实时处理，多颗DDR4芯片用作大容量高速数据缓存，同时主处理模块与IO扩展模块上布有多个SFP+模块用于多个通道的光纤数据传输与千兆网络通信，数字触发判选电路实

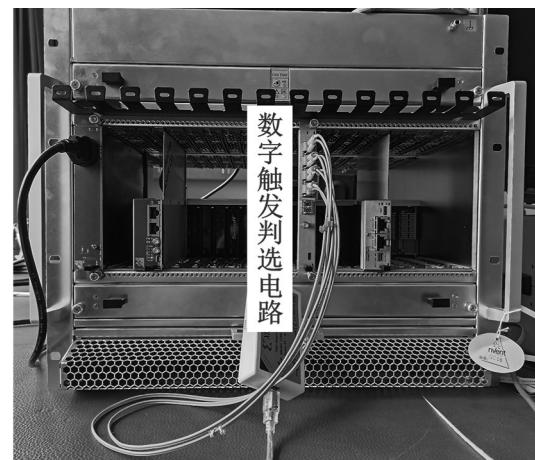

物如图3所示。

图2 数字触发判选电路框图

图3 数字触发判选电路实物图

数字触发判选电路基于光纤来进行高速串行数据通信,使用SFP+光模块进行光电转换,并将电信号连接到FPGA的高速串行收发器上,通过FPGA逻辑配置可以使各个高速串行收发器工作在不同的高速串行数据通信协议下,例如Aurora、SRIO、PCIe等协议<sup>[11-13]</sup>。

在千兆网络通信上数字触发判选电路使用SiTCP技术<sup>[14]</sup>,SiTCP是为高能物理实验而开发的一种网络通信技术,搭建了一种可在FPGA芯片上运行的硬件网络通信处理单元,具有低资源消耗、低功耗等优势。从网络协议层级上来看,SiTCP用硬件实现了MAC层及以上层级,可将FPGA的高速串行收发器用作网络通信的PHY层,数字触发判选电路将以太网SFP模块插到该路的SFP+通道上,即可将该路SFP+通道用于千兆网络数据传输。

## 2 数字触发判选电路设计

### 2.1 主处理模块

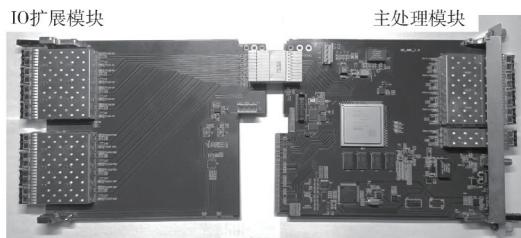

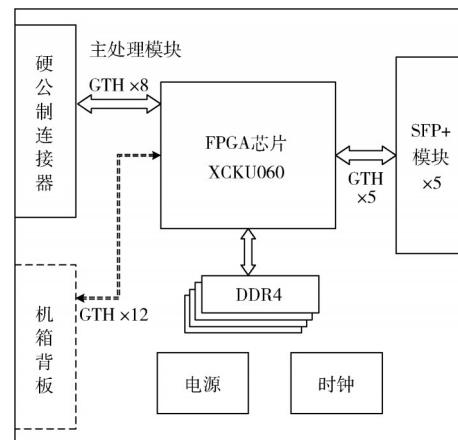

主处理模块的具体电路结构框图如图4所示,可以看到主处理模块主要由FPGA、DDR4、时钟、电源、SFP+接口电路、背板接口电路几部分组成。

#### 2.1.1 FPGA与DDR4芯片

为了支持高速数据传输与缓存,主处理模块上使用一颗Xilinx Kintex UltraScale系列XCKU060型号的FPGA芯片,该芯片具有28个可达16Gb/s传输速率的高速串行收发器(GTH),支持最高传输速率达2400Mb/s的DDR4缓存芯片连接。DDR4芯片使用Micron公司的MT40A512M16LY-083产品,单个芯片数据总线位宽为16bit,该内存颗粒的存储容量为8Gb,最大时钟频率为1.6GHz。在本数字触发判选电路中,为了实现高速数据缓存,使用4片DDR4芯片合并了数据总线位

图4 主处理模块电路结构框图

宽,将数据传输总线宽度扩展为64位,数据缓存速率理论最高可达153.6Gb/s。

#### 2.1.2 时钟方案

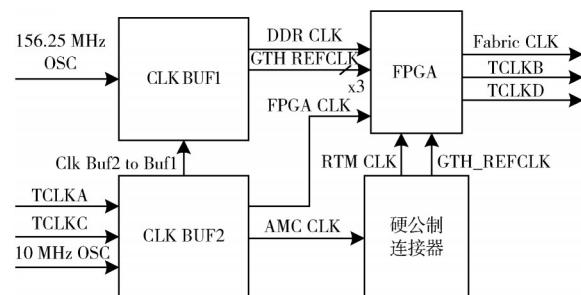

主处理模块的时钟方案如图5所示,使用了两颗时钟扇出芯片,CLK BUF1选择接收本地晶振的156.25MHz时钟,或者是CLK BUF2扇出的时钟信号,同时将输入时钟扇出多路,输出时钟作为FPGA多个GT bank以及DDR接口的参考时钟。CLK BUF2接收本地的高品质10MHz时钟信号,以及背板送过来的TCLKA与TCLKC时钟,选通其中一路并扇出给FPGA、IO扩展模块以及CLK BUF1。同时FPGA芯片接收IO扩展模块通过硬公制连接器送过来的时钟,并输出两路时钟信号作为TCLKB与TCLKD时钟送给机箱背板。通过以上的时钟电路设计可以实现灵活的时钟分配方案。

图5 主处理模块的时钟方案

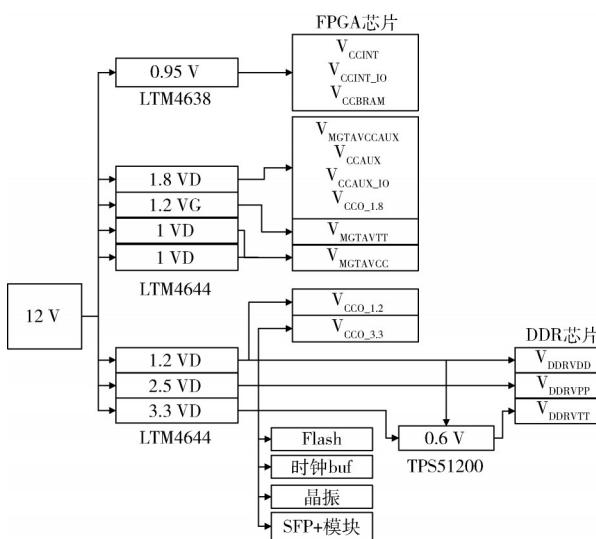

#### 2.1.3 电源方案

主处理模块的电源方案如图6所示,可通过外部直流电源或是机箱背板输入的12V电源进行供电,主处理模块使用ADI公司的具有较高转换效率、高集成度的DC-DC直流降压芯片,1片单通道LTM4638芯片将12V转为0.95V,供给FPGA的核心电压工作;2片4通道输出的LTM4644芯片将12V电平转换为不同的工作电压,并分别给板上FPGA、DDR4、Flash等芯片供电。同时使用TPS51200终端稳压器芯片为DDR4提供特定工

作电平。

图 6 主处理模块的电源方案

#### 2.1.4 SFP+接口电路

数字触发判选电路使用 SFP+ 模块来实现光纤链路数据传输与网络通信，在主处理模块上载有 5 路 SFP+ 连接器插座与对应的屏蔽罩，将不同功能以及传输速率的商用 SFP+ 光纤收发器安装到板卡上，即可实现不同功能与速率的高速串行数据通信。光纤链路的高速串行数据传输使用最高传输速率为 8.5 Gb/s 的 FTLF8528P3 BCV 光纤收发器；而千兆网络通信使用 FCLF8521P2 BTL 型号以太网 SFP 模块，该模块使用 RJ45 接口，通过寻常网线即可连接到其他网络设备上。

#### 2.1.5 背板接口电路

主处理模块基于兼容性考虑，保留了 MTCA 机箱平台的背板总线连接，以便实现更灵活的数据传输与处理功能。机箱背板共有 20 个 Port，每个 Port 都有一收一发两对高速差分线，不同 Port 可用于实现不同功能。主处理模块卡将 12 个 GTH 连到了 Port0~11 上面，其中 Port0、1 分别连接到两块交换卡上，可实现千兆网络通信；Port2、3 可用于相邻槽位插卡间的数据通信；Port4~7 与 Port8~11 分别与交换卡 1、2 相连，可实现×4 链路的 PCIe 或者 SRIO 总线通信。

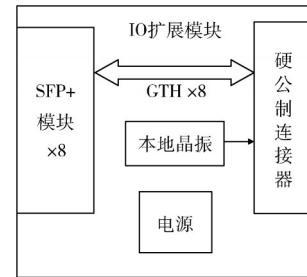

#### 2.2 IO 扩展模块设计

IO 扩展模块电路结构如图 7 所示，IO 扩展模块使用 MPS 公司的 MPM3630GQV-Z 型号 DC-DC 直流降压芯片，将主处理模块通过硬公制连接器提供的 12 V 电源转为 3.3 V，供 8 路 SFP+ 模块使用；板上有 8 路 SFP+ 模块与 2 路 156.25 MHz 频率的本地晶振，通过硬公制连接器将相应信号送至主处理模块上的 FPGA 以实现光纤链路数据通信。

图 7 IO 扩展模块电路结构框图

### 3 硬件电路测试

为验证数字触发判选电路的实测性能是否符合设计时的指标，在实验室环境下对电路逻辑的数据传输与缓存接口进行相应测试。

#### 3.1 高速串行数据传输测试

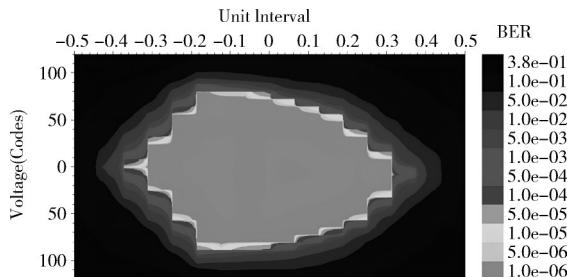

为验证高速串行数据传输的稳定性，对高速串行收发器进行误码率测试<sup>[15]</sup>，在 FPGA 逻辑里例化 Xilinx 提供的专用于高速串行收发器误码率测试的 IBERT IP 核，通过 IBERT 工具得到误码率与眼图测试结果。测试时相邻两对收发器互相通过光纤传输数据，IBERT IP 核产生 PRBS-7 伪随机码对传输链路进行测试，现场照片如图 8 所示。经过约 10 小时的测试得到如图 9 所示的误码率测试结果，光纤链路传输了约  $3.79 \times 10^{14}$  bit 大小的数据量，通道误码数为 0，在 99% 的置信度下小于  $2.645 \times 10^{-15}$ 。其中一条链路眼图测试结果如图 10 所示，眼图睁开范围较大，具有较好信号完整性。

图 8 现场测试照片

| Name                   | TX          | RX          | Status     | Bits     | Errors | BER       |

|------------------------|-------------|-------------|------------|----------|--------|-----------|

| <b>Found Links (4)</b> |             |             |            |          |        |           |

| Auto detected link 0   | Quad_128... | Quad_128... | 8.125 Gbps | 3.79E14  | 0E0    | 2.639E-15 |

| Auto detected link 1   | Quad_128... | Quad_128... | 8.125 Gbps | 3.79E14  | 0E0    | 2.639E-15 |

| Auto detected link 2   | Quad_128... | Quad_128... | 8.125 Gbps | 3.79E14  | 0E0    | 2.639E-15 |

| Auto detected link 3   | Quad_128... | Quad_128... | 8.125 Gbps | 3.781E14 | 0E0    | 2.645E-15 |

图 9 IBERT 测试误码率结果

图 10 IBERT 测试眼图

### 3.2 SiTCP 上行网络通信测速

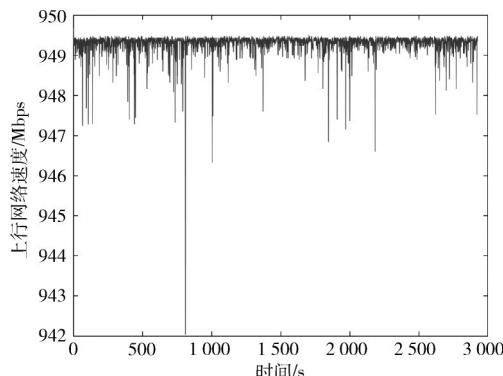

SiTCP 使用 TCP 连接实现硬件电路与上位机之间的数据通信,硬件内逻辑持续通过 SiTCP 上传数据。在上位机编写测速程序测试其上行网速,上位机作为客户端与数字触发判选电路建立 TCP 连接,持续接收数字触发判选电路上传的数据,并对其上行网络数据通信速率进行测试。实测的网络通信速率如图 11 所示,上行的平均网络通信速率最高可达 949.3 Mb/s 左右。

图 11 SiTCP 上行网络传输测速

### 3.3 DDR4 数据读写测试

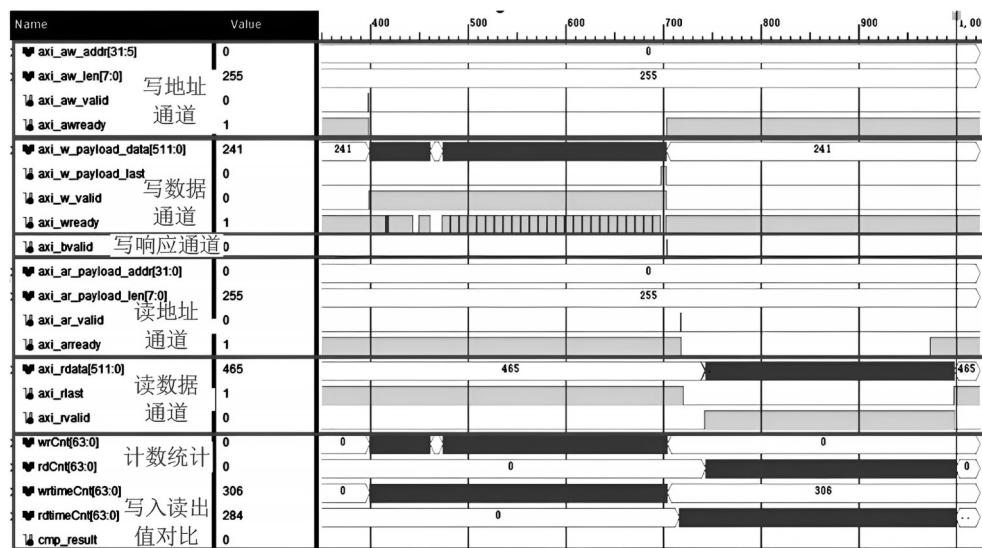

为验证 DDR4 芯片的高速数据缓存是否能够正常工作,编写了数据缓存接口的测试逻辑,例化了 Xilinx 提供的 AXI4 总线接口的 DDR4 MIG IP 核<sup>[16]</sup>,DDR 传输速率设定为 2 000 MT/s,理论传输带宽为 128 Gb/s。测试逻辑持续产生数据递增码,并通过 AXI4 接口依次向 DDR 地址单元中写入数据,随后再读出数据检测是否符合预期,通过多次操作验证 DDR 缓存接口功能正确性,并记录运行时间与写入读出的数据量进行读写测速。

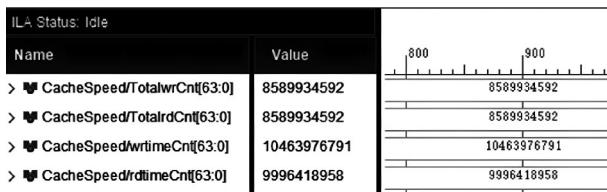

某次写入读出过程的逻辑波形如图 12 所示,写入读出功能正常,读出数据与写入数据完全一致。在经过 128 次对 DDR 所有地址单元的写入读出循环操作后得到如图 13 所示的测速结果,共完成了 4 096 Gb 数据量的 DDR 数据读写操作,写入读出分别消耗了 10 463 976 791、9 996 418 958 个时钟周期,在整个测试过程中写入与读出值完全一致,数据读写无误,DDR 写入读出速度如表 1 所示。

### 4 结论

针对核与粒子物理实验中的数字 NHit 触发判选需求,本文设计实现了一种高性能数字触发判选电路,可支持多通道的光纤数据传输与千兆网络通信、高速大容量数据存储以及实时 FPGA 数字触发处理。在实验室条件下进行了数据传输与缓存接口测试,测试结果表明板卡可实现 8.125 Gb/s 光纤链路的高速串行数据传输速率,SiTCP 上行网络传输速率达 949.3 Mb/s,DDR 数据读写速率可达 102.6 Gb/s,满足电路设计需求。该硬件电路具有较强的扩展性与灵活性,可通过多个该模块的扩展,灵活应用在各个物理实验中。本文在完成硬件电路的设计实现以及数据传输与缓存接口的性能测试工作基础上,后续将结合数字 NHit 触发算法,完成数字触发判选电路的完整逻辑设计工作,并进行多个模块扩展的

图 12 DDR4 读写测速波形

图 13 DDR4 读写操作消耗时钟周期计数

表 1 DDR4 实测写入与读出速度

| 实测写速度/<br>(Gb/s) | 实测读速度/<br>(Gb/s) | 写入效率/<br>% | 读取效率/<br>% |

|------------------|------------------|------------|------------|

| 102.61           | 107.41           | 80.17      | 83.92      |

系统级别综合调试验证。

#### 参考文献

- [1] 王贻芳, 阮曼奇. 探究物质最基本的结构——从中微子和正负电子对撞谈起[J]. 自然杂志, 2017, 39(6):391–400.

- [2] 王贻芳. 探究物质最深层次的物理规律: 中国粒子物理发展规划的思考[J]. 科技导报, 2021, 39(3):52–58.

- [3] 彭猛, 贺国珠, 骆宏, 等.  $4\pi$  BaF<sub>2</sub>装置的触发系统研究[J]. 原子能科学技术, 2016, 50(10):1866–1870.

- [4] 邓文迪. CBM-TOF 无触发数据获取系统数据压缩算法研究[D]. 武汉: 华中师范大学, 2016.

- [5] 王强. PANDA 实验 EMC 新型触发与数据获取系统研究[D]. 北京: 中国科学院研究生院, 2011.

- [6] 卢晓旭, 顾旻皓, 朱科军, 等. LHAASO 地面簇射粒子阵列在线实时分布式数据处理[J]. 核技术, 2020, 43(4): 80–88.

- [7] XIE L, CAO P, YU T, et al. Real-time digital trigger system for GTAF-II at CSNS Back-n white neutron source[J]. Journal of Instrumentation, 2021, 16(10): P10029.

- [8] GONG G, GONG H, LI H, et al. The global trigger with online vertex fitting for low energy neutrino research[C]//

ICALEPCS, 2015: 1107–1110.

- [9] 祝星, 沈仲弢, 赵珂庆, 等. 面向暗物质直接探测的原型液氩探测器读出电子学系统设计[J]. 原子能科学技术, 2020, 54(12):2439–2447.

- [10] LARSEN R S. Recent progress in next-generation platform standards for physics instrumentation and controls[C]// 2012 18th IEEE-NPSS Real Time Conference, 2012.

- [11] 王松明. 高速数据交换的 FPGA 实现[J]. 微型机与应用, 2017, 36(24):98–101.

- [12] 王之光, 高清运. 基于 FPGA 的 PCIe 总线接口的 DMA 控制器的设计[J]. 电子技术应用, 2018, 44(1):9–12.

- [13] 辛云旭, 文丰, 张凯华. 基于 Serial RapidIO 的远距离高速数据传输[J]. 电子测量技术, 2021, 44(21):125–132.

- [14] 吕子祎, 李星, 宋超凡, 等. 一种便捷的探测器数据传输技术的实现[J]. 电子测量技术, 2020, 43(16):142–145.

- [15] 沈瀚涛, 孙学聪, 朱蕊蘋. 一种串行通信的误码率测试方法[J]. 现代防御技术, 2013, 41(4):110–114.

- [16] ZHENG J, YAN K, ZHANG Y, et al. Design and implementation of DDR4 SDRAM controller based on FPGA [C]// 2018 2nd IEEE Advanced Information Management, Communicates, Electronic and Automation Control Conference (IMCEC), 2018: 421–424.

(收稿日期: 2022-04-29)

#### 作者简介:

刘尚铭(1998-), 男, 硕士研究生, 主要研究方向: 物理实验数据读出与信号处理等。

曹平(1980-), 通信作者, 男, 博士, 副教授, 主要研究方向: 物理实验数据获取与处理, E-mail: cping@ustc.edu.cn。

李超(1992-), 男, 博士, 主要研究方向: 物理实验数据采集与信号处理。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所