# 射频模块中晶振对电磁兼容影响研究

马世娟,肖永平,倪晓东

(中科芯集成电路有限公司,江苏 无锡 214072)

**摘要:** 提出了一种 SoC 芯片时钟方案,并设计了两种版图方案。针对模块中产生电磁干扰的原因进行分析,通过判断信号间隔离度仿真结果,可提前识别版图方案中是否存在信号间干扰风险,进而恶化 SoC 芯片输出模拟信号质量。根据信号间隔离度仿真结果指导版图设计,并给出优化版图方法,改善了信号间隔离度性能。测试结果表明,版图设计两种方案的仿真结果与实测结果吻合,验证了仿真结果的准确性、可参考性。

**关键词:** 电磁兼容;电磁干扰;数模混合;隔离度

中图分类号: TN74

文献标志码: A

DOI: 10.16157/j.issn.0258-7998.223049

中文引用格式: 马世娟,肖永平,倪晓东. 射频模块中晶振对电磁兼容影响研究[J]. 电子技术应用,2023,49(2):102-105.

英文引用格式: Ma Shijuan, Xiao Yongping, Ni Xiaodong. Research of the influence of crystal oscillator on EMC in RF module [J]. Application of Electronic Technique, 2023, 49(2): 102-105.

## Research of the influence of crystal oscillator on EMC in RF module

Ma Shijuan, Xiao Yongping, Ni Xiaodong

(China Keys System & Integrated Circuit Co., Ltd., Wuxi 214072, China)

**Abstract:** This paper proposes a SoC chip clock scheme and designs two layout schemes. By analyzing the causes of electromagnetic interference and judging the simulation results of the isolation degree between signals, the risk of inter-signal interference in the layout scheme can be identified in advance, which will deteriorate the output analog signal quality of SoC chip. In this paper, the simulation results of the isolation degree between signals are used to guide the layout design, and the optimization layout method is given to improve the performance of the isolation degree between signals. The test results show that the simulation results of the two layout design schemes are consistent with the actual results, which verifies the accuracy and reference of the simulation results.

**Key words:** EMC; EMI; digital-analog hybrid; isolation

## 0 引言

20世纪70年代,研究者发现通过在不同介质表面上引入周期性的结构可对电磁波幅度进行控制。该类设计可对不同频率下的电磁波产生滤波器效应。21世纪,研究者对电磁波的控制拓展到相位层面,利用周期性界面对面电磁波的幅度和相位进行控制。电磁场的应用带动科技突飞猛进的发展<sup>[1]</sup>。但在实际应用中,有用电磁波被利用的同时,无用电磁波给系统或者模块造成干扰,导致系统或者模块不能正常工作。

随着通信技术的不断发展,飞机、船舶、卫星、地面应用等载体的需求量越大、功能越来越复杂,其间的电磁干扰也变得尤为突出<sup>[2-4]</sup>。根据电磁兼容(EMC)的定义,不难理解,某一设备不会干扰处在同一电磁环境中的其他设备,同时自身也不会受到其他电磁干扰(Elec-

tromagnetic Interference, EMI)的影响。现在大多数产品均对 EMC 提出了要求。同时,相关领域也制定了详细的标准、规范以及辐射参考标准。

在实际应用中,对电磁兼容的研究应用大多处于问题解决法的阶段<sup>[5-9]</sup>。文献[10]利用 CST 仿真机壳缝隙大小与电缆间耦合大小等参数,实现电磁辐射干扰的有效抑制,但并未对板级电磁兼容进行研究与仿真;文献[11]结合测试事例,讨论按元器件布局与布线原则来达到抗干扰设计的目的,并未对其中间过程进行研究。在产品预言前期,缺乏通过仿真手段对电磁干扰进行仿真、分析的手段,以达到提前识别电磁干扰是否存在干扰风险的目的。结合电磁干扰仿真结果,对产品提供理论优化指导,既能最大化减小电磁干扰对产品的影响,也能缩短产品设计周期以及提高产品调试效率。

本文提出了一种 SoC 芯片时钟方案,提供了两种版图设计方案。通过信号间隔离度仿真,提前识别到版图设计方案一中 CLK50M 与 clk3 差分对间的隔离度低,存在 CLK50M 间接干扰 SoC 芯片内部模拟信号的风险,进而恶化 SoC 芯片输出模拟信号质量。根据信号间隔离度仿真结果指导版图设计,本文给出了版图设计方案二。对比两种版图设计方案的实测结果,方案一的输出模拟信号测试结果中存在干扰,而方案二的输出模拟信号测试结果中无干扰。测试结果验证了仿真结果的准确性。与传统的建模仿真方法相比,本文提出的板级隔离度仿真方法具有高效、准确的优点。同时该方法也具有较强的实用型,可应用于板级任意两信号的隔离度评估,对规避板级 EMI 风险以及模块 EMC 具有参考意义。

## 1 硬件方案设计

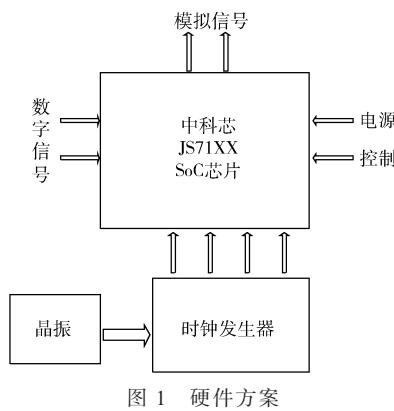

模块主要实现功能为信号处理,即将数字信号处理成中频模拟信号,中频模拟信号经过滤波等输出到连接器。其中,时钟发生器产生 4 对差分时钟提供给 SoC 芯片(JS71XX 型高速多通道信号处理电路),晶振输出的 50 MHz 时钟信号为时钟发生器提供参考时钟。为了避免晶振信号通过耦合路径将时钟谐波干扰信号带入到芯片内部,本方案要求晶振输出时钟信号与时钟发生器产生 4 对差分时钟间的隔离度为 60 dB。

如图 1 所示,方案中采用中科芯的 JS71XX 型高速多通道信号处理电路,其封装采用 SiP 封装,简称 SoC 芯片。该 SoC 芯片主要功能有完成模拟信号数字化、信号正交变换、通道校准、功率控制、中频模拟信号输出等。

图 1 硬件方案

在方案实施版图设计时,重点评估晶振信号及时钟发生器输出信号对模拟信号的干扰影响,评估时钟信号与模拟信号间的隔离度。

## 2 方案设计与仿真

### 2.1 方案设计

为了时钟信号与模拟信号间的隔离度,根据设计经验,本方案提供了两种不同版图设计方案 SoC 芯片、晶振、时钟发生器三部分的布局、布线,其他部分的布局、

布线方案均相同,用于分析对比布局、布线对隔离度的影响。

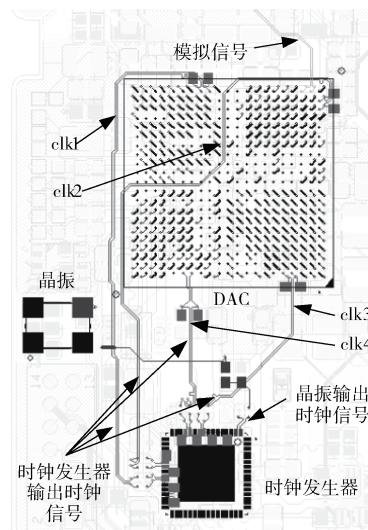

第一种版图设计方案中,晶振位于 SoC 芯片左下方,时钟发生器位于晶振的右下方且位于 SoC 芯片的下方,其详细布局如图 2 所示。印制板层叠为 8 层,晶振位于上表层,SoC 芯片、时钟发生器两个器件位于下表层。晶振输出时钟信号命名为 CLK50M,其相关器件与走线均位于上表层。时钟发生器输出 4 对时钟差分对信号,分别命名为 clk1、clk2、clk3、clk4。clk1、clk2 两对时钟差分对走线位于印制板第 6 层,clk3、clk4 两对时钟差分对走线位于印制板第 3 层。SoC 芯片输出的模拟信号走线位于印制板第 3 层。

图 2 版图设计方案一

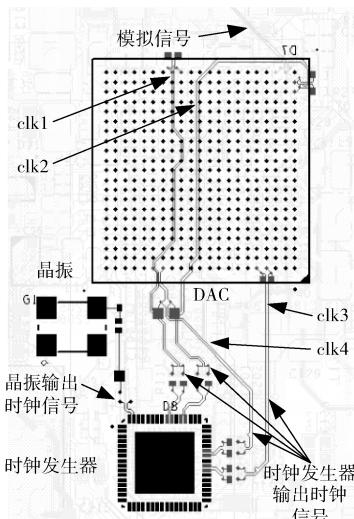

第二种版图设计方案中,晶振位于 SoC 芯片斜下方。时钟发生器位置不变,仍位于晶振的右下方且位于 SoC 芯片的下方,其详细布局如图 3 所示。晶振仍位于上表层,SoC 芯片仍位于下表层。与第一种版图设计方案不同的是,为方便 clk1、clk2 两对时钟差分对走线,将时钟发生器放置于上表层,且印制板层叠调整为 10 层。晶振输出时钟信号 CLK50M 相关器件与走线均位于上表层。为方便走线,将时钟发生器输出 4 对时钟差分对进行换 pin。本文仍按照到达 SoC 芯片 pin 脚位置进行命名,分别为 clk1、clk2、clk3、clk4。clk1、clk2 两对时钟差分对走线位于印制板第 8 层,clk3、clk4 两对时钟差分对走线位于印制板第 3 层。SoC 芯片输出的模拟信号走线位于印制板第 3 层。

### 2.2 仿真

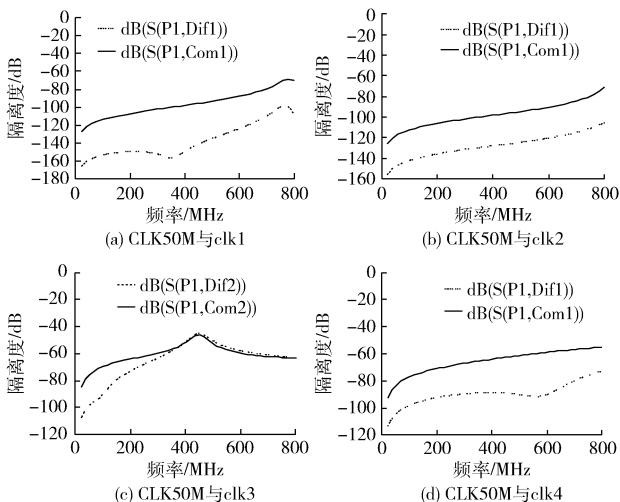

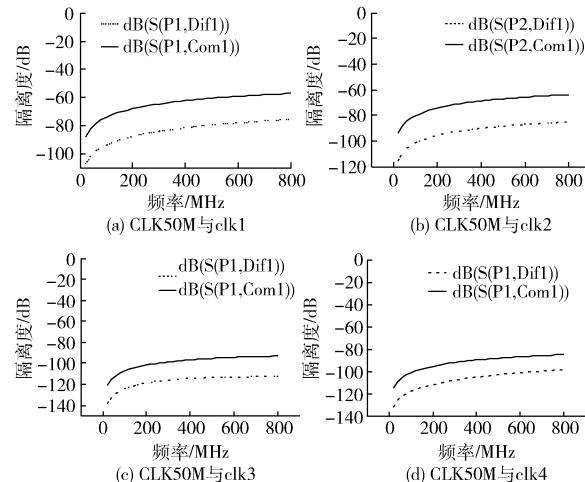

版图设计方案一中,CLK50M 与 clk1、CLK50M 与 clk2、CLK50M 与 clk3、CLK50M 与 clk4 的隔离度分别如图 4(a)、图 4(b)、图 4(c)、图 4(d) 所示。SoC 芯片输出模拟信号的频率为 347.5 MHz,故文中关注 50 MHz 晶振

图3 版图设计方案二

图4 版图设计方案一仿真结果

产生的N次谐波是否通过时钟发生器输出的时钟差分对信号带入到SoC芯片内部,从而影响SoC芯片模拟信号的信号质量。在频率为600 MHz处,CLK50M与clk1差分对间的隔离度为-87 dB,CLK50M与clk2差分对间的隔离度为-98 dB,CLK50M与clk3差分对间的隔离度为-48 dB,CLK50M与clk4差分对间的隔离度为-61 dB。

由仿真结果可以看出,CLK50M与clk1、clk2差分对间的隔离度比CLK50M与clk3、clk4差分对间的隔离度大,其原因为CLK50M走线在上表层,clk1、clk2走线在第6层,而clk3、clk4走线在第3层,且clk3、clk4信号器件与CLK50M信号器件均在上表层且距离较近。

版图设计二中,CLK50M与clk1、CLK50M与clk2、CLK50M与clk3、CLK50M与clk4的隔离度分别如图5(a)、图5(b)、图5(c)、图5(d)所示。在频率为600 MHz处,CLK50M与clk1差分对间的隔离度为-60 dB,CLK50M与clk2差分对间的隔离度为-65 dB,CLK50M

与clk3差分对间的隔离度为-94 dB,CLK50M与clk4差分对间的隔离度为-86 dB。由仿真结果可以看出,CLK50M与clk1、clk2差分对间的隔离度比CLK50M与clk3、clk4差分对间的隔离度大。

图5 版图设计方案二仿真结果

对比以上两种版图设计方案的信号隔离度仿真结果可以看出,因版图设计二中将时钟发生器输出clk1、clk2的pin脚换到了版图设计一中clk3、clk4的pin脚的位置,所以CLK50M与clk1、CLK50M与clk2的隔离度因表层器件位置拉近,其间的隔离度变小。同样,CLK50M与clk3、CLK50M与clk4的隔离度因表层器件位置拉远,其间的隔离度变大。与时钟发生器相同输出pin脚处对比,版图设计方案一中CLK50M与clk3差分对间的隔离度比版图设计二中CLK50M与clk1差分对间的隔离度小12 dB。版图设计方案一中CLK50M与clk4差分对间的隔离度比版图设计二中CLK50M与clk2差分对间的隔离度小4 dB。

### 3 实测结果

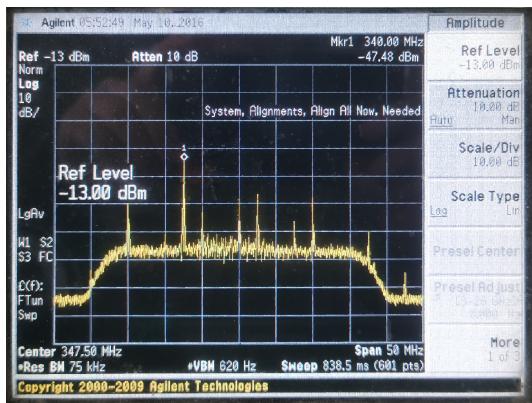

将贴片后的射频模块进行测试。版图设计方案一的测试结果如图6所示,由测试结果可以看出,在347.5 MHz±25 MHz范围内存在杂散干扰,导致模拟信号质量变差,射频模块不能正常工作。

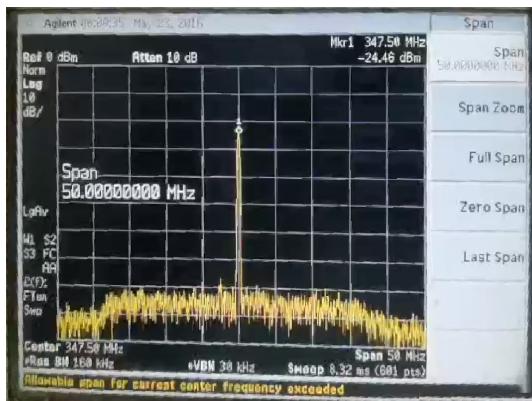

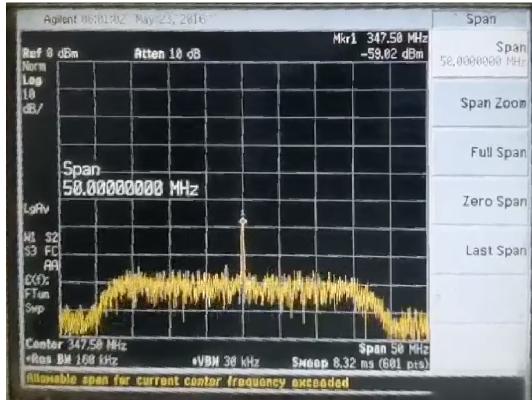

版图设计方案二的测试结果如图7所示。由测试结果可以看出,当模拟信号输出增益为-24.4 dBm时,在347.5 MHz±25 MHz范围内无杂散干扰。当模拟信号输出增益为-59.8 dBm时,在347.5 MHz±25 MHz范围内无杂散干扰。

结合两种方案的版图设计、隔离度仿真结果以及输出信号测试结果分析,版图设计方案一的输出模拟信号测试结果中存在干扰,其原因为时钟发生器的时钟输入信号与时钟输出信号的布局、走线在空间上存在交叉以及布局不优,导致时钟发生器的时钟输入信号与时钟输

图 6 版图设计方案一测试结果

(a) 输出信号增益-24.4 dBm

(b) 输出信号增益-59.8 dBm

图 7 版图设计方案二测试结果

出信号间的隔离度较低,时钟输出信号上存在时钟输入信号的谐波,该谐波干扰通过时钟输入信号带入到SoC芯片内部,从而恶化SoC芯片的输出模拟信号质量。版图设计方案二中CLK50M与clk1差分对间的隔离度比版图设计方案一中CLK50M与clk3差分对间的隔离度大12 dB,版图设计方案二中作为强干扰源的CLK50M、clk1~clk4被保护得比版图设计方案一中的信号好,且时钟发生器的时钟输入信号与时钟输出信号在空间上无交叉以及相关布局优,减小了SoC芯片中模拟信号被干

扰的风险,故版图设计方案二的输出信号质量优于版图设计方案一中的输出信号质量,且不存在干扰。

#### 4 结论

本文提出了一种SoC芯片时钟方案,并设计了两种版图设计方案。针对电磁干扰的原因进行分析,通过判断信号间隔离度仿真结果,可提前识别版图方案中是否存在信号间干扰风险,进而恶化SoC芯片输出模拟信号质量。文中根据信号间隔离度仿真结果指导版图设计,并给出优化版图方法,即拉远干扰源与受干扰体之间的距离,改善了信号间隔离度性能。测试结果表明,版图设计两种方案的仿真结果与实测结果吻合,验证了仿真结果的准确性、可参考性。本文研究结果对规避板级EMI风险以及模块EMC具有参考意义。

#### 参考文献

- [1] 曲美君.射频前端功能融合及电磁兼容研究[D].北京:北京邮电大学,2020.

- [2] 王杨.堆外核测系统的电磁干扰问题研究与工程实践[J].电子技术应用,2021,47(S1):19-23.

- [3] 陈世浩.民用飞机CNS系统电磁兼容分析与设计[J].电讯技术,2020,60(6):713-719.

- [4] 任振兴,彭泽清.某型分系统电磁兼容优化设计[J].航空电子技术,2020,51(2):65-70.

- [5] 邵颖飞,鲁征浩.基于皮尔斯振荡器的8 MHz晶振电路设计[J].电子与封装,2021,21(2):96-101.

- [6] 钱宏文,刘继祥,吴翼虎,等.ADC测试中同源时钟分析与解决方案[J].电子与封装,2021,21(1):24-27.

- [7] 潘旭麒,李进,袁健,等.对于EMC封装模具离型性的改良研究[J].电子与封装,2021,21(6):19-24.

- [8] 涂波,王兴宏.基于锁相环多相位时钟实现小数分频的方法[J].电子与封装,2020,20(1):35-38.

- [9] 王洪伟.强电磁干扰下远距离综合无线通信设计[J].电子技术应用,2015,41(4):40-42,49.

- [10] 胥朋,徐亮,陈琦,等.基于仿真的电磁辐射抗干扰措施及验证[J].微波学报,2014,30(S2):58-60.

- [11] 马宁,陈莉.射频电路板抗干扰设计[J].现代雷达,2005(9):75-77.

(收稿日期:2022-06-01)

#### 作者简介:

马世娟(1989-),女,硕士研究生,工程师,主要研究方向:天线理论分析与设计、无源器件设计、射频微波模块等,E-mail:msj11111@126.com。

肖永平(1983-),男,本科,工程师,主要研究方向:微波模块设计、电磁兼容分析仿真及集成电路封装工艺研究等。

倪晓东(1984-),男,本科,工程师,主要研究方向:电子元器件方案设计、仿真及应用。

扫码下载电子文档

## 版权声明

经作者授权，本论文版权和信息网络传播权归属于《电子技术应用》杂志，凡未经本刊书面同意任何机构、组织和个人不得擅自复印、汇编、翻译和进行信息网络传播。未经本刊书面同意，禁止一切互联网论文资源平台非法上传、收录本论文。

截至目前，本论文已经授权被中国期刊全文数据库（CNKI）、万方数据知识服务平台、中文科技期刊数据库（维普网）、DOAJ、美国《乌利希期刊指南》、JST 日本科技技术振兴机构数据库等数据库全文收录。

对于违反上述禁止行为并违法使用本论文的机构、组织和个人，本刊将采取一切必要法律行动来维护正当权益。

特此声明！

《电子技术应用》编辑部

中国电子信息产业集团有限公司第六研究所