0 引言

2009年1月国内3G牌照正式发放,随着3G时代的到来,各大通信运营商对3G移动通信网络展开了大规模建设,投入巨大,而基站是3G网络建设中,数量最多及成本最高的设备。移动通信领域日趋激烈的竞争,使得通信运营商比以往更加关注建网成本,而分布式基站具备低成本、高性能、快速运营等特性,能够大大节省运营商的建网与运维成本。因此分布式基站成为当前3G网络建设的最主要选择。

分布式基站核心理念,是把传统宏基站基带处理单元(BBU" title="BBU">BBU)和射频拉远单元(RRU" title="RRU">RRU)分离,二者通过光纤" title="光纤">光纤相连。网络部署时,将BBU、核心网、无线网络控制设备集中在机房内,与规划站点上部署的RRU通过光纤连接,完成网络覆盖。

为了有效处理分布式基站BBU与RRU间的光纤连接,无线通信行业形成两个联盟,分别制定了两种接口标准:2002年诺基亚、LG、三星等宣布成立OBSAI(开放式基站结构同盟);2003年爱立信、华为、NEC、北电和西门子等联合成立CPRI" title="CPRI">CPRI (通用公共无线接口组织)。本文主要介绍基于CPRI协议的光纤通讯。

1 CPRI协议概述

CPRI协议定义了两个协议层。两个协议层为物理层(L1)和数据链路层(L2)。在物理层中,将上层接入点的传输数据进行复/分接,并采用8B/10B编解码,通过光模块串行收发数据。数据链路层定义了一个同步的帧结构,包含基本帧和超帧(由256个基本帧组成),数据在L2层中,通过CPRI固定的帧结构形式进行相应的成帧和解帧处理。

基带处理单元(BBU)和射频拉远单元(RRU)之间可以通过一条或多条CPRI数据链路来连接,每条CPRI数据链路支持614.4Mbps、1228.8M-bps和2457.6Mbps三种比特率高速串行传输。当前工业界,通过将四条并行CPRI数据链路进行相应串行化处理,可实现BBU与RRU之间通过光纤以近10Gbps(即4X2457.6 Mbps)速率超高速传输。

2 硬件方案

采用FPGA" title="FPGA">FPGA来设计实现基于CPRI协议的光纤通讯,可以有多种方案来实现,下面介绍两种方案。

方案一:采用集成了RocketIO模块的FPGA。RocketlO收发器是在Xilinx公司Virtex2 Pro以上系列FPGA芯片中,集成的功能可配置千兆位级串行收发器。可通过调用Xilinx公司的COREGenerator生成的IPCore来使用RocketIO收发器。该模块的功能包括8B/10B编解码,串并转换,时钟与数据流的绑定以及时钟恢复等。使用此方案优点是,可以使电路板尺寸较小、结构紧凑,可方便设置参数;缺点是,一般集成了RocketIO的FPGA芯片价格均较高,必然带来开发成本的提高,同时开发周期相对也较长。

方案二:FPGA与SCAN25100相结合。SCAN25100是美国国家半导体专门为新一代基站结构推出的串行/解串器,其集成了高精度延迟校准测量(DCM)电路及独立的发送和接收系统锁相环路,还具备先进的高速混合信号和时钟管理以及信号调节等功能。同时芯片具备8B/10B编解码、高速串并转换、锁定检测、CPRI信号和帧丢失检测等功能。可根据这款芯片来构建多天线技术分布式基站光纤互连解决方案。此方案开发成本较低,调试简单方便,性能稳定。

2.1 方案整体设计

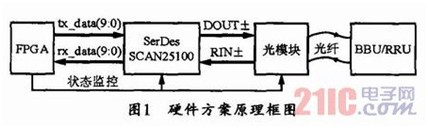

本文主要针对方案二进行介绍与讨论。该方案设计,由FPGA完成CPRI协议的成帧、解帧、同步、传输数据复,分接等操作,以及与SCAN 25100相关接口设计,同时负责对SCAN25100与光模块控制与状态监控。SCAN25100负责实现8B/10B编解码和高速串并转换功能。

FPGA与SCAN25100之间通过使用并行数据线传输,SCAN25100的并行数据线支持8位和10位两种模式,这里选择用FPGA将SCAN25100配置成10位模式。SCAN25100完成8B/10B编解码和高速串并转换,与光模块通过差分串行数据线相连。最后由光模块完成光、电信号转换,通过光纤与外部设备进行数据传输,实现光纤通讯数据收发。其方案原理框图如图1所示。

2.2 时钟方案

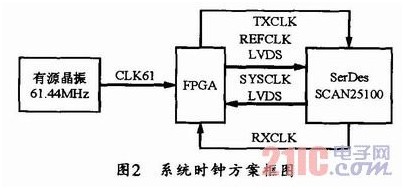

采用输出频率为61.44MHz的有源晶振为FPGA提供系统基准时钟(CLK61),系统所需的其他频率时钟,均可使用FPGA内置的时钟管理模块,对CLK61进行分频、倍频及移相而得。SCAN25100有四个时钟端口,与FPGA相连。系统时钟方案如图2所示。

SCAN25100芯片内置振荡器能够产生一个30.72MHz时钟SYSCLK输出,提供给FPGA作参考时钟。当系统作为REC端时,FPGA需要提供一个30.72MHz时钟REFCLK,给SCAN25100作为参考时钟。REFCLK和SYSCLK均使用LVDS差分电平,在FPGA内部使用缓冲器IBUFGDS来将输入差分时钟信号转为单端时钟,而使用OBUFDS将单端时钟转为差分时钟输出。

TXCLK为FPGA输出给SCAN25100,用于采集输出数据tx_data(9:0)的时钟。RXCLK为SCAN25100输出给FPGA,用于采集输入数据rx_data(9:0)的时钟。TXCLK和RXCLK配置使用INCMOS18电平,均为双边沿采集数据,其时钟频率由用户根据需求配置SCAN25100串行接口(DOUT和RIN)的传输速率决定。SPMODE(1:0)的配置值决定传输速率,对应关系见表1。

2.3 PCB布板设计

PCB布板设计要特别注意信号完整性问题,尤其当系统设定速率为2457.6Mbps高速传输时。图3所示为系统速率设定为2457.6Mbps,未注意信号完整性问题的PCB布板设计下,TXCLK时钟信号眼图,可以看到时钟信号质量较差。而SCAN25100对TXCLK信号质量要求较高,如占空比要求为45%~55%范围。经测试,在此设计下,当系统工作于614.4Mbps或1228.8Mbps时,系统能正常传输数据,但当系统速率转换为2457.6Mbps,此时TXCLK/RXCLK双边沿对DDR(Double Data Rate)数据出现了错误采集,SCAN25100与光模块之间的差分串行数据线传输也变得不稳定。因此系统对PCB布板设计要求较高。