摘 要: 复位是FPGA设计中一个基本而又重要的问题,如果处理不当,不仅可能导致亚稳态的问题,而且会降低设计的资源利用率。分析了不同的复位方式对系统亚稳态和资源利用率的影响,并对不同的目标器件中复位信号的使用给出了建议。

关键词: 复位;亚稳态;资源利用率

在FPGA设计中,复位信号扮演着重要的角色,设计人员通常都使用一个外部输入的全局复位信号在上电初期对系统进行初始化[1-2]。通常,FPGA中的全局复位信号一般由3种途径获得[3]:(1)用一个复位按钮产生一个复位信号接到FPGA的全局复位管脚上,它的速度非常慢,而且存在抖动的问题;(2)上电时由电源芯片产生,如TI公司TPS76x系列的电源系统一般都可以产生复位信号,供主芯片上电复位使用;(3)由微处理器产生复位脉冲,这个是设计人员可以方便使用程序控制的。

全局复位管脚类似于其他任何输入管脚,通常都是异步的,设计人员可以在FPGA中将其当作异步或同步复位信号来使用, 但一个最佳的复位结构却可以对FPGA的亚稳态和资源利用率产生很大的影响。

1 复位与亚稳态

1.1 异步复位

在大多数FPGA设计中,外部输入的全局复位信号被直接当作异步复位来使用。这种用法在可控的仿真环境下工作正常,然而在真实的系统中却常常会出现不规律的错误,其原因在于设计人员常常低估了真实系统中复位信号的“释放”问题,这个问题可能导致系统中的触发器进入亚稳态,从而影响整个系统的稳定性[4]。

常用的异步复位电路Verilog描述如下:

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n) q <= 1’b0;

else q <= d;

end

在Quartus Ⅱ中综合出的异步复位电路模型如图1所示。图2为异步复位电路的复位时序图。

如果异步复位信号的撤销时间在Trecovery(恢复时间)和Tremoval(移除时间)之内,则造成亚稳态的产生,触发器的输出在时钟边沿的Tco后会产生振荡,最终稳定到“0”或者“1”,这就有可能造成复位失败。

1.2 同步复位

由于全局复位信号通常是异步的,因此,有些设计人员采用同步复位电路对FPGA进行复位,并且绝大多数文献资料认为同步复位电路都不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

常用的同步复位电路Verilog描述如下:

always @ (posedge clk)

begin

if(!rst_n) q <= 1’b0;

elseq <= d;

end

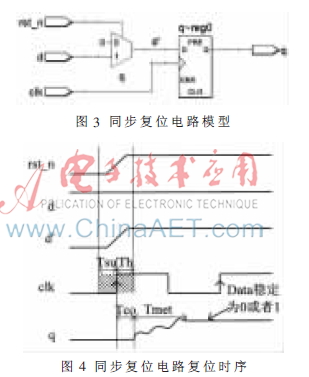

在Quartus Ⅱ中综合出的异步复位电路模型如图3所示,其复位时序图如图4所示。

当输入端d为高电平且复位信号的撤销时间在clk的Tsu(建立时间)和Th(保持时间)内时,亚稳态就随之产生了。如图4所示,当复位信号的撤销时间在clk的Tsu和Th内时,输入数据为“1”,通过和输入数据相“与”后产生的信号d’也在clk的Tsu和Th内,因此,势必会造成类似异步信号采集的亚稳态情况。

1.3 异步复位、同步释放

为了解决单纯的异步复位或同步复位所带来的亚稳态问题,一种常用的处理方式是异步复位、同步释放。其Verilog描述如下:

always @ (posedge clk or negedge rst_n_asyn)

begin

if (!rst_n_asyn)

begin

temp <= 1′b0;

rst_n_syn <= 1′b0;

end

else

begin

temp <= 1′b1;

rst_n_syn <= temp;

end

end

在Quartus Ⅱ中综合出的异步复位、同步释放电路模型如图5所示。

由图5可以看出,新产生的复位信号rst_n_syn是一个同步化了的异步复位信号,其复位时刻的到来不受时钟信号的影响,同时其复位释放的时刻却与时钟信号同步。这种复位方式很好地将异步复位和同步复位的优点结合起来,设计人员在开发FPGA工程时只需要在每个时钟域内用这种异步复位、同步释放的复位结构产生一个局部的复位信号rst_n_syn,并用它来对该时钟域内的所有模块进行复位,便可以有效地降低亚稳态出现的几率。

2 复位与资源利用率

在不同的目标器件中,寄存器对复位的异步或同步、高电平或低电平有不同的要求和实现,因此,不同的复位方式对FPGA的资源利用率也将产生很大的影响。

2.1 Altera公司的FPGA

在Altera公司的FGPA中,每个寄存器都有一个异步的清零输入端[5]。高/低电平的异步/同步复位电路在Quartus Ⅱ中综合出的电路模型如图6~图9所示。

由图6~图9所示的电路模型可以看出,在Altera公司的FPGA中,不论是高电平还是低电平的异步复位,直接使用了寄存器的CLR端口;然而如果是同步复位,综合后会在其寄存器的数据路径上增加一个数据选择器,将复位信号作为输入逻辑的使能信号,这样不仅增加了设计的资源占用量,而且增加了数据信号的路径时延。

2.2 Xilinx公司的FPGA

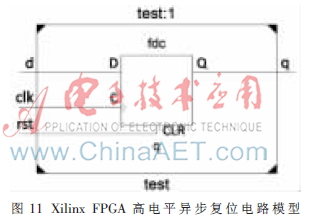

在Xilinx公司的FGPA中,每个寄存器都有一个专用的清零输入端[6]。高/低电平的异步/同步复位电路在ISE 12.4中综合出的电路模型如图10~图13所示。

由图10~图13所示的电路模型可以看出,在Xilinx的FPGA中,不论是同步的还是异步的高电平复位,直接使用了寄存器的专用清零输入端;然而如果是低电平复位,综合后会在复位路径上增加一个反相器,这样不仅增加了设计的资源占用量,而且增加了复位信号的路径时延。

从以上分析可以看出, 在FPGA设计中,通过异步复位、同步释放的复位结构将外部输入的全局复位信号进行同步化,可以降低系统中亚稳态出现的几率,增加系统复位的可靠性; 同时,在Altera公司的FPGA中对寄存器使用高电平或低电平的异步复位、在Xilinx公司的FPGA中对寄存器使用异步或同步的高电平复位,均可以降低设计的资源占用量,提高资源利用率。因此,在FPGA设计时,设计人员应该根据不同的应用场景和不同的目标器件区别使用复位方式,以取得最佳的复位效果。

参考文献

[1] 周伟,杜玉晓,杨其宇,等.FPGA跨时钟域亚稳态研究[J].

电子世界, 2012(3):87-89.

[2] 黄隶凡,郑学仁.FPGA设计中的亚稳态研究[J]. 微电子

学, 2011,41(2):265-268,273.

[3] CHAPMAN K. Get smart about reset think local, not

global[Z]. Xilinx FPGAs, 2008.

[4] 汪路元.FPGA设计中的亚稳态及其缓解措施[J].电子技

术应用,2012,38(8):13-15.

[5] Altera. Cyclone IV device handbook[Z].2013.

[6] Xilinx. Virtex-5 family overview[Z].2009.