文献标识码: A

文章编号: 0258-7998(2014)11-0036-03

0 引言

近年来,大规模集成电路的快速发展使其在计算机视觉领域得到了广泛的应用。而运动目标检测技术是计算机视觉的重要组成部分,因此吸引了世界各国科学研究者投入到对这一技术的研究[1-2]。

目前,运动目标检测最常用的是帧间差分算法、背景差分算法和光流法3种算法。通过比较,本系统采用易于硬件实现、实时性好的帧间差分算法[3-4]。FPGA内含丰富的逻辑资源,加之内嵌着DSP块,有着出色的计算能力;同时FPGA采用的体系是并行体系且具有流水性的工作方式,可以加快数据流的数据。因此,本设计采用FPGA模块作为主控制和算法处理单元。

1 系统的总体结构

整个系统由视频信号采集单元、控制和算法实现单元、数据缓存单元和视频信号显示单元四部分组成,如图1所示。

视频采集单元在FPGA的控制下,对带有运动目标的模拟视频进行采集,并转换为数字视频信号传输到FPGA进一步处理;FPGA主要负责对其他模块进行功能控制以及对传入的视频信号进行灰度化、帧间差分和阈值分割,以实现运动目标的检测; 数据缓存单元是在FPGA的控制下,完成对视频图像数据的缓存,配合FPGA进行图像处理;视频信号显示单元是在FPGA的控制下对处理前后的视频图像进行显示,可以直观地观察检测效果。

2 系统硬件设计

2.1 视频信号采集单元

本系统使用的CCD(Charge Coupled Device)相机输出PAL制式视频。而FPGA只能处理数字视频信号,因此需要将PAL制式信号转换为标准的数字视频格式。飞利浦公司研制的SAA7113H是一款功能强大的9位视频解码芯片,它可以自动检测视频制式,并且可以输出包含YUV4:2:2在内的不同格式的数字视频。图2所示为本系统中视频解码模块的电路图。

本设计仅使用4路输入通道中的1路即可,将SAA7113H解码后的数字视频信号传输给FPGA进行下一步处理,片选信号CE接高电平时,芯片选通;像素时钟接口LLC外接27 MHz时钟信号。

2.2 视频图像缓存单元

在完成运动目标检测的过程中,需要至少缓存一帧图像。为了节省FPGA内部有限的存储资源,缓存数据量巨大的视频图像时,本系统采用外接DDR SDRAM来进行数据缓存。Hynix公司研制的存储容量为2 M×4 Banks×16 bit的HY57V281620FTP-H型号SDRAM满足本设计要求。其各引脚功能如表1所示。其中WE#无效时进行读操作;A0~A11为行列地址选择信号,当列有效时,使用A0~A8表示列地址,当行有效时,使用A0~A11表示行地址,其中A10还是自动预充的标记[5]。

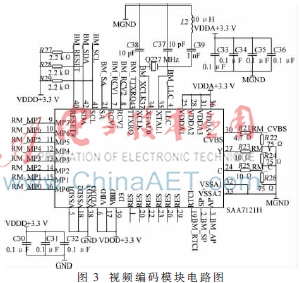

2.3 视频图像显示单元

经过FPGA处理输出的视频信号为数字信号,而一般的显示器只能显示模拟信号,因此需要将数字视频信号转换为模拟视频信号进行显示。飞利浦公司的视频编码芯片SAA7121H转换效率高,设计简单,可以将FPGA处理输出的YCbCr格式的数字视频信号编码成可以直接显示的PAL制式的模拟视频信号,本设计采用此芯片完成视频编码并进行显示。其电路如图3所示。

MP0~MP7是8个数字视频数据输入端口;RCV1、RCV2是行、场同步信号接口;LLC是27 MHz像素时钟信号接口;SCL、RESET和SDA分别是串行时钟信号线、复位信号以及双向串行数据信号线,设计时这3个接口都要外接一个2.2 kΩ的上拉电阻。CVBS是CVBS信号的输出端口,与显示屏连接可显示视频图像。

3 系统软件设计

3.1 帧间差分算法

帧间差分算法是对视频信号中相邻帧或者多帧图像中同一位置的像素点进行差分运算。现在以相邻帧的帧间差分算法为例,其基本流程如图4所示。设第k-1帧图像中(x,y)位置处的像素值为fk-1(x,y),第k帧相同位置处的像素值为fk(x,y),先对二者按式(1)进行差分运算得到?驻k(x,y),再将?驻k(x,y)按式(2)进行二值化处理。

其中,T为预设“阈值”,可以从0~255中取值,具体大小与实际环境有关。当k(x,y)≥T时,Rk(x,y)=1,此时判断该像素点为运动区域像素点;当?驻k(x,y)<T时,Rk(x,y)=0,此时判断该像素点为静止区域像素点。

帧间差分算法中两帧图像相差的时间短,使得环境中光线变化等不可控因素对设计的影响较小,因此具有良好的抗干扰性,且对动态环境有很强的适应能力。

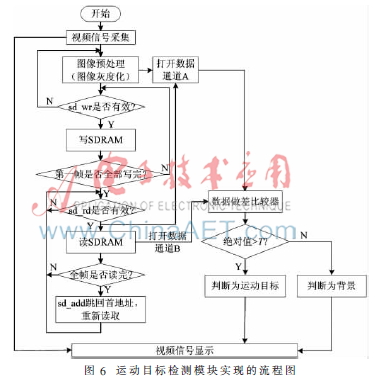

3.2 帧间差分算法的实现

系统开始工作后,FPGA先通过I2C总线对SAA7113H和SAA7121H进行初始化,使视频采集及视频显示单元能够正常工作。配置流程如图5所示。

视频信号采集单元采集的有效视频数据分两路传输:一路直接传输给视频信号显示单元进行显示,用来与处理后的结果进行对比分析;另一路传输给图像预处理模块进行灰度化处理,以备后续处理。经过图像预处理模块后的视频数据仅有Y分量;同时需要设置A、B两个数据通道进行传输。当写信号sd_wr有效,提取的Y分量数据开始写入SDRAM中,当读信号sd_rd有效时,同时将A、B两个数据通道打开;此时A数据通道传输的数据是第n+m帧图像数据的Y分量,而B数据通道的数据却是第n帧图像数据的Y分量。A、B两通道的数据同时传入“数据做差比较器”中进行差分运算,即能得出视频中第n+m帧图像的像素点与第n帧图像的像素点的差分结果。若差分结果的绝对值大于预先设定的阈值t(t值取25),则判定此像素点发生较大的变化,为运动目标区域的像素点。设计流程如图6所示[6]。

4 系统试验结果与分析

利用帧间差分算法对运动目标检测后,为完善检测效果,需要进行“阈值分割”处理,而这个“阈值”需要根据具体实验测试环境提前设定。选用与最终实验测试摄像头采集的视频环境类似的一段视频进行软件仿真,分别选用“阈值”为10、20、25、30、40、50进行仿真分析,结果如图7所示。

从图7中可以看出,当“阈值”小于25时,出现了很多误判,导致检测效果不理想;当“阈值”大于25时,虽然干扰像素点减少,但检测出的运动目标出现了“空洞”,“阈值”越大,“空洞”越大。因此,“阈值”选定为25。

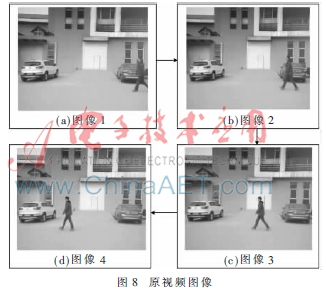

搭建实验平台对系统进行测试,显示屏显示的原视频图像的其中4帧图像如8所示;经过硬件电路端处理以后的视频图像的其中4帧图像如图9所示。

分析以上实验结果,不难发现,图9(a)和图9(b)所示的检测结果出现了较多的“空洞”,因为在这两个时间段,运动中的人经过一辆与背景颜色相近的汽车前面,在检测时,把运动目标上的部分像素点误认为是背景图像,故出现了“空洞”;图9(c)所示的检测效果更好,因为这段时间运动目标颜色与所处背景颜色差异较大,在进行帧间差分检测时,运动目标能更好地从背景中分割出来;图9(d)所示的检测结果中,运动中的人脸部位出现了空洞,因为此时人脸肤色与目标所处的背景颜色接近。

5 结论

本文设计了一种基于FPGA的运动目标检测系统,以FPGA为控制核心和算法实现单元,加上外围的采集和显示电路,可以实时地检测运动目标并显示。在军事公安、工业生产、生物医学等各个领域都有广泛的应用前景。

参考文献

[1] 郭浩.基于FPGA的运动目标检测系统设计与实现[D].武汉:武汉理工大学,2013.

[2] 刘攀.车辆目标检测和跟踪技术研究[D].太原:中北大学,2011.

[3] 王瑾琦.复杂背景下运动目标检测与跟踪方法研究[D].太原:中北大学,2012.

[4] 高美凤,刘娣.分块帧差和背景相融合的运动目标检测[J].计算机应用研究,2013,30(1):299-302.

[5] 程晓东,郑为民,唐志敏.基于DDR SDRAM控制器时序分析的模型[J].计算机工程,2005,31(17):182-184.

[6] 田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2012.