张良,葛荣骏,张志钊,马义德

(兰州大学 电路与系统研究所,甘肃兰州 730000 )

摘要:介绍了一款以FPGA和NIOS系统为核心设计的智能电子测试仪器。该仪器主要围绕友晶公司的Altera DE270开发板进行开发,借助直接数字频率合成(DDS)技术与FPGA芯片的可编程、易修改的特性,实现了正弦波、余弦波、三角波、方波、锯齿波5种基础波形与AM、FM、2ASK、2PSK 4种调制信号的输出,并且在LCD液晶屏上实时显示输出波形。此外,对于外部反馈信号,系统利用NiosⅡ嵌入式微处理器对信号做进一步的处理,例如波形的幅度变换、频率测量、电压测量和幅频特性分析等。该智能电子测试仪器实现了波形发生器、数字示波器、扫频仪、频率计、电压表等多种仪器在功能上的综合,是智能仪器仪表设计的一次全新的尝试。

关键词:FPGA;NiosⅡ;智能仪器;波形发生器

0引言

随着社会科技水平的不断发展,越来越多的企业、学校和个人都参与到电子产品设计与制作的工作中来,而电子测量仪器是从事电子设计工作时必不可少的工具,因此,对电子测量仪的研究也一直是电子设计领域的热门话题[14]。

目前,国内外对于电子测量仪器的研究已经非常成熟,以泰克、安捷伦、惠普为首的公司也推出了很多高性能的电子测量仪器。然而,这些仪器虽然性能出众,但是价格十分昂贵且性能单一,人们从事电子设计时往往需要配备多台仪器,这无疑极大地增加了电子产品的设计成本。同时,许多公司在设计电子测量仪器时为了追求单一设计指标的高性能,使用大量价格昂贵、体积庞大的模拟电路,造成许多仪器体积庞大且操作不智能,这也增加了从事电子设计的学习负担。

基于以上背景,本文设计了一款基于FPGA和NIOS系统的智能电子测试仪器。本仪器综合了波形发生器、数字存储示波器、扫频仪、频率计、电压表等多种仪器的功能,在功能上涵盖了电路设计所需的输入信号激励和输出信号处理,能够独立完成一些复杂实验,简化了操作步骤,降低了实验成本,为智能仪器设计提供了一个全新的思路。

1系统的功能描述

本文以友晶公司设计的DE2开发平台为核心,结合FPGA内嵌NiosⅡ微处理器设计了一款智能电子测试仪器。本仪器具备以下功能:

(1)丰富的波形输出功能

本系统能够输出正弦波、余弦波、三角波、方波、锯齿波5种基础波形,以及AM(调幅信号)、FM(调频信号)、2ASK(二进制振幅键控信号)、2PSK(二进制相位键控信号)4种调制波形。同时系统能够接收外部调制信号参与调制。

(2)灵活的扫频输出功能

借助NiosⅡ微处理器强大的控制能力,本系统能够在 10 Hz~10 MHz频率范围内连续输出正弦扫频信号,借助系统的信息处理能力,能够对外部被测网络进行幅频特性分析。其中扫频信号的起始频率、终止频率、频率间隔等参数可预置。

(3)精准的电压和频率测量功能

本系统能够测量1 Hz~10 MHz的频率范围内的周期波形的频率值和电压值。频率测量采用全同步等精度测量技术[67],具有较高的测量精度(优于10-6)。电压测量采用数字峰值检波技术[8],具有较高的测量稳定性,避免了复杂的模拟电路带来的不稳定性和飘移带来的测量精度不高的影响。

(4)智能的输入波形输出波形显示功能

本系统不仅能够在LCD液晶屏上实时显示输出信号的波形、频率等信息,借助信号反馈网络,同时能够显示被测信号的波形、频率、幅度等信息。这样的设计方便人们在从事电子设计时能够同时观察输入端和输出端的波形、频率、幅度等参数的变化。

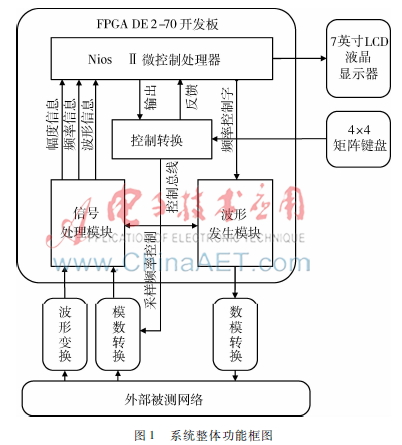

根据以上对仪器功能的分析,本仪器的系统整体功能框图如图1所示。

2系统的结构设计

通过对智能电子测试仪器的具体功能进行分析,将整个系统划分成3个子系统,分别为信号激励子系统、反馈处理子系统和嵌入式微控制子系统。

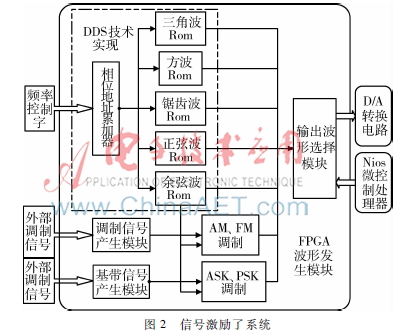

2.1信号激励子系统

信号激励子系统的工作流程如图2所示。首先,子系统接收来自微控制子系统的频率控制字,借助直接数字频率合成技术(DDS技术)[1]在FPGA内部通过Verilog硬件逻辑语言产生正弦波、余弦波、三角波、方波、锯齿波5种基础波形[7]。然后以余弦波为载波,以正弦波为调制信号或通过调制信号产生模块接收外部输入的调制信号,借助相关算法产生AM和FM两种调制波形。同时以方波为基带信号或通过基带信号产生模块接收外部输入的基带信号,借助相关算法产生ASK和FSK两种编码信号。最后通过输出波形选择模块来输出这些激励信号[8]。

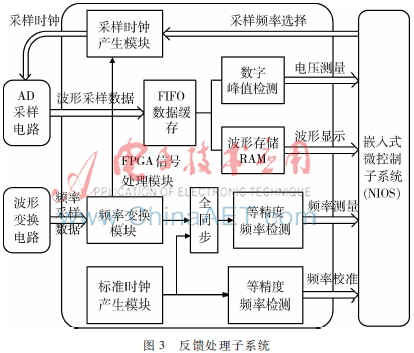

2.2反馈处理子系统

反馈处理子系统的工作流程如图3所示。在嵌入式微控制子系统的控制下,采样时钟模块首先产生一个预置的采样时钟,控制AD采样电路的采样速率。然后系统将反馈信号的波形数据通过FIFO缓存读取到FPGA中,再分别对其进行数字峰值检波和波形存储,将处理结果发送到NiosⅡ微处理器中,实现波形的存储显示和电压测量功能。

波形变换电路首先将具有周期性质的反馈信号变换成同频率的方波信号并将其输入到频率变换模块,通过控制采样时钟产生模块,使其产生的采样信号为被测信号的整数倍,这样使得不同频率的信号在液晶上可以显示相同的周期数。最后,采用全同步的等精度测频法对变换后的方波信号进行测频。此外,采用一个标准时钟信号进行频率校准,最终实现频率测量功能。

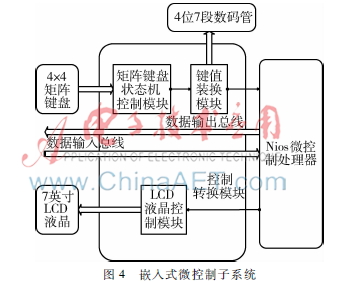

2.3嵌入式微控制子系统

嵌入式微控制子系统的工作流程图如图4所示。子系统的主要功能是通过矩阵键盘输入人机交互信息,再通过数据输入和输出总线控制其他子系统,最终在7英寸LCD液晶上进行数据显示。

通过对智能电子测试仪器的系统结构进行分析,明确了整个系统的硬件设计目标。其中信号激励子系统的波形发生模块、反馈处理子系统的信号处理模块和嵌入式微控制子系统的控制转换模块均采用基于Verilog的FPGA硬件逻辑语言实现。最终FPGA硬件设计的RTL视图如图5所示。

3系统的软件设计

嵌入式微控制子系统的核心是来自FPGA内部的NiosⅡ微控制处理器。整个NiosⅡ微控制处理器的软件工作流程如图6所示。

首先,NiosⅡ接收来自矩阵键盘的输入控制信息,这些控制信息包括:系统的波形输出模式、正弦波扫频的扫描频率间隔及中断控制、基础波形输出的波形类型和输出频率、调制信号的产生方式和调制度、基带信号的产生方式、AD采样时钟频率和LCD液晶显示界面的的波形显示模式等信息。然后,NiosⅡ将这些控制信息通过输出数据总线发送到各个模块,使各模块正常工作。同时,NiosⅡ也通过输入数据总线接收各个模块的反馈信息,这些信息包括:输出端的波形信息、采样时钟的频率、输入信号的波形、电压最大值和最小值和频率信息。最终,NiosⅡ微控制处理器将这些信息显示在外接的7英寸LCD液晶显示器上。

4系统的测试与分析

本文设计的基于FPGA和Nios系统设计的智能电子测试仪器的实际工作效果如图7所示。

为了检测智能电子测试仪器系统波形输出功能的稳定性和测量功能的准确性,借助一台由泰克公司生产的数字示波器(型号:Tektronix TDS 2022B)来对其进行测试。

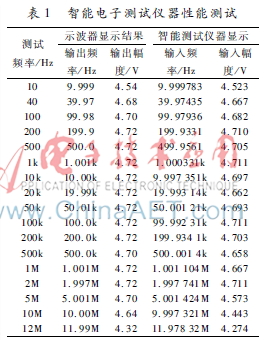

表1是以正弦波为代表,借助示波器检测本仪器输出信号的频率和幅度的稳定性与输入信号频率和幅度测量的准确性的部分测量结果。

测量结果表明,本仪器采用全同步的等精度频率测量技术,频率的有效测量范围与测量精度相较于传统仪器有较大的提高。波形输出的3 dB带宽为1 Hz~22 MHz,波形在100 Hz~10 MHz

的输出频率范围内,具有良好的幅度稳定性。相较于传统的二极管峰值检波幅度测量方式,本仪器采用数字峰值检波的幅度测量方式,具有较高的测量精度与稳定性。

5结论

本系统外围电路简单、体积小巧、操作方便,各种功能采用模块化思路集成在一起,可以根据用户需求随意增减功能模块,也能根据不同设计需求改变各功能模块的技术指标,与传统电子仪器相比更加智能和灵活。

系统注重多种功能的综合,减少了实验所需的仪器数量,降低了实验成本,非常适合于没有足够成本建立大型实验室且对于性能指标没有极高追求的中小型企业和个人,以及刚刚接触电子设计的高校学生。图6NIOS微控制子处理器软件工作流程图图7智能电子测试仪器实验效果图

参考文献

[1] 赵茂泰.智能仪器原理及应用(第3版)[M].北京:电子工业出版社,2009.

[2] 陈尚松.电子测量与仪器(第2版)[M].北京:电子工业出版社,2007.

[3] 王媛媛.基于FPGA的数字秒表设计与实现[J].微型机与应用,2014,33(5):23-26.

[4] 吴征,苏淑靖.基于FPGA+PWM的多路信号发生器设计[J].电子技术应用,2014,40(3):38-40,44.

[5] 张志刚.FPGA与SOPC设计教程—DE2实践[M].西安:西安电子科技大学出版社,2007.

[6] 刘德亮,王竹林,尉广军.基于FPGA高精度频率测量仪的设计[J].河北工业科技,2010(1): 29-31.

[7] 包本刚.基于FPGA的全同步数字频率计的设计[D].长沙:湖南大学,2007.

[8] 石明江,顾亚雄,何道青.基于FPGA的手持式数字存储示波器峰值采样技术[J].仪器仪表,2009(4):6-8.