潘滨,周昕杰,罗静

(中国电子科技集团公司第五十八研究所, 江苏 无锡 214062)

摘要:研究设计了一种多节点的1553B总线协议处理器,可以模拟整套1553B总线系统,既可以作为测试设备,也可作为总线上的多个节点在实际应用中使用。针对总线协议处理器逻辑与存储资源占用高、难以单片实现的问题,提出了多核MIMD架构的实现思路,有效地降低了逻辑资源的使用量,使其可以在单片FPGA上实现。基于软硬件融合的理念,通过自定义专用指令集增加指令并行度来提高指令执行的效率,增强了系统的实时性,使其可以在低频时钟下运行,从而降低了系统的功耗。

关键词:1553B总线;多核;MIMD;FPGA

0引言

1553B总线是一种广泛应用的军用总线,它具有异步操作、时钟自对准、数据传输可靠性高等优点[1]。目前,国内科研院所已经完成了总线协议处理器的国产化,成功研制了多款单节点总线协议处理器。但在用于部分特殊应用和总线测试系统的多节点协议处理器方面,国内尚未有相关的研究文献。这一方面由于相比单节点处理器,多节点处理器需求量不大;另一方面由于多节点处理器需要的逻辑与存储资源远高于单节点处理器,实现难度很大,国外同类产品也多是以较大规模的板卡形式实现,而未能将其集成到单片中[2]。

随着集成电路国产化的范围日益扩大,研制一种单片/单板实现的多节点协议处理器是必然要求。本文将以一种多核MIMD(多指令多数据)的架构在单片FPGA上实现多节点总线协议处理器,这一设计思路也可以转换到ASIC设计上。

1总体思路

研究以DDC公司的BU61580型总线协议处理器作为参考范本,功能上实现1个总线控制器、31个总线终端、1个总线监视器。设计为在外部接口时序上与BU61580兼容,以方便现有软件的移植。

1553B总线协议处理器可以分为逻辑和存储两大核心部分[3]。1553B总线的设计紧贴应用,功能繁杂,逻辑资源使用量较大。同时,总线上每个节点至少4 K字的存储容量需要大量的存储资源。若采用单节点协议处理器复制32份的方式来实现,势必耗费大量资源。这就要求设计一种高效简洁的架构,最大程度地复用相似逻辑来减少资源占用。

通过分析总线的事务和总线各节点的行为模型,发现这样两个特性:(1)相比于协议处理器的速度,总线上的数据传输速率是很慢的,即使依次处理各节点,也不会影响总线事务的正常运行;(2)不同的节点,在对总线事务的处理上,处理的过程基本是相同的,区别仅在于配置寄存器的不同配置值而产生的细小差异。若采用微控制器来执行指令实现总线上的事务处理功能,就可以复用大部分的逻辑资源,而对于每个节点的不同配置而产生的细节差异,可以用SFR(特殊功能寄存器)的方式实现[4]。这样,既达到了压缩逻辑规模的目的,又保证了不同节点独立配置的能力。

2架构设计

在架构设计中,重点关注简洁性和实时性。简洁的架构能够减少资源的使用量,提高代码的可维护性。实时性能够尽可能高效快速地完成总线事务,从而实现更高的性能。

2.1MIMD指令集设计

首先考虑微控制器核的指令集的设计。将原本并行运行的硬逻辑功能改为串行执行的指令,一个重要的问题就是保证系统的实时性。

一种思路是采用常规指令集并使用流水线实现微控制器,这样在一个周期内能够执行更多的指令。但这只是提高了指令执行的速度,并不能改变串行的本质,而且在协议处理器中,微控制器不应该是最复杂的部分,调试工作的重点应该放在与协议密切相关的具体功能模块上,流水线的控制逻辑复杂,容易引入bug干扰其他模块的调试,这会给设计工作带来很大不便。

另一个思路是采用MIMD(多指令多数据)架构。在每个周期内,同时执行多条指令,处理多个数据,这是在事务层面的并行化,通过分配指令位域,在一条指令中实现多个不同的功能,可以大大提高指令执行的效率,增强系统的性能。

将32 bit宽度的指令分为4个位域,分别是通用指令INS、特殊功能寄存器指令SFRINS、扩展指令EXT和条件判断码COND。通用指令是微控制器的指令,完成总线事务的基本操作;特殊功能寄存器指令针对总线协议处理器中的寄存器设计,实现与总线事务处理流程无关但与处理细节相关的功能;扩展指令用于实现地址的重映射和设备的选择;将需要多步逻辑运算才能得到结果的条件判断通过硬逻辑实现,供程序根据条件是否成立来选择是否执行该条指令。图1给出了指令编码的位域定义。

根据编码原则,定制了一套专用指令集,能够最好地适用于总线事务的处理。这套指令集可以在一个周期内实现常规指令多个周期才能完成的功能,大大地提高了实时性。为便于软件设计与调试,使用Perl语言编写了该指令集的汇编器。

2.2硬件模块运行机制

硬件采用Verilog HDL设计实现,在设计中注重了代码的模块化和可升级化。秉承高内聚、低耦合的原则,将可以独立出来的功能都尽可能独立设计为一个模块,这样既有益于设计过程中的调试,也方便日后的维护与升级。图2展示了多节点总线协议控制器的基本架构框图。

控制器由BC_ACE、RT_ACE、BM_ACE、BUS_INTF和CTRL_INTF共五个模块组成。BC_ACE、RT_ACE、BM_ACE分别实现BC(总线控制器)、RT(远程终端)、BM(总线监视器)的功能,BUS_INTF实现了三个协议处理模块与1553B总线之间的接口,CTRL_INTF实现了多节点总线协议控制器和上位机之间的接口。

下面详细介绍各模块的运行机制。

BC_ACE包含微控制器、指令存储器、通用寄存器、特殊功能寄存器组和数据存储器。微控制器从指令存储器中读取指令并执行,完成SFR的配置与更新、数据存储器的访问等任务。同时,微控制器将SFRINS发送到特殊功能寄存器组中,由SFR内部逻辑完成总线数据收发和部分寄存器值的更新。

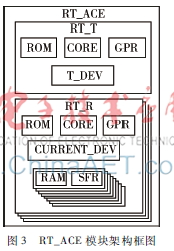

RT_ACE包含四个RT_R模块和一个RT_T模块,RT_R模块负责响应接收指令,RT_T模块负责响应发送指令。RT_ACE模块的功能框图如图3所示。

RT_T模块包含微控制器、通用寄存器和指令存储器。模块中定义了T_DEV信号来选择发送的RT设备,指向对应的SFR和数据存储器。当接收到RT发送命令时,微控制器使用扩展指令选定发送RT,然后使用其SFR和数据存储器完成发送操作;当接收到RT接收命令时,RT_T模块不工作。

RT_R模块包含微控制器、通用寄存器、指令存储器、8组特殊功能寄存器和8组数据存储器,每个RT_R模块可以实现8个RT,4个RT_R模块可以实现32个RT(仅出现在禁用广播命令的情况下)。模块中定义了CURRENT_DEV信号来选择当前的设备,指向对应的SFR和数据存储器。在接收到非广播接收命令时,微控制器使用扩展指令选择命令字指定的RT;在接收到广播接收命令时,首先选择第1个可用RT,在该RT处理完毕后,使用扩展指令选择下一个可用的RT继续处理,直到全部可用RT处理完毕。在接收到发送命令时,RT_R模块不工作。

BM_ACE包含微控制器、指令存储器、通用寄存器、特殊功能寄存器和数据存储器。其运行机制类似于BC_ACE模块,这里不再赘述。

BUS_INTF作为收发器,是各总线终端与总线之间的接口,用来完成Manchester码的编解码和码字正确性检测工作。它包含一个32×16 bit的发送缓存、一个编码器、两套解码器和一个编解码状态监视器。发送缓存暂存各处理器请求发送的数据,编码器完成Manchester码的生成,两套解码器分别负责A/B通道的解码,状态监视器实现总线状态的检测和loopback(环回自测)功能。

CTRL_INTF实现了上位机和协议控制器之间的通信功能。上位机通过板上的USB协议处理芯片与CTRL_INTF模块的通信来配置协议控制器中各个节点,并且可以在协议控制器工作过程中读写各节点的SFR和存储器数据。

2.3软件设计

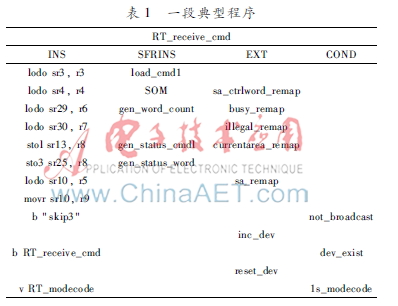

软件设计是本设计中较为重要的部分,它直接影响到功能的正确性和运行的实时性。设计中共有4段程序,分别是BC、RT_R、RT_T和BM的程序。出于效率的考虑,程序尽可能实现并行化操作,充分发挥MIMD的优势,让图5仿真测试典型波形指令的每一个码域都能在指令中充分应用,从而最高效地完成所需要的功能。表1给出了一段典型的程序,可以看出,一条指令中有多个域,可以分别实现不同的功能,共同完成RT处理接收命令的过程。

3仿真验证与综合

3.1仿真

采用VCS作为仿真工具进行仿真,为提高仿真效率,使用System Verilog搭建了测试平台。测试平台使用随机种子带约束地随机产生一定数量的总线事务,根据事务内容,通过CTRL_INTF模块来配置初始化各总线终端,完成总线系统的初始化,随后启动总线进入工作状态。在总线事务启动后,测试平台的结果比较器开始监测总线事务,并使用内建mailbox对比DUT的结果和预期的结果,从而判断各终端的功能是否正确[5]。图4显示了测试平台的架构。

经过大量的测试验证,结果表明设计满足1553B总线标准的要求,能够模拟整套1553B总线系统。

图5显示了仿真中BC到RT的广播数据传输过程。BC运行指令将消息发送到总线上,RT协议处理器接收到命令后依次选择各RT节点处理该消息。

3.2综合

目标FPGA是Altera的EP3C80F474C8,这款FPGA存储资源充裕但性能并不高。这样选型主要是因为多节点协议处理器需要33×4K×16 bit的存储资源(1个BC,31个RT,1个BM),而采用的多核MIMD架构对速度和逻辑资源的要求不高,因此出于成本方面的考虑,选择了这样一款器件[6]。设计使用的时钟频率为16 MHz,在Quartus II 13.0中综合结果如图6所示。

图6综合报告实验表明,在该型号的FPGA上复制32份单节点协议处理器实现多节点处理器,所需的逻辑资源超出FPGA所能提供资源的一倍以上。从综合报告中可以看出,采用多核MIMD系统大大降低了逻辑资源的占用,逻辑资源仅使用了可用资源的70%左右,在FPGA中仍有可观的剩余逻辑资源。

4结论

研究提出了一种采用多核MIMD架构实现多节点1553B总线协议处理器的方法,功能符合1553B总线标准的要求,并特别注意了逻辑资源的节约与复用,使设计逻辑规模可以在单片FPGA中实现。在后续的工作中,将进一步优化设计,并开发测试板和PC上的测试应用软件[7],使整个系统作为完整的产品提供给用户使用。

参考文献

[1] 董大伟,周宇江,郭楹. 军用总线发展趋势研究[J]. 电子技术应用,2015,41(7):710.

[2] Alta Data Technologies. MultiChannel 1553 Interface for PCI Systems[R]. 2011.

[3] Data Device Corporation. AceXtreme 1553/429 USB Avionics Device[R]. 2010.

[4] Data Device Corporation. ACE/MINIACE Series BC/RT/MT Intergrated 1553 Terminal User’s Guide[R]. 2010.

[5] Data Device Corporation. MILSTD1553 Designer’s Guide Sixth Edition[R]. 2003.

[6] 张春,麦宋平,赵益新. System Verilog验证测试平台编写指南[M].北京:科学出版社, 2009.

[7] 黄正,王健军,刘士全,严华鑫. 基于NIOS II的1553B总线测试系统设计[J]. 微型机与应用, 2015,34(18):98100.