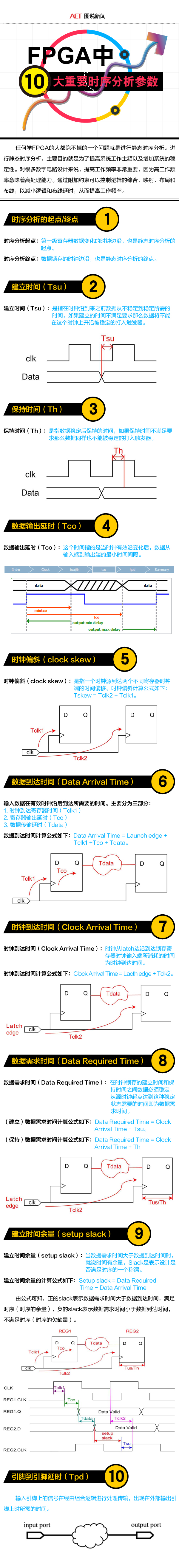

FPGA中10大重要时序分析参数

2016-12-02

关键词:

图说新闻

补充

静态时序分析(STA)是采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。它不需要输入向量就能穷尽所有的路径,且运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计,因此静态时序分析已经越来越多地被用到数字集成电路设计的验证中。

静态时序分析可以在逻辑综合、布局布线等步骤后进行,FPGA EDA工具在布局布线完成后给出STA结果,这时的分析结果是最接近实际电路情况的,而逻辑综合时的分析结果是看不到的,也是不准确的(因为没有物理信息,所以只用于指导布局)。如果是用ASIC综合工具(比如DC),两个阶段的STA结果都可以看。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。