外媒:IBM 2纳米芯片被虚标了!台积电都快量产了!

2021-05-13

来源: EETOP

前几天IBM宣布开发出了世界上首款2纳米芯片。此消息一出,立马全网刷屏。

那么IBM 2纳米芯片真的“货真价实”么?带着疑问,国外知名科技媒体semiwiki做了详细的数据分析,最后的结论是IBM的2纳米芯片更接近于台积电的3纳米!

semiwiki的分析原文如下:

作者:Scotten Jones

IBM公告中指出这款2纳米芯片具有以下的特征:

在这里IBM的2nm制程号称在150mm2(指甲盖大小)的面积中塞入了500亿个晶体管,平均每平方毫米为3.3亿个。

栅极长度为12nm的44nm接触式多节距(CPP)。

基于IBM正在使用水平纳米片(HNS)的横截面,可以使用Gate All Around(GAA)进行GAA的几种方法。

HNS叠层构建在氧化物层之上。

与最先进的7nm芯片相比,性能提高了45%或功耗降低了75%。

EUV图案用于前端,允许HNS片的宽度在15纳米到70纳米之间变化。这对于调整电路的各个区域以实现低功耗或高性能以及SRAM单元是非常有用的。

这些薄片的厚度为5纳米,三层堆叠。

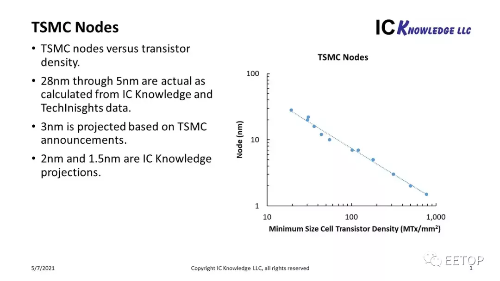

如IBM所说,这真的是“ 2nm”吗?台积电是目前生产工艺技术的领导者。我们绘制了TSMC节点名称与晶体管密度的关系图,并拟合了0.99 R2值的曲线,见图1。

图1. TSMC等效节点

使用曲线拟合,我们可以将晶体管密度转换为台积电等效节点(TEN)。使用曲线拟合,对于IBM宣布的333MTx / mm 2,我们得到2.9nm的台积电等效节点。因此,我们认为,IBM的这款2纳米芯片,严格来说应该是3nm节点,而不是2nm节点。

为了更详细地将IBM公告与之前宣布的3nm工艺和预计的2nm工艺进行比较,我们需要进行一些估算。

从公告中我们知道CPP为44nm。

我们假设一个单扩散中断(SDB),这将导致最密集的工艺。

查看公告中的横截面,我们没有看到埋入式电源轨(BPR),BPR是将HNS轨道高度降低到5.0所必需的,所以我们假设该工艺为6.0。

为了达到333MTx / mm 2,最小金属间距必须为18nm,这是一个非常具有挑战性的值,可能需要EUV多重曝光。

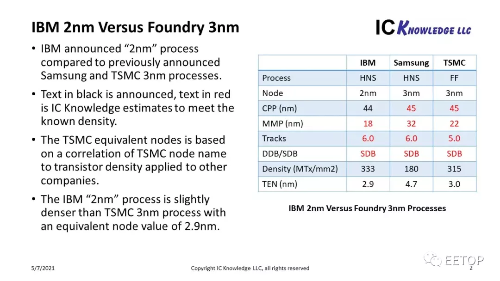

IBM 2nm对比代工厂的3nm

图2将IBM 2nm设计与我们对三星和台积电3nm工艺的估计进行了比较。我们知道三星也在制造HNS,而台积电则选择了3nm的FinFET。三星和台积电都宣布了其3纳米工艺相对于5纳米工艺的密度改进,因此我们可以知道这三家公司的晶体管密度,并可以计算出这三家公司对应的TEN(台积电等效节点)。如前所述,IBM的TEN是2.9,而三星的TEN是4.7,台积电的TEN是3.0,这再次证明了IBM 2纳米工艺与台积电3纳米工艺相当,而三星得3纳米则落后于台积电。

图2中红色的数字是为实现公布的密度而估计的,我们假设所有公司都是SDB。台积电的轨道高度最小,因为FinFET在没有BPR的情况下可以有5.0的轨道高度,但HNS需要BPR来达到5.0,而BPR还没有准备好。

图2. IBM 2nm与代工厂的3nm。

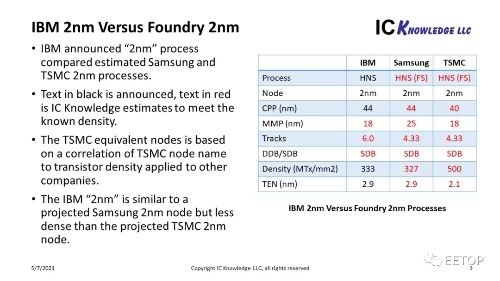

IBM 2nm对比代工厂的 2nm

我们还在图3中预测了三星和台积电的2纳米工艺。我们预测这两家公司都将使用BPR(BPR目前还没有准备好,但当三星和台积电在2023/2024年左右推出2纳米工艺时可能会就绪)。我们还假设三星和台积电将利用NHS(HNS(FS))架构来达到4.33轨道高度,放宽一些其他收缩要求。然后我们根据公司最近的收缩趋势预测出CPP和MMP。

图3. IBM 2nm与Foundry 2nm。

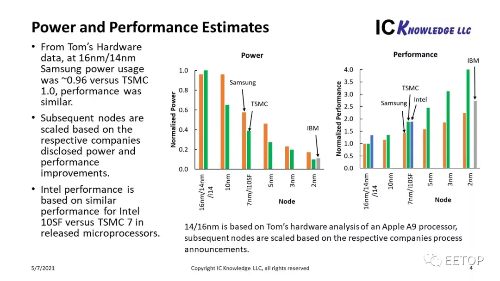

功耗与性能

在今年的ISS上,我估计了三星(Samsung)和台积电(TSMC)的相对功率和性能,并提供了一些额外的英特尔性能数据。各节点的缩小趋势是基于各公司公布的功率和性能估计以及14nm/16nm的可用比较。欲了解更多信息,请参见ISS的文章。(https://semiwiki.com/events/294639-iss-2021-scotten-w-jones-logic-leadership-in-the-ppac-era/)

由于IBM将其功率和性能改进与领先的7nm性能进行了比较,因此我可以将IBM的功率和性能放在我先前介绍的相同趋势图上,见图4。

图4.功率和性能(估计值)

IBM对HNS的使用大大降低了功率,使他们的2纳米工艺比三星或台积电的3纳米工艺更省电,尽管我们相信一旦台积电在2纳米工艺中采用HNS,他们的功率将和IBM一样好甚至更好。就性能而言,我们估计台积电的3纳米工艺的性能将超过IBM的2纳米工艺。

正如ISS文章中讨论的那样,这些趋势仅是估计值,并基于许多假设,但这是我们可以汇总的最佳预测。

结论

在分析了IBM的公告后,我们认为他们的 “2纳米 ”工艺从密度角度看更像台积电的3纳米工艺,功耗更佳,但性能更差。IBM的公告令人印象深刻,目前这还仅仅还属于实验室阶段,与台积电的3纳米工艺相比,只有在功耗方面有明显的优势,而台积电3纳米工艺将在今年晚些时候进入风险启动阶段,并在明年投产。

我们进一步相信,当台积电工艺在2023/2024左右投入生产时,它将在2nm的密度、功率和性能方面保持领导地位。