基于最佳接收的UART的设计与实现

2008-05-16

作者:何健标,王宏远,林静宜,李众奇

摘 要: 针对通用异步接收和发送器" title="发送器">发送器UART对随机脉冲干扰特别敏感的弱点,引入数字相关器" title="相关器">相关器,以实现信号的最佳接收及提高UART的抗干扰性能;结合现场可编程逻辑门阵列FPGA的结构特点针对同步模块和数字相关器等关键部件进行逻辑设计" title="逻辑设计">逻辑设计优化,使UART性能大为提高。

关键词: UART 最佳接收 数字相关器 FPGA

在嵌入式系统设计中常使用通用异步接收和发送器UART(Universal Asynchronous Receiver/Transmitter)实现系统控制信息或低速数据信息的传输,而UART所采用的奇偶校验方式不具备前向纠错能力,检错能力也有限,所以在设计UART时要尽可能提高其抗干扰能力,以加强系统的可靠性。

1 基于最佳接收的UART

目前UART中的接收器多采用如图1所示的设计。

同步模块的作用是检测异步串口的同步位(Sync位)并提取抽样判决需要的采样信号,使抽样判决模块尽量在输入信号" title="输入信号">输入信号RXD的码元中部对信号采样(如图2)。因为信号在码元边沿跳变时会有振铃或过冲等抖动,所以码元的边沿部分不适合采样。要想获得较佳的抽样判决效果,最好在靠近码元中部的位置对接收到的信号进行抽样判决。

这种在码元中部进行抽样判决的接收方法可以有效去除振铃、过冲等信号的边沿抖动带来的影响,但无法解决随机脉冲干扰带来的问题。如图3所示,随机脉冲干扰可能在任何时刻出现。即使同步模块工作正常,使得抽样判决总处在码元中部的最佳采样时刻,也有可能由于随机脉冲干扰造成判决错误。

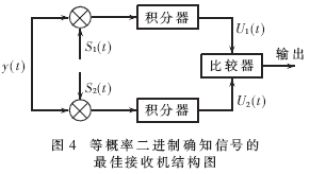

为了尽可能地减弱随机干扰及其他干扰给信号接收带来的影响,引入最佳接收机结构来设计UART的接收器,以实现信号的最佳接收。等概率二进制确知信号(异步串口通信的信号即属于此情况)的最佳接收机结构如图4所示。

图4中的乘法器和积分器实质上构成了一个相关器,因此上述结构又称为相关器形式的最佳接收机。其中相关器的输出u(t)由下式定义:

其中:T为采样周期,N表示一个码元的时间包含N个采样周期。

U1(kT)和U2(kT)由上式计算可得,然后送到比较器在最佳判决时刻(t=kNT)进行比较,若U1(kT)≥U2(kT),则判决为逻辑1,否则判决为逻辑0。

UART接收器接收的信号是未经调制的二进制基带信号,码元波形不是高电平" title="高电平">高电平就是低电平,两种码元的波形截然不同。因此,如果输入信号Y(nT)与S1(kT)相关运算的结果较大,则Y(nT)与S2(kT)相关运算的结果就很小;反之亦然。所以可以将上述最佳接收机结构中S2(kT)这一路相关器省略,只保留一路相关器。最后的比较器改成判决器,判决准则是:如果相关器在最佳判决时刻(t=kNT)的输出大于某个阈值,则判决为逻辑1;否则判决为逻辑0。经过简化改进基于最佳接收机结构的UART接收器的框图如图5所示。

下面以一个简单示例证明基于最佳接收的UART接收器可以有效地去除随机干扰给信号接收带来的影响。如图6所示,在这个码元周期内,如果采用一次抽样判决,则即使处于一次抽样判决的最佳采样时刻,也会由于随机脉冲干扰而产生误判;如果引入数字相关器在最佳判决时刻进行判决,则尽管由于信号边沿的抖动和随机脉冲的干扰,信号的波形遭到了破坏,但信号在码元周期内相关运算的结果为7,大于阈值5,接收器依然能正确地判定接收到的信号为逻辑1。这将有效抑制随机干扰给信号接收带来的影响。

2 基于FPGA的UART设计优化

数字相关器的引入,极大地提高了UART接收器的抗干扰性能,但也带来了两个问题:

(1)在数字相关器输出相关运算的结果后,判决器需要在最佳判决时刻进行判决,因为此时与信号的相关输出最大。同步模块得到的判决信号与这个最佳判决时刻的偏移越大,UART接收器的性能就越差。也就是说,数字相关器对同步模块的判决信号有很高的精确度要求。

(2)数字相关器是一个运算量相当大的复杂逻辑器件。

以上两个问题使得UART接收器的逻辑结构非常庞大,并将耗用很大的逻辑资源。而在大多数嵌入式系统应用中,UART通常只是控制信息的一个接口,如果设计出来的UART的IP本身就占用了大量的逻辑资源,则使用者肯定不能接受,且这样的UART的IP核也毫无价值。所以,要使得这种高性能的UART能在实际工程中应用,就必须优化UART的逻辑设计,减少耗用的资源。下面将以现场可编程逻辑门阵列FPGA(Field Programmable Gate Array)为设计平台,根据UART接收器中同步模块和数字相关器的结构特点以及FPGA的结构特点,对逻辑设计进行优化。

2.1 同步模块的设计优化

UART的同步模块主要检测Sync位并得到判决信号。理想情况下,如果在一个码元内有N次采样,则当N次采样的结果都为0时,表明检测到一个Sync位,而且此时就是数字相关器的最佳判决时刻(如图7)。可是由于信号的边沿抖动或是随机脉冲干扰,N次采样的结果通常无法达到同时为0的理想情况,如果以N作为检测同步的门限,则可能检测不到Sync位,造成漏同步。

为了保证接收器能抵御一定程度的干扰而进行正确的同步,检测同步的门限不能取N。假定同步检测的门限定为(N-3),则会出现这样的问题:如果接收到的信号波形良好,而又采用(N-3)作为检测同步门限,则同步模块得到的判决信号实际上偏离了数字相关器的最佳判决时刻,使判决器误判的可能性增加。较好的解决办法是增大单个码元周期内的采样次数N,使同步检测门限(N-3)与判决器判决门限N/2有较大距离,从而使后端的判决器有更好的抗干扰性能。根据实际测试的经验,取N为16,以13作为同步检测门限,以8作为判决门限。这样既能有效防止因干扰而造成的漏同步,又能保证后端的数据判决有较好的抗干扰性能。

由上所述,同步模块实际上是对接收到的16个采样值进行译码,当有13个0时表示检测到同步,并将此时得到的判决信号提供给后端的判决器进行数据判决。在物理上这就是一个16输入的组合电路。由于FPGA有丰富的时序逻辑资源而缺乏组合逻辑资源,因此该电路模块若是在FPGA上实现要耗用大量的逻辑资源,所以需要对该模块的逻辑设计进行优化。

逻辑优化的原则是充分利用FPGA逻辑资源丰富的特点,以相同功能的时序电路替代这个庞大的组合电路。如图8所示,输入信号RXD经过D触发器采样并经过一个反相器后做为使能信号送给下一级的模13计数器(即对D触发器采样得到的低电平计数),这样就可以用时序统计逻辑来替代原来的组合统计逻辑。对FPGA,这样的时序电路只需要耗用少数几个D触发器,可以极大地节省资源。然而时序统计逻辑可能会由于对随机脉冲干扰带来的反常低电平的采样积累而产生误同步,所以需要同时对输入信号RXD经过D触发器的采样得到的高电平进行计数。若得到连续多个不同长度(图7中长度为8)的高电平,则说明正在接收的不是Sync位,即使采样得到了低电平,也是干扰信号,这时就要对模13计数器复位,以防止干扰(低电平的干扰)的累积产生误同步。

2.2 数字相关器的设计优化

数字相关器的数学表达式为:

这时乘法器实际上是不需要的,数字相关器的输出是最近的N(N=16)个输入采样(即输入信号RXD的采样)的叠加。输入信号RXD的采样是1比特量化,其值为逻辑1(高电平),或逻辑0(低电平)。所以对输入采样的叠加可以用计数器实现:逻辑1使计数器计数加1,逻辑0则保持计数器的值不变。这样,复杂的数字相关器就可以用一个计数器实现。

图9为经过逻辑优化的数字相关器和判决器的电路。RXD经过D触发器(一个码元周期采样N=16次)送入数字相关器。该数字相关器在逻辑设计上被优化为一个计数器,对D触发器输出的逻辑1进行统计计数。当同步模块送来判决信号时,判决器根据当时数字相关器的计数结果进行硬判决:计数结果≥8(N/2)即为逻辑1,否则为逻辑0(逻辑上把计数结果的Count[3]和Count[4]作逻辑或运算为抽样判决结果输出)。判决信号同时还要对数字相关器(即计数器)复位,因为这同时是新码元接收周期的开始,使数字相关器重新进行计数叠加。

3 基于FPGA的UART设计实现

UART根据功能划分为波特率控制器、发送器和接收器三个模块。图10是UART的整体设计框图。Out8_RxData[7..0]和Out_RxDateValid是接收器收到数据后输出的数据及其使能信号。而In8_TxData[7..0]和In_TxDataEna是发送器要发送的数据及输入使能信号。校验参数设置包括是否需要校验、奇偶校验等。

3.1 波特率控制器的设计

波特率控制器根据波特率控制参数的设置,为接收器和发送器提供工作使能信号,这种工作使能信号的频率决定了UART工作的波特率。从逻辑设计的角度看,波特率控制器实质上是一个可变模计数器,波特率控制参数调整计数器的模,从而为接收器和发送器提供各种符合通信波特率要求的工作使能信号。

3.2 发送器的设计

发送器在接收到并行发送数据后,将数据进行并串变换,按照波特率控制器提供的工作使能信号的速率,将数据及奇偶校验位(是否发送校验位根据参数设置)逐位发送。发送器在逻辑设计上是一个有限状态机,图11是发送器状态跳转图。

3.3 接收器的设计

接收器的逻辑框图见图5,其中同步模块、数字相关器和判决器已详细介绍。下面介绍数据接收模块。数据接收模块负责将判决器的判决输出逐位接收,然后将接收到的串行位串转换成8位的字节,根据校验的参数进行设置。如果无需校验,则直接输出收到的字节;如果需要校验,则根据设置进行奇偶校验。如果校验显示接收有错误,则直接丢弃接收结果;如果校验无误,将收到的字节输出。数据接收模块在逻辑上也是由一个有限状态机实现,图12是数据接收模块的状态跳转图。

4 综合与测试

UART设计完成后,采用Altera公司的开发软件QuartusII综合实现,器件选用Cyclone系列的FPGA——EP1C12Q240C8。整个UART占用了120个FPGA的逻辑单元(LE,Logic Element)。可以说所耗逻辑资源非常小,而且使用方便,适合工程使用。

为了测试这个UART的IP的工作稳定度,采用串口助手以各种速率不间断发送数据流给UART进行接收测试并回发,在每次长达15分钟的不间断接收并回发数据的测试过程中,UART的通信错误是0。在性能上,比以前设计的UART(基于单次采样而不是基于最佳接收)大为提高,而消耗的逻辑资源基本一致。目前这个基于最佳接收的UART的IP已经在本研究所的FPGA产品中推广,获得一致好评。

参考文献

1 缪众林,丁克忠.带硬件地址识别的UART IP的设计和实现.电子技术应用,2004;30(6)

2 李群芳,黄 建.单片微型计算机与接口技术.北京:电子工业出版社,2001

3 樊昌信.通信原理(第5版).北京:国防工业出版社,2001

4 Bernard Sklar.Digital Commun-ications Fundamentals and Applications(Second Edition).Beijing:Publishing House of Electronics Industry,2002

5 Cyclone_device_handbook.Altera Corp,2003,10