基于边界扫描的多芯粒异构集成系统互连线测试方法

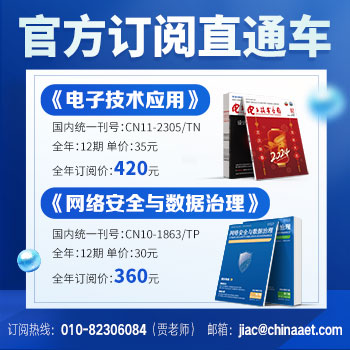

电子技术应用

陈龙,黄健,解维坤,宋国栋

中国电子科技集团公司第五十八研究所

摘要: 针对多芯粒异构复杂结构采用传统的功能测试方案无法准确定位内部互连故障,提出一种基于边界扫描的多芯粒互连线测试方法,实现对芯粒芯片互连故障的检测。基于IEEE 1149.1边界扫描协议与互连线测试优化算法,通过ATE测试系统识别内部互连故障线路,从而准确检测出芯片故障缺陷。与传统测试方法相比,基于边界扫描的多芯粒互连线测试方法稳定可靠,能够精确定位芯片内部互连故障,大幅提高测试效率,保证芯粒系统的可靠性应用。

中图分类号:TN407 文献标志码:A DOI: 10.16157/j.issn.0258-7998.257100

中文引用格式: 陈龙,黄健,解维坤,等. 基于边界扫描的多芯粒异构集成系统互连线测试方法[J]. 电子技术应用,2026,52(3):46-50.

英文引用格式: Chen Long,Huang Jian,Xie Weikun,et al. Interconnect testing method for multi-chiplet heterogeneous integrated systems based on boundary scan[J]. Application of Electronic Technique,2026,52(3):46-50.

中文引用格式: 陈龙,黄健,解维坤,等. 基于边界扫描的多芯粒异构集成系统互连线测试方法[J]. 电子技术应用,2026,52(3):46-50.

英文引用格式: Chen Long,Huang Jian,Xie Weikun,et al. Interconnect testing method for multi-chiplet heterogeneous integrated systems based on boundary scan[J]. Application of Electronic Technique,2026,52(3):46-50.

Interconnect testing method for multi-chiplet heterogeneous integrated systems based on boundary scan

Chen Long,Huang Jian,Xie Weikun,Song Guodong

No.58 Research Institute of China Electronic Technology Group Corporation

Abstract: For multi-chiplet heterogeneous complex structures, traditional functional testing methods are unable to accurately locate internal interconnection faults. A boundary-scan-based interconnect testing method for multi-chiplet is proposed, which enables the detection of interconnect faults between chiplets. Based on the IEEE 1149.1 boundary-scan protocol and an optimized interconnect testing algorithm, this method uses an Automatic Test Equipment (ATE) testing system to identify faulty internal interconnection lines, thereby accurately detecting chip faults and defects. Compared with traditional testing methods, the boundary-scan-based interconnect testing method for multi-chiplet is stable and reliable. It can accurately pinpoint internal interconnection faults within the chip, significantly improves testing efficiency, and ensures the reliable application of chiplet systems.

Key words : chiplet;boundary scan;interconnect test;fault defect

引言

多芯粒异构集成系统是将多种功能芯粒,包括处理器[1]、可编程阵列逻辑(FPGA)[2-4]、存储器[5-6]、模拟等功能芯粒集成在一个封装内,从而实现一个基本完整的功能。在芯粒系统中,摒弃传统的印制电路板(PCB)作为芯片连接载体的方式,有效规避因PCB自身固有缺陷所导致的系统性能瓶颈问题。芯粒系统具有开发周期短、功能多、功耗低、性能更优良、成本价格低、体积小、质量轻的特点,因此被广泛应用于航空航天等诸多领域。

芯粒系统堆叠过程中,随着堆叠芯片数量的增加,互连缺陷造成的芯片失效率呈指数级上升。在芯粒系统中,互连线是指系统内芯粒之间的导线,是系统功能测试的基础,互连测试[7]是芯粒测试过程中的一个重要环节,其目的是验证芯粒各个功能模块之间的通信是否正常。传统测试方法是通过功能测试方法对整个系统功能进行验证,此测试办法在功能失效的情况下无法精确定位具体互连线的失效位置,已经达不到好的测试效果。

本文针对以上存在的问题提出一种基于边界扫描的多芯粒[8-9]互连线测试方法,能够准确定位芯片内部互连故障,是提高故障覆盖率的重要方法之一,具有非常重要的意义,在工业技术等方面也具有重要的参考价值。

本文详细内容请下载:

https://www.chinaaet.com/resource/share/2000007001

作者信息:

陈龙,黄健,解维坤,宋国栋

(中国电子科技集团公司第五十八研究所, 江苏 无锡 214035)

此内容为AET网站原创,未经授权禁止转载。