通过对可编程逻辑器件CPLD用VHDL语言进行编程,实现编码译码过程,本设计采用HDB3码对可编成逻辑器件进行编程。

1 CPLD相关内容及信道编解码

CPLD(Complex Programmable Logic Device)是复杂可编程逻辑器件的简称,它是20世纪90年代初期出现的高密度可编程逻辑器件,采用E2CMOS工艺制作,一般由三种可编程电路组成,即可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线。它可利用EDA技术中的MAX+ PLUS2作为开发工具,将设计的电路图或硬件描述语言编写的程序综合成网表文件写入其中,制成ASIC芯片。CPLD的突出优点是可反复编程,集成度非常高,数据速率快,同时具有较大的灵活性。

2 编码器的VHDL建模与程序设计

2.1 HDB3码编码规则

HDB3码是AMI码的改进型,称为三阶高密度双极性码,它克服了AMI码的长连0串现象。HDB3码的编码规则为先检查消息代码(二进制)的连0串,若没有4个或4个以上连0串,则按照AMI码的编码规则对消息代码进行编码;若出现4个或4个以上连0串,则将每4个连0小段的第4个0变换成与前一非0符号(+1或-1)同极性的V符号,同时保证相邻Y符号的极性交替(即+1记为+V,-1记为-V);接着检查相邻V符号间非0符号的个数是否为偶数,若为偶,则将当前的V符号的前一非0符号后的第1个0变为+B或-B符号,且B的极性与前一非0符号的极性相反,并使后面的非0符号从V符号开始再交替变化。

2.2 HDB3编码器的VHDL建模与程序设计

HDB3码的VHDL建模思想是在消息代码的基础上,依据HDB3编码规则进行插入“V”符号和“B”符号的操作,且用2位二进制代码分别表示。最后完成单极性信号变成双极性信号的转换。其编码模型如图1所示。

2.2.1 插“V”模块的实现

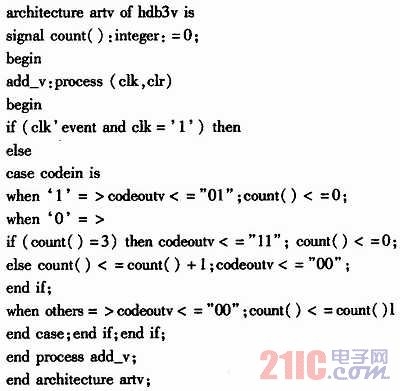

插“V”模块主要是对消息代码里的四连0串的检测,即当出现四个连0串的时候,把第四个“0”变换成符号“V”,用“11”标识。“1”用“01”标识,“0”用“00”标识。实现的VHDL结构代码如arty:

2.2.2 插“B”模块的实现

插“B”模块的建模思路是当相邻“V”符号之间有偶数个非0符号时,把后一小段的第1个“0”变换成一个“B”符号。可用一个4位的移位寄存器来实现延迟,这样经插“V”处理过的码元,可在同步时钟的作用下同时进行是否插“B”的判决,等到码元从移位寄存器里出来的时候,就可以决定是应该变换成“B”符号,还是照原码输出。输出端用“11”表示符号“V”,“01”表示“1”码,“00”表示“0”码,“10”表示符号“B”。VHDL的结构代码如artb:

2.3 单极性变双极性的实现

因为经过插“B”模块后,“V”、“B”、“1”已经分别用双相码“11”、“10”、“01”标识。“0”用“00”标识。而在实际应

用中,CPLD或FPGA端口的输出电压只有正极性电压,且在波形仿真中也只有“+1”和“0”,而无法识别“-1”。所以要得到所需HDB3编码的结果,需定义“00”、“01”、“10”来分别表示“0”、“-1”、“+1”。可将插“B”模块后输出的“00”、“01”、“10”、“11”组合转换为“00”、“01”、“10”组合,再通过“00”、“01”、“10”控制四选一数字开关的地址来选择输出通道,就可以实现0、-B、+B。本设计使用CC4052的一组通道作为四选一数字开关,从而将CPLD或FPGA目标芯片的标识性输出转换成双极性信号,最终实现HDB3非归零编码。

2.4 HDB3编码器的仿真

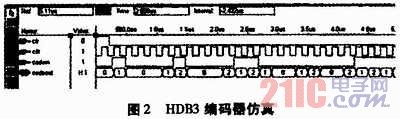

在此,以四连“0”的可能性通过多“0”消息代码进行分析,并利用EDA工具对VHDL源程序进行编译、适配、优化、逻辑综合与仿真。仿真结果显示其完全可以达到编码要求。而将HDB3编码硬件描述下载到CPLD或FPGA目标芯片中,然后连接好CC4052进行实际应用测试(用示波器测得)的编码波形如图2所示。

3 实验结果

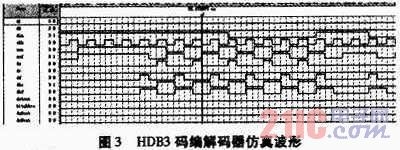

利用QUARTUS2开发工具进行编译和仿真,HDB3码器仿真波形如图3所示。

4 结论

本设计主要是通过用VHDL语言对可编程逻辑器件CPLD进行控制,基于Altera公司的Quartus X软件开发平台,以原理图和VHDL语言方法混合输入设计,实现了信道编码、HDB3码和卷积码的编解码过程。该设计方案与专用的基带传输码型编码芯片相比,有以下优势:体积小,集成度高,开发周期短,设计过程简单便捷,运行速度快,使用方便,成本低。本文设计的编码器能够弥补专用基带传输码型编码芯片的不足,具备一定的工程应用价值。