教程:FPGA PCIE调试及DSP代码的讲解

2022-12-31

来源:FPGA之家

本人调试是将DSP作为RC端,FPGA作为EP端,且下文是对DSP代码的讲解。本人调试参考代码是D: ipdk_C6678_1_1_2_6packages idrvexampleProjectsPCIE_exampleProject。本文所指的PCIE手册为TI公司C6678的pcie技术手册,全名为 KeyStone Architecture Peripheral Component Interconnect Express (PCIe)。pdf

(1)outbound和inbound的理解:

哪一端发起请求哪一端就是outbound。一端是outbound,另一端就是inbound。

对于outbound来说,可以发出写请求和读请求。当作为RC端的DSP对0X60000000发起写请求时,RC发出outbound的写请求,将数据传送给作为EP端的FPGA。当作为RC端的DSP对0X60000000发起读请求时,RC发出outbound的读请求,作为EP端的FPGA先收到读请求然后将数据发给RC端的DSP。

错误理解:简单地将数据出去理解为outbound,数据进去理解为inbound。

DSP存在PCIE_DATA 0x60000000~0x6FFFFFFF这段地址。在这段地址中写数据会触发outbound写机制,在这段地址中读数据会触发outbound读机制。0x60000000该地址在outbound转换机制中为DSP内部总线地址。

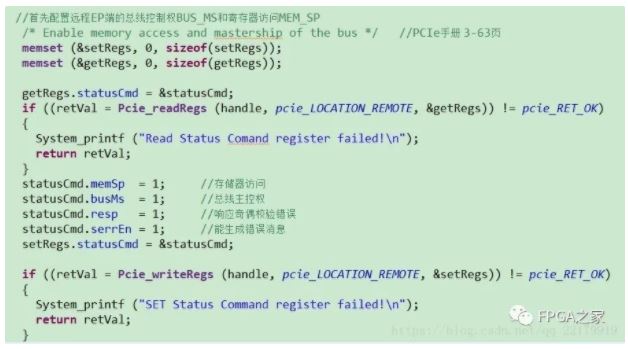

(2)对EP端(远程配置空间)BUS_MS和MEM_SP的配置

RC端对EP发出outbound写时,RC端的DSP必须把作为EP端FPGA的BUS_MS和MEM_SP置为1,否则EP端无法收到数据。BUS_MS为设置总线控制权,MEM_SP为设置存储器访问权限,具体可见pcie手册3-63页。

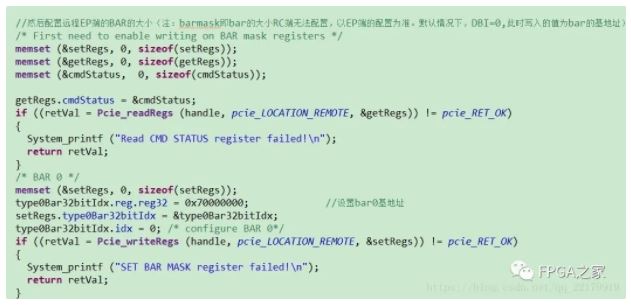

(3)对EP端(远程配置空间)BAR的配置

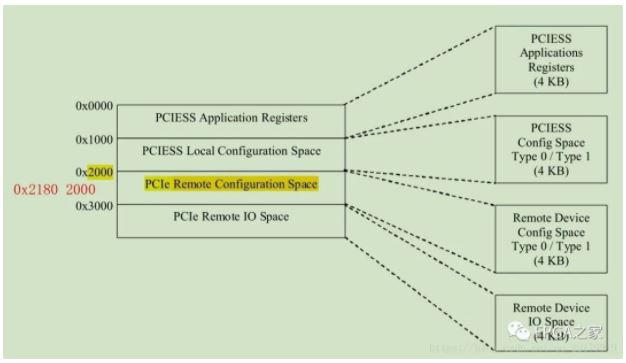

本地配置空间地址 0x21801000,远程配置空间地址 0x21802000,见pcie手册45页。

在PCIE手册中没有关于remote configuraTIon space中具体的寄存器介绍。但是其和local configuraTIon space中寄存器顺序是一样的,只是偏移量将0x1000改成了0x2000。

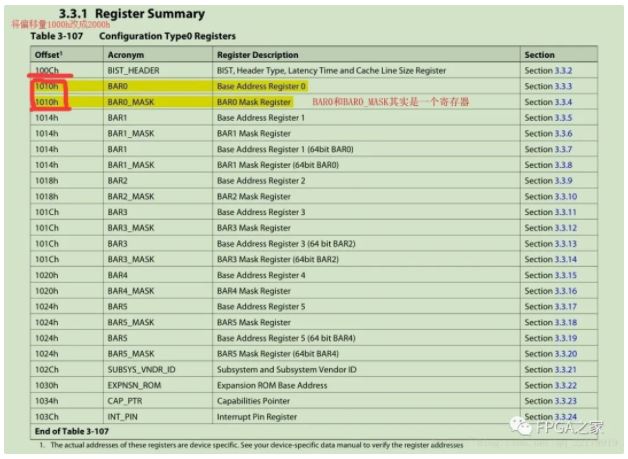

从偏移地址上可以看出BAR0和BAR0_MASK地址是一样的。在DSP端,当DBI=1时,此时写入的值为bar的范围大小(bar_mask)。当DBI=0时,此时写入的值为bar的地址(bar)。(DBI在CMD_STSTUS中,DBI默认值为0)详细寄存器见pcie手册的3.2、3.3、3.4章节的寄存器,同时偏移量也可见FPGA的pcie gen3手册。

RC端无法配置EP端bar mask的大小,只能配置bar的地址。RC端配置的bar基地址会因为EP端配置的bar大小而改变。例如:bar_mask=8MB,那么配置的bar地址的0~22会置为0。

配置远程EP端bar0的具体代码如下图所示。在TLP过滤中,bar接收到的数据包头中存在type这一标志位。type=0对应于EP的configuraTIon space,type=1对应于RC的configuration space。故选择对type0Bar32bitIdx进行配置。idx选择0表示配置bar0。DBI默认为0,直接将数值写入bar0,即为bar0的地址。

(4)DSP作RC端,FPGA作EP端时inbound和outbound地址转换

详细的地址转换过程可见pcie手册2.7节。

首先需要说明的是inbound和outbound机制是DSP独有的,FPGA侧不存在inbound和outbound机制。实际上,在PCIE通信链路中的数据帧中不仅包含发送的数据,还包含PCIE地址,数据类型和数据长度等。由于DSP存在inbound和outbound机制,故不需要人为的依据PCIE通信的规范去组帧和解帧,只需配置好inbound和outbound机制所需的寄存器。

下面根据代码具体解释一下inbound和outbound的转换计算过程。

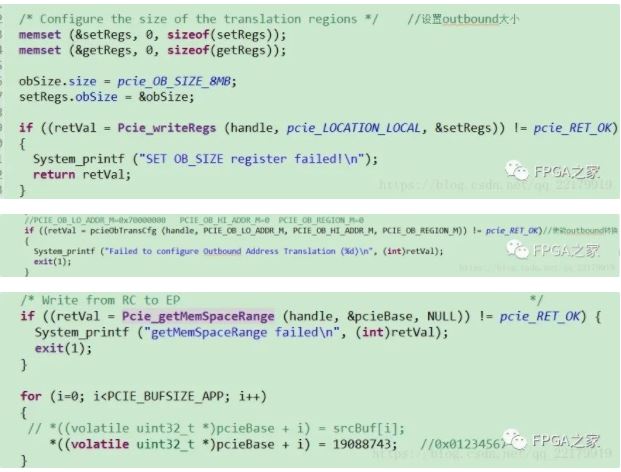

(a) outbound配置如下所示:

由Pcie_getMemSpaceRange (handle, &pcieBase, NULL))函数可以得到pcieBase的地址为0x60000000,此地址即为内部总线地址。关于此地址的详细介绍可以见本位第一章节。

内部总线地址=0x60000000

OB_SIZE= pcie_OB_SIZE_8MB=3

OB_OFFSET_HI= PCIE_OB_HI_ADDR_M=0

PCIE_OB_REGION_M=0 对应于下面的index0,即使用outbound的region 0。

OB_OFFSET_INDEX0= PCIE_OB_LO_ADDR_M=0x70000000

注:第一个参数为PCIE手册中所用参数名,第二个参数为样例代码中所用参数名。

OB_SIZE=3,故取内部总线地址0x60000000的[27:23]位,即index=0

PCIe基地址=OB_OFFSETn_HI+OB_OFFSETn_INDEXn[31:23]

=0+0x70000000[32:23]

PCIe总地址=PCIe基地址+内部总线地址[22:0]

=0x70000000[32:23]+ 0x60000000[22:0]

=0X70000000

即传到PCIE链路中的地址为0x70000000,可以看到的是由于OB_SIZE为8M(因为8M=810241024=2^23 所以取0-22位 ) ,所以要是一次性传输的数据量超过8M的话,要么多次传输,要么再加个region传输。

而这个0x70000000又正好是本文第三章给远程FPGA配置bar0的地址,故FPGA可以收到DSP发送的数据。

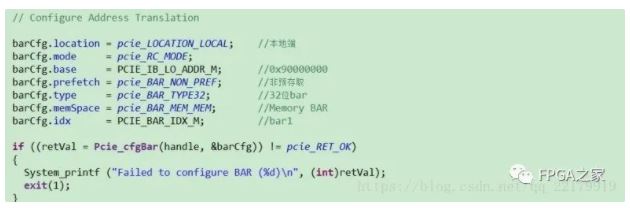

(b) inbound配置如下所示:

指定bar1的地址为0x90000000,且为32位bar。

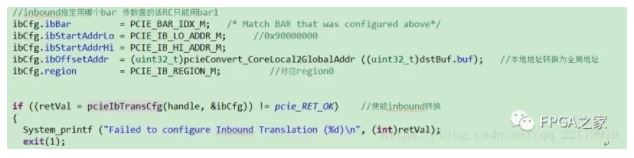

将bar1绑定给inbound机制,且使用region 0

pcieConvert_CoreLocal2GlobalAddr()作用是将本地地址转换为全局地址。在6678中一共有8个核,对于核0来说L2 SRAM本地起始地址为0x00800000,L2 SRAM全局起始地址为0x10800000,两者差值为0x10000000。

IB_START1_HI = PCIE_IB_HI_ADDR_M=0

IB_START1_LO = PCIE_IB_LO_ADDR_M=0x90000000

IB_OFFSET1 = dstBuf.buf的全局地址

注:第一个参数为PCIE手册中所用参数名,第二个参数为样例代码中所用参数名。

PCIe地址偏移量=PCIe地址 -(IB_STARTn_HI:IB_STARTn_LO)

= PCIe地址 – 0x90000000

内部总线地址=IB_OFFSETn+ PCIe地址偏移量

= dstBuf.buf的全局地址+ PCIe地址 – 0x90000000

我们将内部总线设为dstBuf.buf的全局地址,即将从FPGA侧收到的数据存放在dstBuf.buf中。由此我们可以计算出PCIE地址:

dstBuf.buf的全局地址= dstBuf.buf的全局地址+ PCIe地址 – 0x90000000

PCIe地址=0x90000000

FPGA侧将这里计算出来的PCIE地址用在发送数据时的组帧过程里,DSP侧就可以从dstBuf.buf这个变量地址里读到FPGA侧发过来的数据。

更多信息可以来这里获取==>>电子技术应用-AET<<