目前基于FPGA和DSP结构的软件无线电技术被广泛应用在数字接收机设计中,雷达接收机领域的数字化技术也在日趋发展,如何借助数字化的软硬件优势设计出易实现、灵活,并满足不同性能指标和目的的数字接收机成为工程设计的焦点。本文结合某连续波测速雷达数字接收机的设计实现,给出了一种基于模块化的FPGA设计方案,并在此基础上重点讨论了信号处理模块的设计。

1 雷达接收机概述

雷达接收机的任务是通过适当的滤波将天线上接收到的微弱高频信号从伴随的噪声和干扰中选择出来,并经过放大和检波后,送至显示器、信号处理器或由计算机控制的雷达终端设备。雷达接收机可以按应用、设计、功能和结构等多种方式来分类。但是,一般来说可以将雷达接收机分为超外差式、超再生式、晶体视放式和调谐高频式等4种类型,其中超外差式雷达接收机具有灵敏度高、增益高、选择性好和适用性广等优点,实际中在很多的雷达系统中都获得应用。超外差式雷达接收机的简化方框图如图1所示。

2 数字中频接收机原理

由于受器件水平的制约,数字接收技术目前还难以在射频频段直接实现,一般在中频进行数字化。目前所说的数字测速即是利用中频数字锁相环来完成多普勒频率的提取及测量。数字中频接收机主要由数字化正交处理单元、数字载波锁相环和自动增益控制(AGC)环组成。

中频经A/D采样后的数字信号与数控振荡器(NC0)产生的数字正交信号分别进行数字混频,各经过FIR数字低通滤波器,得到I、Q两路数字窄带信号。I、Q两路信号分别作为数字信号的实部和虚部,做FFT分析,估算出多普勒信息,输出频率控制码控制NCO输出,实现快速载波频率引导。I路信号再经过低通滤波器(LF1)完成数字滤波,控制NCO的输出频率,从而构成数字锁相环,在频率引导成功后实现对载波信号的快速捕获与跟踪。环路锁定后从环路滤波器输出可以提取出多普勒信息。Q路信号经过一个低通滤波器(LF2),通过I、Q提取输入信号的幅度信息,实现信号的AGC控制。

3 模块化设计在FPGA的具体应用

本接收机主要功能是完成连续波雷达的测速和测角任务,设计时在保证指标的前提下,贯彻简洁至上的原则;并且尽量采用先进、成熟的数字处理技术和软件无线电技术,贯彻模块化、通用化、系列化、组合化设计原则,确保系统先进、稳定、可靠。中频数字接收机是整个接收机部分的核心,设计时遵循简洁、灵活的特点,尽量减少硬件电路的功能,使其结构简洁,降低设计和实现的难度,而把复杂的处理交由软件完成。

3.1 FPGA模块组成

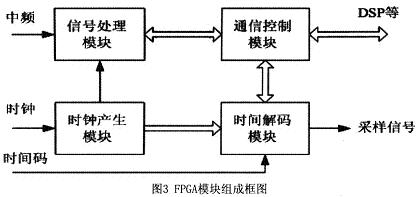

FPGA是整个数字中频接收机的通信枢纽,同时还参与部分信号处理工作,FPGA由时钟产生模块、时间解码模块、信号处理模块和通信控制模块四部分组成,分别完成四大基本功能,如3.2节所述。

3.2 FPGA各个模块的基本功能

3.2.1 时钟产生模块

时钟产生模块利用系统基准信号为整个系统提供时钟信号,保证系统的同步运行,具体如下:为ADC提供采样信号;为DSP提供时钟信号;为信号处理模块提供时钟信号;为时间解码模块提供时钟信号;为通信控制模块提供时钟信号。其中,后3类时钟信号为FPGA内部信号,无需输出。

3.2.2 时间解码模块

时间解码模块利用时间码信号和时钟产生模块送来的时钟信号为整个系统提供时间信息和时基信号,保证系统在时间上的同步运行,具体如下:接收时间码信号,解码得到时间信息;产生与时间码信号对准的时基信号。

3.2.3 信号处理模块

信号处理模块接收ADC数据,完成信号处理,包括以下内容:信号的下变频处理;信号的滤波抽取处理。

3.2.4 通信控制模块

通信控制模块其外部完成与DSP单元、外部设备的通信;其内部完成与时钟产生模块、时间解码模块、信号处理模块的通信。

3.3 FP6A各个模块设计原理及解决方法

3.3.1 各模块组成

(1)时钟产生模块。时钟信号的产生利用PLL和分频器,对基准信号进行处理得到,设计时应注意ADC采样信号同相,同时保证信号处理模块时钟信号和FPGA接收的ADC数据相差要求的固定值。

(2)时间解码模块。时间解码模块由编码器、解码器和分频链组成,时间码解码器的主要作用是译码得到秒信号和时间信息,分频链路的主要作用是产生与译码秒同步的分频信号。

(3)信号处理模块。信号处理模块由A、B两个通道组成,两个通道结构相同,分别处理两个点频的中频信号;每个通道又由和信号和差信号两个子通道组成,两个子通道都是数字下变频器(DDC),其结构相同,分别处理和/差两路信号。原理框图如图4所示。

对于每个通道而言,和信号的处理结果分为一次抽取结果和二次抽取结果(每个结果又包含同相和正交两路),分别用于信号频谱识别和环路跟踪;差信号的处理结果为二次抽取结果,同相和正交两路信号分别对应于方位和俯仰角误差信号。