18A与14A工艺合体 英特尔秀出最强3D封装肌肉

2025-12-24

来源:IT之家

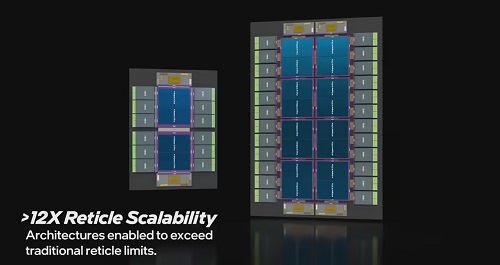

12 月 24 日消息,科技媒体 Wccftech 昨日(12 月 23 日)发布博文,报道称英特尔针对高性能计算(HPC)和 AI 数据中心场景,展示其在大规模芯片封装领域的最新成果,能够构建超过传统光罩尺寸 12 倍的超大芯片。

光罩极限(Reticle Limit)芯片制造中光刻机单次曝光的最大面积,突破此极限(如 >12x)意味着通过拼接技术制造出比传统单颗芯片大得多的巨型芯片。

援引博文介绍,英特尔针对未来算力需求,设计展示了两种概念架构:一种集成了 4 个计算模块与 12 个 HBM 内存位点,另一种则更为激进,集成了 16 个计算模块与 24 个 HBM 位点。

这些设计显示出英特尔在争夺 AI 和数据中心市场方面的决心,不仅在规模上超越现有标准,更直接对标台积电的 CoWoS 解决方案(目前规划为 9.5 倍光罩尺寸)。

该封装方案采用了精密的 3D 堆叠结构。底层基础晶圆(Base Die)采用 Intel 18A-PT 工艺制造,该工艺为提升逻辑密度和电源稳定性,引入了背面供电技术(Backside Power)。

传统芯片是从正面给晶体管供电,线路复杂且干扰信号。背面供电就像把房子的电线全部埋在地下,给地面的房间(晶体管)腾出更多空间传输数据。

基础晶圆内集成了大量 SRAM 缓存,其设计思路与“Clearwater Forest”处理器类似。Clearwater Forest 采用 18A 工艺节点制造,其三单元基片方案中集成了 576 MB 的 L3 缓存。Clearwater Forest 的基片采用 Intel 3 工艺技术制造,因此我们可以预期 Intel 18A-PT 将进一步优化并增加未来芯片中 SRAM 的数量。

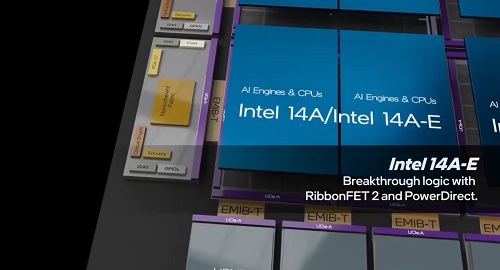

基础 Tile 之上是主计算 Tile,采用 Intel 14A 或 14A-E 工艺制造,包含 AI 引擎或 CPU 核心。

两者通过 Foveros Direct 3D 技术进行垂直互连,利用混合键合(Hybrid Bonding)实现了极小间距的高速通信。

为解决多芯片间的通信瓶颈,英特尔部署了下一代 EMIB-T(嵌入式多芯片互连桥接)技术。该技术引入了硅通孔(TSV),大幅提升了带宽并支持更大规模的模块集成。

注:EMIB-T 相当于在芯片之间修了一座“高速立体高架桥”,不仅能水平连接,还能通过硅通孔(TSV)进行垂直连接。

在存储方面,该方案展现了极高的兼容性,支持 HBM3、HBM4 乃至未来的 HBM5 标准。顶层芯片设计可容纳多达 24 个 HBM 位点,或集成 48 个 LPDDR5x 控制器,这种极高的内存密度将为处理大规模 AI 模型和数据中心工作负载提供关键支撑。

该媒体解读认为,此次技术展示不仅仅是工程能力的秀场,更是英特尔代工服务(Intel Foundry)争取外部客户的关键信号。虽然 18A 节点主要用于英特尔自家产品,但 14A 节点被明确设计为面向第三方客户的开放工艺。

英特尔正通过展示这种高度可扩展的封装生态系统,试图证明其在制造和封装领域的领先地位,以期在经历了 Ponte Vecchio 等项目的挫折后,凭借 Jaguar Shores 等未来产品及代工订单重回巅峰。