经过近几年的快速发展,嵌入式系统(Embedded system)已经成为电子信息产业中最具增长力的一个分支。随着手机、PDA、GPS、机顶盒等新兴产品的大量应用,嵌入式系统的市场正在以每年30%的速度递增(IDC预测),嵌入式系统的设计也成为软硬件工程师越来越关心的话题。

在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人员必须面对的问题,其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中去,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电,所以设计人员从每一个细节来考虑降低功率消耗,从而尽可能地延长电池使用时间。事实上,从全局来考虑低功耗设计已经成为了一个越来越迫切的问题。

那么,我们应该从哪些方面来考虑低功耗设计呢?笔者认为应从以下几方面综合考虑:

处理器的选择

接口驱动电路设计

动态电源管理

电源供给电路的选择

下面我们分别进行讨论:

一、处理器的选择

我们对一个嵌入式系统的选型往往是从其CPU和操作系统(OS)开始的,一旦这两者选定,整个大的系统框架便选定了。我们在选择一个CPU的时候,一般更注意其性能的优劣(比如时钟频率等)及所提供的接口和功能的多少,往往忽视其功耗特性。但是因为CPU是嵌入式系统功率消耗的主要来源---对于手持设备来讲,它几乎占据了除显示屏以外的整个系统功

耗的一半以上(视系统具体情况而定),所以选择合适的CPU对于最后的系统功耗大小有举足轻重的影响。

一般的情况下,我们是在CPU的性能(Performance)和功耗(Power Consumption)方面进行比较和选择。通常可以采用每执行1M次指令所消耗的能量来进行衡量,即Watt/MIPS。但是,这仅仅是一个参考指标,实际上各个CPU的体系结构相差很大,衡量性能的方式也不尽相同,所以,我们还应该进一步分析一些细节。

我们把CPU的功率消耗分为两大部分:内核消耗功率PCORE和外部接口控制器消耗功率PI/O,总的功率等于两者之和,即P=PCORE+PI/O。对于PCORE,关键在于其供电电压和时钟频率的高低;对于PI/O来讲,除了留意各个专门I/O控制器的功耗外,还必须关注地址和数据总线宽度。下面对两者分别进行讨论:

1、CPU供电电压和时钟频率

我们知道,在数字集成电路设计中,CMOS电路的静态功耗很低,与其动态功耗相比基本可以忽略不计,故暂不考虑。其动态功耗计算公式为:

Pd=CTV2f

式中,Pd---CMOS芯片的动态功耗

CT----CMOS芯片的负载电容

V----CMOS芯片的工作电压

f-----CMOS芯片的工作频率

由上式可知,CMOS电路中的功率消耗是与电路的开关频率呈线性关系,与供电电压呈二次平方关系。对于一颗CPU来讲,Vcore电压越高,时钟频率越快,则功率消耗越大。所以,在能够满足功能正常的前提下,尽可能选择低电压工作的CPU能够在总体功耗方面得到较好的效果。对于已经选定的CPU来讲,降低供电电压和工作频率,也是一条节省功率的可行之路。

2、总线宽度

我们还经常陷入一个误区,即:CPU外部总线宽度越宽越好。如果我们仅仅从数据传输速度上来讲,也许这个观点是对的,但如果在一个对功耗相当敏感的设计来说,这个观点就不一定正确了。

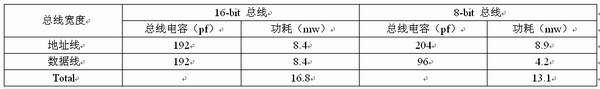

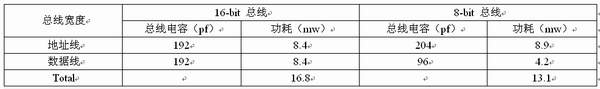

同样引用公式Pd=CTV2f ,对于每一条线(地址等数据线)而言,都会面临这样的功率消耗,显而易见,当总线宽度越宽的时候,功耗自然越大。每条线路的容性负载都不太一样,但一般都在4~12PF之间。我们来看下面一个例子:一片1Mbit Flash通过8bit和16bit的

总线与CPU相连,总线频率为4MHZ ,总线电压为3.3V。我们可以得到以下结果:

由上可见,采用16-bit总线和采用8-bit总线会有3.7mw的功耗差异。

当然,如果需要大量频繁地存取数据的场合下,用8-bit总线不见得会经济,因为增加了读写周期。

另外,从上面的例子我们也可以看到:如果CPU采用内置Flash的方式,也可大大地降低系统功率消耗。

二、接口驱动电路的低功耗设计

接口电路的低功耗设计,往往是容易被大家所忽略的一个环节,在这个环节里,我们除了考虑选用静态电流较低的外围芯片外,还应该考虑以下几个因素:

上拉电阻/下拉电阻的选取

对悬空脚的处理

Buffer的必要性

通常我们习惯随意地确定一个上拉电阻值,而没有经过仔细地计算。现在我们来简单计算一下,如果在一个3.3V的系统里用4.7KΩ为上拉电阻,当输出为低的时候,每只脚上的电流消耗就为0.7mA,如果有10个这样的信号脚时,就会有7mA电流消耗在这上面。所以我们应该在考虑在能够正常驱动后级的情况下(即考虑IC的VIH或VIL),尽可能选取更大的阻值。现在很多应用设计中的上拉电阻值甚至高达几百KΩ。另外,当一个信号在多数情况下时为低的时候,我们也可以考虑用下拉电阻以节省功率。

CMOS器件的悬空脚也应该引起我们的重视。因为CMOS悬空的输入端的输入阻抗极高,很可能感应一些电荷导致器件被高压击穿,而且还会导致输入端信号电平随机变化,导致CPU在休眠时不断地被唤醒,从而无法进入休眠状态或其他莫名其妙的故障,所以正确的方法是将未使用到的输入端接到VCC或地。

Buffer有很多功能,如电平转换,增加驱动能力,数据传输的方向控制等等,但如果仅仅基于驱动能力的考虑增加Buffer的话,我们就应该慎重考虑了,因为过驱动会导致更多的能量被白白浪费掉。所以我们应该仔细检查芯片的最大输出电流IOH和IOL是否足以驱动下级IC,如果可以通过选取合适的前后级芯片来避免Buffer的使用,对于能量来讲是一个很大的节约。

三、动态电源管理(DPM)

所谓动态的电源管理就是在系统运行期间通过对系统的时钟或电压的动态控制来达到节省功率的目的,这种动态控制是与系统的运行状态密切相关的,这个工作往往通过软件来实现。

1、选取不同工作模式

如前所述,系统时钟对于功耗大小有非常明显的影响。所以我们除了着重于满足性能的需求外,还必须考虑如何动态地设置时钟来达到功率的最大程度节约。CPU内部的各种频率都是通过外部晶振频率经由内部锁相环(PLL)倍频式后产生的。于是,是否可以通过内部寄存器设置各种工作频率的高低成为控制功耗的一个关键因素。现在很多CPU都有多种工作模式,我们可以通过控制CPU进入不同的模式来达到省电的目的。

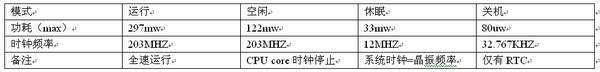

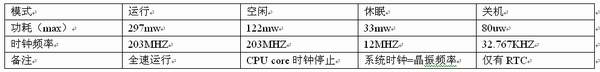

我们以SAMSUNG S3C2410X (32bit ARM 920T内核)为例,它提供了四种工作模式:正常模式、空闲模式、休眠模式、关机模式,各种模式的功耗如下:

由上图可见,CPU在全速运行的时候比在空闲或者休眠的时候消耗的功率大得多。省电的原则就是让正常运行模式远比空闲、休眠模式少占用时间。在类似PDA的设备中,系统在全速运行的时候远比空闲的时候少,所以我们可以通过设置使CPU尽可能工作在空闲状态,然后通过相应的中断唤醒CPU,恢复到正常工作模式,处理响应的事件,然后再进入空闲模式。

经过近几年的快速发展,嵌入式系统(Embedded system)已经成为电子信息产业中最具增长力的一个分支。随着手机、PDA、GPS、机顶盒等新兴产品的大量应用,嵌入式系统的市场正在以每年30%的速度递增(IDC预测),嵌入式系统的设计也成为软硬件工程师越来越关心的话题。

在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人员必须面对的问题,其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中去,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电,所以设计人员从每一个细节来考虑降低功率消耗,从而尽可能地延长电池使用时间。事实上,从全局来考虑低功耗设计已经成为了一个越来越迫切的问题。

那么,我们应该从哪些方面来考虑低功耗设计呢?笔者认为应从以下几方面综合考虑:

处理器的选择

接口驱动电路设计

动态电源管理

电源供给电路的选择

下面我们分别进行讨论:

一、处理器的选择

我们对一个嵌入式系统的选型往往是从其CPU和操作系统(OS)开始的,一旦这两者选定,整个大的系统框架便选定了。我们在选择一个CPU的时候,一般更注意其性能的优劣(比如时钟频率等)及所提供的接口和功能的多少,往往忽视其功耗特性。但是因为CPU是嵌入式系统功率消耗的主要来源---对于手持设备来讲,它几乎占据了除显示屏以外的整个系统功

耗的一半以上(视系统具体情况而定),所以选择合适的CPU对于最后的系统功耗大小有举足轻重的影响。

一般的情况下,我们是在CPU的性能(Performance)和功耗(Power Consumption)方面进行比较和选择。通常可以采用每执行1M次指令所消耗的能量来进行衡量,即Watt/MIPS。但是,这仅仅是一个参考指标,实际上各个CPU的体系结构相差很大,衡量性能的方式也不尽相同,所以,我们还应该进一步分析一些细节。

我们把CPU的功率消耗分为两大部分:内核消耗功率PCORE和外部接口控制器消耗功率PI/O,总的功率等于两者之和,即P=PCORE+PI/O。对于PCORE,关键在于其供电电压和时钟频率的高低;对于PI/O来讲,除了留意各个专门I/O控制器的功耗外,还必须关注地址和数据总线宽度。下面对两者分别进行讨论:

1、CPU供电电压和时钟频率

我们知道,在数字集成电路设计中,CMOS电路的静态功耗很低,与其动态功耗相比基本可以忽略不计,故暂不考虑。其动态功耗计算公式为:

Pd=CTV2f

式中,Pd---CMOS芯片的动态功耗

CT----CMOS芯片的负载电容

V----CMOS芯片的工作电压

f-----CMOS芯片的工作频率

由上式可知,CMOS电路中的功率消耗是与电路的开关频率呈线性关系,与供电电压呈二次平方关系。对于一颗CPU来讲,Vcore电压越高,时钟频率越快,则功率消耗越大。所以,在能够满足功能正常的前提下,尽可能选择低电压工作的CPU能够在总体功耗方面得到较好的效果。对于已经选定的CPU来讲,降低供电电压和工作频率,也是一条节省功率的可行之路。

2、总线宽度

我们还经常陷入一个误区,即:CPU外部总线宽度越宽越好。如果我们仅仅从数据传输速度上来讲,也许这个观点是对的,但如果在一个对功耗相当敏感的设计来说,这个观点就不一定正确了。

同样引用公式Pd=CTV2f ,对于每一条线(地址等数据线)而言,都会面临这样的功率消耗,显而易见,当总线宽度越宽的时候,功耗自然越大。每条线路的容性负载都不太一样,但一般都在4~12PF之间。我们来看下面一个例子:一片1Mbit Flash通过8bit和16bit的

总线与CPU相连,总线频率为4MHZ ,总线电压为3.3V。我们可以得到以下结果:

由上可见,采用16-bit总线和采用8-bit总线会有3.7mw的功耗差异。

当然,如果需要大量频繁地存取数据的场合下,用8-bit总线不见得会经济,因为增加了读写周期。

另外,从上面的例子我们也可以看到:如果CPU采用内置Flash的方式,也可大大地降低系统功率消耗。

二、接口驱动电路的低功耗设计

接口电路的低功耗设计,往往是容易被大家所忽略的一个环节,在这个环节里,我们除了考虑选用静态电流较低的外围芯片外,还应该考虑以下几个因素:

上拉电阻/下拉电阻的选取

对悬空脚的处理

Buffer的必要性

通常我们习惯随意地确定一个上拉电阻值,而没有经过仔细地计算。现在我们来简单计算一下,如果在一个3.3V的系统里用4.7KΩ为上拉电阻,当输出为低的时候,每只脚上的电流消耗就为0.7mA,如果有10个这样的信号脚时,就会有7mA电流消耗在这上面。所以我们应该在考虑在能够正常驱动后级的情况下(即考虑IC的VIH或VIL),尽可能选取更大的阻值。现在很多应用设计中的上拉电阻值甚至高达几百KΩ。另外,当一个信号在多数情况下时为低的时候,我们也可以考虑用下拉电阻以节省功率。

CMOS器件的悬空脚也应该引起我们的重视。因为CMOS悬空的输入端的输入阻抗极高,很可能感应一些电荷导致器件被高压击穿,而且还会导致输入端信号电平随机变化,导致CPU在休眠时不断地被唤醒,从而无法进入休眠状态或其他莫名其妙的故障,所以正确的方法是将未使用到的输入端接到VCC或地。

Buffer有很多功能,如电平转换,增加驱动能力,数据传输的方向控制等等,但如果仅仅基于驱动能力的考虑增加Buffer的话,我们就应该慎重考虑了,因为过驱动会导致更多的能量被白白浪费掉。所以我们应该仔细检查芯片的最大输出电流IOH和IOL是否足以驱动下级IC,如果可以通过选取合适的前后级芯片来避免Buffer的使用,对于能量来讲是一个很大的节约。

三、动态电源管理(DPM)

所谓动态的电源管理就是在系统运行期间通过对系统的时钟或电压的动态控制来达到节省功率的目的,这种动态控制是与系统的运行状态密切相关的,这个工作往往通过软件来实现。

1、选取不同工作模式

如前所述,系统时钟对于功耗大小有非常明显的影响。所以我们除了着重于满足性能的需求外,还必须考虑如何动态地设置时钟来达到功率的最大程度节约。CPU内部的各种频率都是通过外部晶振频率经由内部锁相环(PLL)倍频式后产生的。于是,是否可以通过内部寄存器设置各种工作频率的高低成为控制功耗的一个关键因素。现在很多CPU都有多种工作模式,我们可以通过控制CPU进入不同的模式来达到省电的目的。

我们以SAMSUNG S3C2410X (32bit ARM 920T内核)为例,它提供了四种工作模式:正常模式、空闲模式、休眠模式、关机模式,各种模式的功耗如下:

由上图可见,CPU在全速运行的时候比在空闲或者休眠的时候消耗的功率大得多。省电的原则就是让正常运行模式远比空闲、休眠模式少占用时间。在类似PDA的设备中,系统在全速运行的时候远比空闲的时候少,所以我们可以通过设置使CPU尽可能工作在空闲状态,然后通过相应的中断唤醒CPU,恢复到正常工作模式,处理响应的事件,然后再进入空闲模式。