摘要:采用两片TI公司的专用视频处理芯片TMS320DM642设计了一种多路视频监控系统。其中,DSP1与视频采集芯片SAA7113共同完成多路视频的采集,并拼接成一路视频图像输出;DSP2完成对DSP1输出图像的采集、压缩和视频传输。该方案结构灵活、拓展性强,可以实现4路视频的实时采集与传送。

关键词:视频监控系统;TMS320DM642;双DSP;BT.656

引言

在钢铁冶炼加工等高温高危行业中,有许多场合不适合工人长时间在现场监控设备运行,因此需要在现场建立隔离工作室,利用视频监控系统将现场的实时视频采集和传输至工作室中。为了实现全方位的设备监控,往往需要多路视频监控系统,本文针对实际情况,采用TI公司的专用视频处理芯片TMS320DM642构建单板多路视频监控系统。该系统连接简单、方便,设备成本低,可以广泛应用于现场监控系统中。

1 核心处理器选择

视频系统通常包括视频信号的采集、处理和输出。其中最核心的部分是处理部分。对于4路720×576标清格式的PAL制式视频采集系统及1路720×576标清格式的PAL制式视频输出,系统输入的数据量为:

(720×576)×4×16 bit×25Hz≈79.1 MB/s

输出数据量为:

(720×576)×16 bit×25 Hz≈19.8 MB/s

处理如此巨大的数据量成为多路视频监控系统的最大瓶颈。这要求DSP有足够出色的外部接口能力和较高的内核时钟,使用高速的缓冲设备和高速的存储器,并采用各种技术完成超大量视频数据的采集和处理。

TMS320DM642(简称DM642)是TI公司推出的专用视频处理芯片。其基于C64X内核,采用VLIW(超长指令字)结构和二级缓存结构;最高主频时钟达720 MHz,拥有丰富的外设接口:拥有3个可配置视频口,可实现与视频输入/输出的无缝连接;拥有64路可配置EDMA,可以灵活地实现数据的搬移操作;具有64位外部存储器接口(EMIFA),可以连接同步或者异步的存储器和外设;拥有I2C总线接口,可实现对外部编解码芯片的配置。

DM642拥有3个可配置的视频口外设(VP0,VP1,VP2)。每个视频口具有两个通道,每个通道都可以实现与通用视频编码器和解码器无缝链接,支持CCIR-601、ITU-BT.656、BT.1120等视频标准。这样每个DSP可以配置2个视频用于视频采集(即同时采集4个通道),另一个视频

口用于输出显示。另外,DM642还拥有一个10/100M以太网接口,可以实现与外部网络的连接。因此,采用DM642作为主处理芯片来实现视频的采集、压缩与传输等功能。考虑到系统不仅需要采集多路标清PAL制式视频,还需要进行H.264压缩编码,很难利用单DSP系统来达到实时性要求,因此采用了双DSP系统。其中一个DSP负责采集与拼接,另一个DSP负责视频压缩与传送。

2 系统总体设计

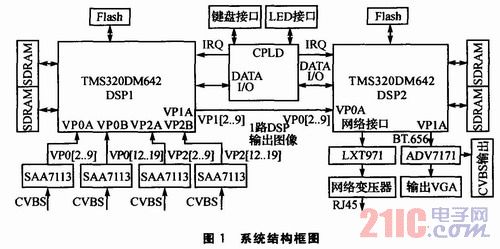

系统采用DM642为系统核心芯片,利用DM642的视频口互连技术实现DSP间的通信。在视频采集端,由DSP1和4个SAA7113构成4路视频采集系统,DSP1的视频输出口接DSP2的视频采集输入口。DSP2在系统中主要实现H.264压缩编码功能,压缩后的数据通过网络接口送至总监控室;另外,DSP2的视频口2外接视频编码芯片,完成模拟CVBS及RGB格式视频数据的输出。系统结构框图如图1所示。

3 系统硬件设计

3.1 视频解码模块设计

视频解码模块也称为视频采集模块,它由数字视频解码芯片SAA7113和视频源(模拟CVBS信号)组成。输入的图像经过视频解码模块进行A/D转换后,才能送给视频处理模块。该解码模块采用Philips公司的SAA7113芯片来进行采集。图像传感器输出的模拟CVBS信号经SAA7113视频芯片转换为数字信号,输出的数字信号经过DM642视频口的内部FIFO缓冲后,由DM642的。EDMA通道将数据传送到片外SDRAM中,以便视频处理程序使用。DM642通过I2C控制器对SAA7113进行配置,使其输出BT.656格式4:2:2的YUV视频数据流。

这里需要说明的是,由于DM642只有一个I2C接口,最多只能寻址两个I2C从设备。为了实现DM642对4个视频解码芯片的配置,使用一个多路选择开关74CBT3257将I2C总线分成I2C0和I2C1。I2C总线切换电路如图2所示。

3.2 双DSP通信设计

实现双DM642的通信设计可以采用两种方式:双端口RAM和视频口互连。双端口RAM采用共享内存的模式,系统时序复杂,快速双端口RAM的成本代价高,因此在本系统中采用视频口互连技术实现双DSP的通信设计。

采用视频口互连技术的优点有:

①电路设计简单,实现系统通信只需要13根信号线,包括8根视频口数据线、2根时钟线及3根可选的控制信号线(行场同步信号)。

②DM642的视频支持BT.656格式视频输出,而BT.656格式数字视频将同步信号内嵌在数据流中,因此无需行场同步信号,即无需其他芯片辅助控制。

③传输速率高,可达80 MB/s。

双DSP通信模块的设计如图3所示。系统只需将DSP1的视频口1配置成显示模式,则VP1A将输出符合BT.656格式的数字视频数据流;同时将DSP2的视频口0配置成采集模式,采集DSP1输出的BT.656数字视频流,然后进行解隔行及H.264压缩处理。由于BT.656数字视频流内嵌有同步信号,因此VPxCTL[O:2]可接可不接。

3.3 网络接口模块设计

网络接口模块主要由DM642以太网接口、网络物理层芯片LXT971及网络变压器组成,其主要功能是将经DSP2压缩编码后的H.264视频数据流传输到总监控室中。LXT971是10/100Base-TX以太网控制器,兼容IEEE802.3标准,提供MII接口,可实现与DM642的MII接口无缝连接。系统中的网络变压器采用1:1的HR601680,其主要作用是匹配阻抗、增强信号、提高传输距离以及实现电压隔离。由于LXT971芯片的UTP端口

为电流型驱动,因此网络变压器的中间抽头应接电容到地端。从DM642传输来的数据经LXT971转换为以太网物理层能接收的数据后,经由网络变压器通过RJ-45接口传输到以太网。

3.4 视频编码模块设计

视频编码模块也称为视频显示模块。采用ADV7171实现视频编码功能,得到一路CVBS及一路VGA模拟视频输出。ADV7171是ADI公司生产的视频编码器,可将符合BT.656及BT.601格式的数字视频转换成CVBS复合视频信号、模拟RGB信号或者S-Video信号输出,同时支持电视字幕及图文电视。其功能框图如图4所示。DM642的VP1A输出BT.656数字视频流至ADV7171,ADV7171完成编码及格式转换功能后同时输出一路CVBS信号及一路RGB信号;同时,利用DM642的I2C接口完成ADV7171的配置。

3.5 存储空间扩展

DM642采用存储映射的方式来组织存储空间,其中二级缓存映射在0x00000000~0x0003FFFF(共256 KB),外部存储器空间映射在0x80000 000以后的地址空间中。外部存储空间又分为4个可独立寻址的空间,自地址0x80000000其各占256 MB,每个存储空间对应一个CE空间控制寄存器,通过寄存器设置每一个空间的存储器类型。

DM642通过EMIF(External Memory Interface)存储器接口访问片外存储器,它集成了数组总线、地址总线、异步控制总线及SDRAM、SBS-RAM控制总线,支持SDRAM、SBSRAM、Flash等存储器无缝接口设计。将空间配置成64位宽度,只用于SDRAM内存的映射;空间配置成8位数据宽度,用于Flash存储空间扩展;、本设计中未使用,留作将来扩展使用。

3.5.1 SDRAM接口

DM642的EMIF接口拥有SDRAM控制器接口,可以实现与SDRAM芯片的无缝连接。将子空间配置为64位的SDRAM接口,将两片4M×32位的SDRAM拓展成4M×64位,在子空间的具体地址定位为0x80000000~0x81FFFFFF。SDRAM采用Hynix公司的HY57V283220芯片。它具有4个物理Bank,每个Bank的空间为1M×32位,刷新周期为64 ms,可以连续或者交错突发读写1、2、4、8或整页数据。SDRAM的工作时钟由DSP的ECLK-OUT1提供,可由AEA19和AEA20引脚配置为EMIF的CPU时钟的1/4或1/6。SDRAM主要用来存储大量的图像数据。每片DSP需要2片SDRAM,2片DSP就需要4片SDRAM。SDRAM扩展原理图略一编者注。

3.5.2 Flash接口

DM642的外部存储器接口还提供了异步接口,用于与多种存储器和可编程外部设备接口,如SDRAM、E2PROM和Flash存储器,同时也包括FPGA、CPLD等。系统为每个DSP都配置了一片4M×8位的Flash,用于固化程序和初始化数据。系统上电或者复位后,从Flash的0x00000000处开始加载程序和数据到SDRAM空间。DSP将EMIF的空间配置为8位异步静态存储器Flash接口。Flash选用90 ns的AM29LV320DT,拥有22根地址线。由于DM642的外部地址总线只有A[22:3],所以子空间的最大寻址范围为1M×8位。CE1子空间除了分配给Flash空间外,还分配给状态/控制寄存器等资源使用,Flash只占据CE1子空间的一半寻址空间,最大可寻址范围为512K×8位,而Flash的设计容量为4M×8位。为了访问整个Flash空间,需将Flash进行分页,每页为512 KB,共分8页,页地址PA20、PA19、PA18及Flash片选信号都是来自CPLD。Flash接口电路略——编者注。

4 PCB电路设计

DM642的内核时钟达到720 MHz,SDRAM总线速度达到133 MHz,系统属于高速信号电路。为了保证系统正常工作,需要考虑传输线效应、信号完整性、电源完整性及电磁兼容性等问题,利用高速电路布线知识设计阻抗匹配及层叠结构,并保证良好的供电系统。

首先,一个良好的叠层设计是保证系统的信号完整性及电源完整性的关键,同时良好的叠层结构设计也有助于电路的布通。本系统中采用8层电路结构,这8层板分层结构为信号层1一地层一信号层2一电源层一地层一信号层3一地层一信号层4,其中信号层1和信号层4分别为Top层和Bottom层。这样的叠层设计使得电源层和地层紧邻,可以保证系统电源的完整性设计;同时,处于信号层之间的地层将4个信号层有效地隔离开,使得信号层之间信号线间的串扰达到最小,以保证信号的回流路径,从而保证系统的信号完整性。

其次,对于系统中的高速总线信号必须进行阻抗匹配,从而减少信号反射及信号的过冲。常见的匹配网络有串行端接及AC并行端接,考虑到PCB布线空间的影响,总线信号一般采用电阻串行端接的方式,而模拟视频信号线则采用AC并行端接的方式。在系统设计阶段,可以基于IBIS模型利用HyperLynx仿真软件进行布线前仿真,确定阻抗匹配网路及布线宽度。总线系统采用33 Ω的串行端接,而模拟视频信号线采用75 Ω的AC并行端接网络。

最后,对系统的电源平面和地进行分割,并有效地旁路地和电源上的反弹噪声,在合适的地方增加去耦电容。去耦电容的分布应该尽量靠近去耦芯片,同时尽量在每个电源引脚上均匀分布一个电容。

由于系统是高速信号处理系统,因此在布线前可以利用HyperLynx进行布线前仿真,特别是对系统中的存储模块及网络差分模块进行仿真,确定阻抗匹配网路及布线宽度。在布线完成之后还可以进行布线后仿真,确保系统的信号完整性及减小系统的电磁辐射干扰。

结语

本系统利用TI公司的专用视频处理芯片TMS320DM642完成双DSP多路视频监控系统设计。与传统的多路视频监控系统相比,采用双DSP的多路视频监控系统设计简单,开发成本低,可广泛应用于煤炭、钢铁等工业现场监控的领域。