近年来,视频处理系统的研究受到了人们越来越多的关注,发展也非常迅速。同时,视频技术也是一门跨越很多学科的技术,在此基础上又衍生出了很多的新的技术和研究方向,比如人脸识别技术和图像边缘检测算法的研究以及视频压缩算法的研究等。现在视频处理系统有着广泛的应用,比如交通路口的监控装置、在机场、港口以及一些公共场所使用的视频监控设备等。如果视频技术再和图像处理等技术结合起来,那么其应用的范围和深度都会有很大的提高,比如在安防领域可以用于辅助识别危险目标和恐怖分子等,这些技术在民用领域和军事领域都有着广泛的应用。

针对以上这些应用需求,本文采用TI公司的DM642" title="TMS320DM642" target="_blank">TMS320DM642(以下简称DM642)数字多媒体处理芯片设计了一套视频处理系统。文中主要介绍了系统的硬件设计和调试过程。

1 系统硬件设计方案

1.1 系统的硬件结构

视频处理系统的硬件设计采用的DSP是DM642,它是一款高性能的数字多媒体处理器,最高运算速度可达5760MIPS(每秒百万条指令),可以满足复杂算法的实时处理要求。视频信号需要通过CCD摄像头采集。

视频解码芯片将采集到的模拟信号转换为数字信号供DSP进行运算处理。DM642的视频接口(VP口)共有3个,其中VP0和VP1都是20位,10位用于视频输入,另外10位用于音频输入。VP2口也是20位,可以分为两路视频输入。在本文设计的视频处理系统中,采集到的模拟视频信号经过视频解码芯片模/数转换后,形成BT.656格式的数字视频信号,通过DM642的VP0口输入。

数字信号经过DM642的软件编码器进行编码压缩处理,编码压缩生成的视频码流数据打包后通过RJ-45接口经以太网传送到远端的上位机,上位机作为SERVER,这样就构成监控系统。通过DM642独立多媒体接口(MII),片外连接一片以太网处理芯片,就可以构成10/100 Mbpa以太网模块。本地回放由视频编码芯片来完成。

通过DM642的EMIF接口可以连接SDRAM和Flash存储器。尽管DSP提供了片内RAM,但是在大多数情况下不能满足系统的要求;同时对于要求实时处理的系统而言,又要求尽量减小在数据流动过程中由于存储器读写造成的时间开销,因此在系统中配置了高性能的SDRAM,它在运行程序和数据处理时使用。Flash在系统中主要是用来存放系统软件和配置参数的。

系统的总体框图如图1所示。

在该视频处理系统上集成了相当数量的板上设备以适应不同的应用环境,其主要特点为:

1)系统的运行频率为600 MHzc。

2)2个视频端口:1个为板上解码器,1个为板上编码器。

3)32 MB的同步DRAM空间。

4)2 MB的Flash空间。

5)以太网接口。

6)配有仿真器接口可以用来进行JTAG仿真。

7)供电电压为+5 V。

8)蜂鸣器报警。

1.2 存储器模块设计

在数据处理模块中,DSP芯片、SDRAM芯片和Flash芯片这3块芯片是整个模块电路的核心。该模块的功能是完成与外部数据存储器的数据传输和程序存储器的程序读写任务。通过JTAG接口电路与仿真器相连后接到计算机主机进行仿真调试,实现与目标主机的数据交换。

1.2.1 SDRAM接口设计

在系统的硬件设计中,SDRAM内存芯片选用Micron公司生产的MT48LCAM3282-1Mx32×4 banks。SDRAM,即Synchronous DRAM(同步动态随机存储器),表明它的工作速度是和系统的总线速度同步的。MT48LC4M3282总线最高时钟为166 MHz,它主要用来存储数据和程序,SDRAM的刷新由DSP芯片自动控制。MT48LCAM3282是一款高速CMOS动态随机存储器,它内部配置为4个区的同步接口。

DM642的EMIF可以对SDRAM的地址属性进行编程,它和SDRAM可以实现无缝连接。EMIFA最大的时钟总线可达133 MHz。SDRAM控制器可以支持16 M~256 Mbit的SDRAM芯片。TMS320DM642上的Cache容量有限,所以视频数据通常存放在片外SDRAM中,在需要用到的时候通过EDMA把数据从片外搬移到片内处理,这样就可以提高程序的执行效率四。TMS320DM642的SDRAM接口图如图2所示。

由于TMS320DM642的数据总线是64位,而每片MT48LC4M3282的数据总线是32位,所以需要并联两片MT48LC4M3282才能构成64位的数据总线,这样才可以与TMS320DM642的EMW数据总线相连。参照DM642数据手册中SDRAM的配置方法,EA15、EA16控制SDRAM的组,EA3-EA14控制行地址,EA3-EA11控制列地址,片选信号接到DM642的![]() 上,这样就把SDRAM分配到CE0空间上。

上,这样就把SDRAM分配到CE0空间上。

1.2.2 Flash接口设计

DM642 EMIFA的异步接口为各种存储器和外设类型提供了可配置的存储器周期类型,包括SRAM、EPROM、Flash等,在本系统中Flash采用的是SST公司生产的SST39VF1601 Flash,片选信号接到DM642的![]() 引脚上。当DSP上电后,DSP通过增强的直接存储器访问从外部的CE1寻址空间复制1 K字节的数据传给内部存储空间,然后再从内部存储空间0x0处开始运行,所以Flash ROM必须配置在DSP的CE1空间,在DSP存储器中对应的地址是0x90000000-0x90200000。

引脚上。当DSP上电后,DSP通过增强的直接存储器访问从外部的CE1寻址空间复制1 K字节的数据传给内部存储空间,然后再从内部存储空间0x0处开始运行,所以Flash ROM必须配置在DSP的CE1空间,在DSP存储器中对应的地址是0x90000000-0x90200000。

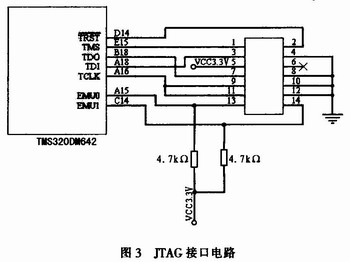

1.3 JTAG接口设计

JTAG接口是调试环境和目标板之间的接口,它的好处是可以让开发者在对目标板进行开发的同时可以不改变目标板的系统结构,从而方便了系统的开发与测试。XDS510仿真器通过JTAG接口将系统板与电脑连接起来,这样就可以使用TI提供的集成化开发环境对系统进行调试了。JTAG接口采用标准的双排14脚插座。系统的JTAG接口电路如图3所示。

1.4 电源模块设计

DM642需要两种电源,一种是内核电源(1.4 V),另一种是I/O电源(3.3 V)。通常由于DM642用于嵌入式系统中,因此电源电路设计不仅要考虑电压精度、稳定度和外围电路的复杂度等问题,还要考虑低功耗问题。另外,根据设计要求,为了保证芯片正常工作,在系统上电作时,对这两种电源的上电顺序还有一定的要求,如果违反该要求,可能降低器件的性能或永久损坏器件。内核电源要比I/O电源早上电,至少不能晚于I/O电源上电。在电路设计中,通过采用在两个电源之间串联二极管的方法来解决系统上电顺序的问题。

系统设计中,电源芯片采用的是TI公司的TPS54310,它是TI公司生产的一款开关电源调节芯片,它能够实现低电压输入和高电流输出(输人电压范围为3~6 V,输出电压根据需要可以在0.9~3.3 V之间调节,输出电流为3 A)。图4是3.3 V电源产生电路,1.4 V电源产生电路与此类似,只需根据TPS54310中的计算公式将相应的电阻和电容值做相应的修改就可以得到1.4 V电源。3.3V的电源不仅是DM642的0电源,同时也是系统上视频解码芯片、视频编码芯片、SDRAM芯片等的供给电源。

1.5 视频输入输出模块设计

1.5.1 视频输入模块设计

视频输入模块设计采用的视频解码芯片是TVP5150APBS,它是TI公司专门开发的一款可以方便携带的低功耗视频解码芯片,可以广泛用于视频系统的设计。TVP5150APBS的视频输入端可以输入两路复合视频信号或者一路S端子信号。输入信号(如PAL、NTSC等制式)通过增益控制单元、模数转换器和Y/C分离及处理模块后,最后可以转化为8位ITU-R BT.656的数据格式,或者转化为8位4:2:2的数据格式。TVP5150A-PBS的初始化操作是通过操作IIC总线来实现的。TVP5150APBS的IIC地址可以通过控制12CSEL引脚的高低电平来设置。当该引脚是低电平时,IIC地址是0xB8h,当该引脚是高电平时,IIC地址则为0xBAh。TVP5150APBS与TMS320DM642的连接示意如图5所示。

从图5可知,视频信号可从TVP5150APBS的AIP1A或AIPIB输入,数据输出引脚YOUT[0:7]与DM642的VP0[2:9]引脚连接在一起。TVP5150-APBS的系统时钟引脚SCLK与DM642的VPOCLK0引脚连接。因为在本系统的设计中采用的是ITU-R BT.656的视频输出格式,所以在系统中不需要分立的同步信号。因此,TVP5150APBS的HSYNC(行同步信号)、VSYNC(场同步信号)、AVID(行消隐指示信号)以及FIDFig.5 Colleetion bet-ween TVP5150APB5 and DM642(奇偶场指示信号)这几个引脚并不需要与TMS320DM642连接, 只需要将TVP5150APBS的INTERQ引脚与TMS320DM-642的VPOCTL0引脚连接起来。

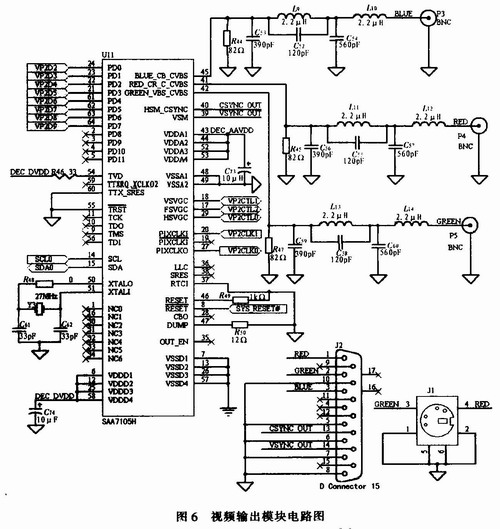

1.5.2 视频输出模块设计

在系统设计中,视频输出模块中的视频编码芯片选用的是Philips公司的SAA7105H,它同时具有SDTV(标准清晰度电视)和HDTV(高清晰度电视)信号编码能力,可以广泛用于视频输出的设计中。视频输出模块的电路如图6所示。

从图6中可知,将DM642的VP2端口配置成视频输出端口。由于VP2端口的数据线与SAA710SH的数据线相互错位,因此这会造成无法正常显示视频输出。为了解决这个问题,在将VP2端口配置成ITU-R BT.656视频输出时,数据就会从VP2 A通道的VPD02-VP2D09输出,VP2D00-VP2D 01则输出无效,因此就需要将VP2D02-VP2D09这8根数据线连接到SAA7105H的PD0-PD7对应的引脚。这样VP2D10-VP2D19在视频回放中就没有使用。

SAA7105H将从DM642端传送来的PC信号转化为PAL制式(50 Hz)或者是NISC制式(60 Hz)送到外部TV端输出。SAA7105H默认为休眠状态,在休眠过程中HC总线仍然可以接受来自DM642的命令。当SAA7105H的3个数模转换器视频输出与外部TV相连接时,SAA7105H能够自动检测到数模转换器接口的阻抗变化,然后通过芯片的TVD(电视信号检测)引脚向TMS320DM642发出中断请求,表明外部有播放要求。此时,DM642就会通过IIC总线来配置SAA7105H的内部寄存器,激活还处于休眠状态的SAA7105H,开始进行本地视频的播放。

在视频输出模块中,SAA7105H的HSVGC(水平同步输出)、VSVGC(垂直同步输出)、FSVGC(帧同步输出)分别于TMS320DM642端口的VP2CTL0、VF2CTL1以及VP2CTL2这3个引脚相连。SAA7105H的输出方式可以有RGB格式、CVBS(混合视频)格式、S-Video格式以及VGA格式等几种。其输出方式的选择通过SAA7105H的应用子地址来控制。

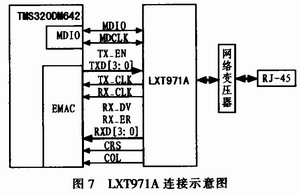

1.6 以太网接口设计

以太网接口设计中的以太网处理芯片采用Intel公司的LXT97lA,它符合IEEE标准,直接支持10 Mbps和100Mbps的双绞线应用,也可以支持100 Mbps的光纤接口。LXT971A与DM642的连接示意图如图7所示,在以太网模块中还需要用到网络变压器和RJ-45以太网连接器。

1.7 报警电路设计

系统的报警电路结构比较简单,它由驱动电路与蜂鸣器构成,驱动电路与DSP的一个GPIO引脚连在一起,电路如图8所示。

从图8中可以看出,当GP10输出高电平(通知报警)时,三极管的集电极和发射极之间将视为短接,从而驱动蜂鸣器发声报警,系统设计中采用的是有源蜂鸣器来进行报警。

2 系统调试

2.1 Flash的调试

Flash调试的步骤如下:

1)配置寄存器,Flash的基地址是0x90000000,共有512个扇区,每个扇区有4 K字节,Flash的大小为2M字节。将Flash的空间映射到TMS320D-M642的存储器空间内;

2)进行Flash的擦除操作;

3)判断擦除操作是否结束。Flash的DQ6位和DQ7位都可以用来判断擦除是否结束,这里采用的是DQ7位。在内部擦除操作过程中,读出的DQ7的值是“0”,一旦内部擦除操作完成,DQ7的值就会变化为“1”;

4)开始Flash的写操作和读操作。

可以通过CCS的Memory窗口可以观察Flash的写入是否正确。读出的数据和写入的数据经过对比后无误,说明系统的Flash工作正常。

2.2 SDRAM的调试

两块SDRAM芯片MT48LC4M3282的片选信号是与TMS320DM642的![]() 引脚接在一起的,因此SDRAM的基地址是Ox800000000。在测试SDRAM时,从SDRAM的基地址开始,长度为32 M字节。在编程时向SDRAM中写入数据。然后再读出数据,将读出的数据与写入的数据进行对比,测试后对比无误,说明系统的SDRAM工作是正常的。

引脚接在一起的,因此SDRAM的基地址是Ox800000000。在测试SDRAM时,从SDRAM的基地址开始,长度为32 M字节。在编程时向SDRAM中写入数据。然后再读出数据,将读出的数据与写入的数据进行对比,测试后对比无误,说明系统的SDRAM工作是正常的。

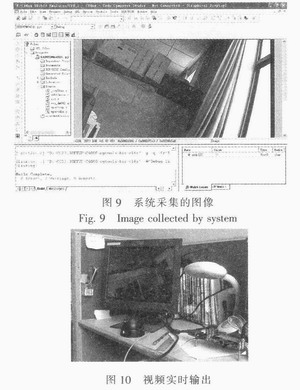

2.3 静态图像的采集

在图像采集中用到的是TMS320DM642的VP0口,需要一个CCD摄像头。采集到的静态图像通过CCS的View功能来显示。

视频解码芯片TVP5150APBS的IIC地址设置为0xB8。另外,在程序中还需要对TVP5150APBS相关的寄存器进行必要的设置以满足系统的要求。编写图像采集程序,TVP5150APBS能够实时采集图像。程序在CCS中经过编译、运行后采集到的图像如图9所示。

2.4 视频显示的调试

视频显示模块主要是在图像采集的基础上实现VGA制式视频图像的实时显示。在调试过程中需要编写视频接口的显示驱动程序以及整个视频显示通道的调试程序,还需要对视频编码芯片SAA7105H的寄存器进行设置。视频输出信号通过VGA接口连接到显示器上,这里采用的是电脑显示器。调试程序经过编译、运行后,会将TVP5150APBS采集到的图像通过SAA7105H送到显示器实时显示出来,如图10所示。

2.5 报警模块的调试

在调试时通过编程将GP10引脚设置为“1”,即给报警电路输入一个报警信号,此时蜂鸣器将会发声报警。

2.6 以太网模块的调试

以太网模块的调试主要是测试EMAC与MDIO的配置及使用,以及如何配置一个PHY设备和CSL库中关于网络接口部分程序的应用。在调试过程中,是采用自闭环的方式来完成的。

将系统板上的RJ-45网络接口用网线和局域网连在一起,在调试中需要用到TI推出的TCP/IP NDK(Network Developer's Kit)开发套件中提供的调试程序。程序运行后,系统板可以和局域网中的电脑正确地进行数据传输,说明系统的以太网模块是可以正常工作的。

3 结束语

系统研究并实现了一个通用的基于DM642的视频处理系统。该系统已经调试成功,它可以完成视频信号的输入与输出,可以应用于视频图象采集和处理的各种场合中。系统还扩展了一个网口,可以方便地与外界通信。与传统的视频处理系统相比,该系统在视频输出方式上更趋多样化,视频输出接口既可以接到电视机上,也可以与PC机的显示器相连接,弥补了以往接口单一的缺陷。系统新增的报警功能增强了系统的实用性。下一步研究的方向是对该系统做进一步的完善,比如可以增加USB接口,扩展系统的应用范围,将蜂鸣器报警改为语音报警等。最后,在此系统上研究各种算法,比如视频压缩算法、图像处理算法等,这样它可以应用于视频会议、交通、监控等诸多领域,具有广泛的应用前景。