数字和模拟无处不在! R2R 架构与电阻串 DAC 架构的区别何在?

2009-01-06

作者:Georg Haubner

当我们在专门研究模数转换器 (ADC)、运算放大器 (Op Amp)、数模转换器 (DAC) 以及其他电子架构的工程类院校修完其主干课程以后,您可能会认为您已理解了这些电路的所有基本功能。大多数人均对 ADC 的工作原理有了一个很好的了解,但是对 DAC 的工作原理却不太熟悉,它究竟有何功能呢?同样,对于大多数人来说,DAC 只不过是一个输入端为数字信号数据而输出端为模拟信号数据的“黑匣子”。只有为数不多的人知道其在架构方面的区别,以及与 R2R 梯形架构相比一个电阻串架构 (string architecture) 所具有的优点和缺点,反之亦然。了解他们之间的不同之处并了解这些通用 DAC 的工作原理可以使设计人员为其应用选择最佳的 DAC。

本文将对 DAC 的基本工作原理进行阐述,并对您一直想知道的一些问题做出解答。

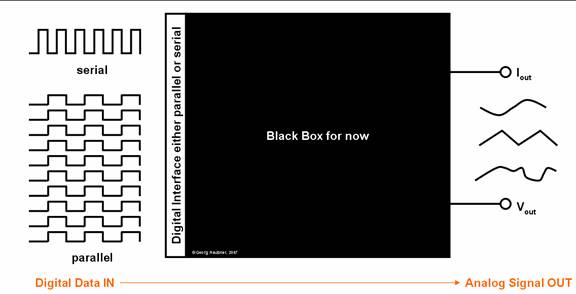

由于 DAC 通常被视为一个输入端为数字信号数据而输出端为模拟信号数据的“黑匣子”,所以在这一点上我就不多说了。数字数据可以是串行数据格式也可以是并行数据格式。串行接口(例如,对数字数据流进行串行传输的 SPI 或 I2C 接口)就像是一个进入“黑匣子”的项链或链条,而并行接口会将一个时钟周期中所有的必要的比特数加载到该器件中。在该器件的另一端,模拟输出信号为是一个电压或一个电流,请参见图 1。

图 1 数模转换器的主要功能

不同的输入接口所提供的数据格式也有所不同,所以在速度、引脚数量、芯片面积、器件尺寸以及灵活性上都有很大的不同。然而,这两种接口(串行接口或并行接口)均可以将数字数据输入到该器件中。

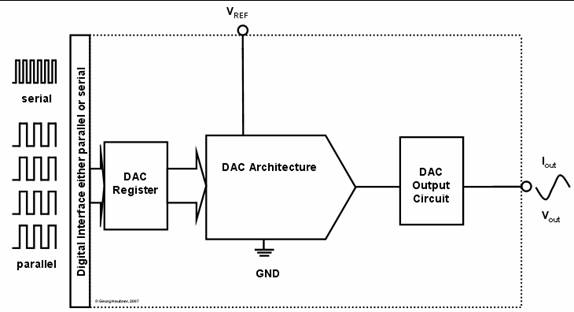

一旦数字数据被输入到黑匣子(第一个功能块),那么输入寄存器就会像串行-并行转换那样工作,或者在多通道器件中对该数据进行存储,直到该数据被传输至单个 DAC 寄存器中。在输入寄存器和 DAC 架构之间起连接作用的 DAC 寄存器将起到一个存储器的作用,并对数字数据加以存储。

在 DAC 设计之初,该 DAC 寄存器为一个保存数字数据的外部存储器。如果没有 该 DAC 寄存器,那么由于模拟电路的实时馈入,DAC 的输出将随着外部输入总路线的任何变化而立即发生变化。在用户决定用新代码更新 DAC 寄存器之前,该数据会一直驻留在 DAC 寄存器之中。DAC 寄存器主要起到了一个触发电路的作用。

图 2 基本的功能块

架构

当今的高精度 DAC 主要采用了两种架构:R2R 架构和电阻串架构。这两种架构均为采用了一些数字控制逻辑的模拟电路。通过一款基本的 R2R 架构,就有可能生成一个电流输出或电压输出;而电阻串架构只能利用一个输出缓冲器生成一个电压输出,如图 2 中的输出电路结构图所示。在电流输出的情况下,没有实施输出缓冲器。

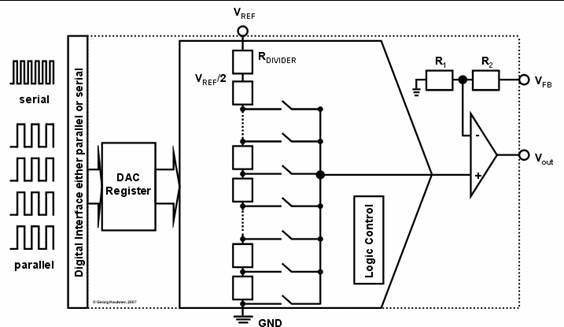

电阻串架构

顾名思义,电阻串架构就是一个以串联形式放置的一串电阻,以构建一个电阻串。从理论上来说,您可能会需要 256 个电阻才能构建一款 8 位 DAC (28 = 256),(请参见图 3 )。

图 3 主要的电压输出电阻串架构

提高精度也就是说要增加所需电阻的数量以构建一个电阻串 DAC。对于一款 16 位DAC 而言,可能需要65,536 个电阻才能生成所有可能的电压/数字阶跃 (step)。但是,在现实真正的设计中,在一颗芯片上实施近 66,000 个电阻是不切实际的,对于当今的小封装,低功耗和低成本要求而言尤为如此。因此,设计人员推出了其它更小的电路设计方案,如可降低电阻串上所需电阻数量以及接触点的内插式放大器,从而实现了功耗更低且更节省空间的设计。该内插式放大器用来代替输出缓冲器。当今的一些电阻串架构拥有一个可用作放大器外部反馈环路的引脚。

图3 显示了一款包含了内部输出缓冲器的电阻串架构,该缓冲器可生成相当于数字输入代码的电压输出。

由于特定的电阻串架构,电阻串 DAC 具有低成本和保证单调性能的优点。值得一提的另外一个很重要的优点是可以实现小型封装的低功耗和小裸片面积,从而使他们非常适合便携式应用。其另外一个优点是输出缓冲器已经包括在该架构之中,从而无需使用更多的板上外部组件。其次,该输出缓冲器还实现了内部电阻和模拟电路与外界的隔离,这在低阻抗电路中非常有用。许多应用都要求低突波能量,这也是电阻串架构的另外一个优点所在。

另一方面,由于电阻串设计的更高阻抗,所以其噪声通常会高于 R2R 架构的噪声。设计人员还应该清楚地知道有限的精度(亦称为积分非线性 (INL))。较早的设计通常在中-60 最低位 (LSB) 提供 INL 数字,而较新型的一些设计则利用改进的工艺技术,现在可以在 4LSB 区域提供典型的 INL 数字。对于诸如马达控制或过程控制的许多闭环应用而言,一个典型的 4 LSB INL 就已经足够了。然而,对于其它应用而言(如:自动测试设备),这还远远不够,那些应用通常需要1 LSB INL。因此,就有了另外一种不同的架构:R2R 架构。

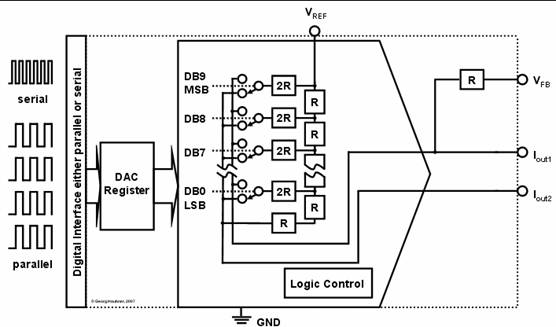

R2R 架构

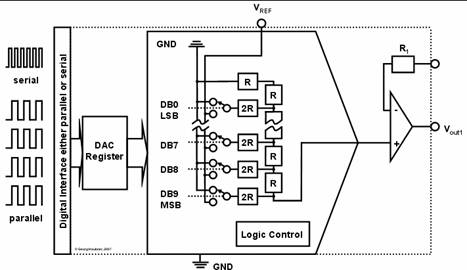

R2R 架构主要是由形成一个电阻梯形的并联电阻组成。图 4 显示了一种可能的 R2R 梯形,这是一款乘法 DAC (MDAC),其 R2R 梯形的顶部与外部参考电压相连。访架构可以输出一个相当于数字输入代码的电流。

图 4 主要的电流输出 R2R 架构

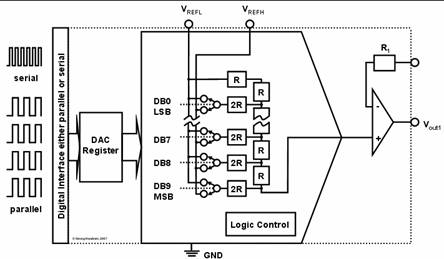

在硅片中实施一个 R2R 梯形的另一种方法如图 5 所示。其外部参考电压没有和 R2R梯形直接连接。根据不同的数字输入代码,开关将通过 R2R 网络把参考电压或接地电平连接至输出缓冲器,该输出缓冲器将所生成的电压信号转换成输出电压。

图 5 主要的电压输出 R2R 架构

图 5 所示的架构只允许从 0V 到应用外部参考电压的单极输出电压(请注意,DAC 的电源电压必须等于或高于参考电压)。通过将接地电平连接至一个额外的外部负参考电压可以对后来提及的架构进行修改,而通过修改该架构则可以实现双极运行。图 6 显示了修改后的架构。此种类型的架构还可用于选择灵活的参考电压。虽然 VREFL 可以为负电压,但不需要让其为负电压。但是,VREFL 必须要低于 VREFH。详尽的描述与参数请参见现有的产品说明书,如:DAC7714 [1]。

图 6 主要的双极 R2R 架构

R2R DAC 具有低噪声和高精度的优点,其可能会提供 ±1 LSB INL 的卓越精度和DNL 性能。而且,该架构可实现高电压输出,MDAC 拥有较快的建立时间(小于 0.3 μsec),以及大于 10 MHz 的乘法带宽。一般而言,其他 R2R 拓扑结构仅拥有中等的建立时间性能。

对于更宽泛的应用范围(如数控校验或工业可编程逻辑控制 (PLC))而言,MDAC 在使用设计人员所选择的外部输出缓冲器方面的灵活性使该架构类型更为有用。设计人员可以为特定的应用挑选最佳的运算放大器。另一方面,对于板上器件数量不断增加的低阻抗连接而言,需要一个外部缓冲器。其次,与 R2R 架构相比,突波能量当然更适合电阻串架构,因此,对于波形生成和其他突波能量敏感型应用而言,很少采用 R2R DAC。

结论

我们不但要考虑诸如增益误差或偏移误差等其他电气规范,而且还要考虑随着温度变化而发生的漂移或满量程误差等重要的参数,这些参数通常与具体的架构无关。为了有一个良好的开端,设计人员应首先查看基本要求并问问自己对最低精度和线性度有何要求。如果是在闭环应用中,那么一款较低成本且线性较差的电阻串 DAC 就足够了;而如果是在开路应用中,则 R2R 架构在提供更佳的线性度和更高的精度方面就显得更加出色。

参考书目

[1] TI 《DAC7741 产品说明书》,网址:www.ti.com/sc/device/dac7714

[2] TI 《放大器和数据转换器选择指南》(修订版 B),网址:http://focus.ti.com/lit/ml/slyb115b/slyb115b.pdf

[3] TI 《数模转换器产品规划》,网址:www.ti.com/dataconverters