摘要:提出了一种基于SOPC技术的数据采集和存储系统的解决方案。该系统通过在一片Xilinx公司Spartan 3E系列的FPGA芯片上配置micro-blaze软核处理器、用户自定义的数据采集与存储接口逻辑、USB传榆模块和总线接口模块来实现其硬件电路。该数据采集系统可同时对多种信号进行测量,有较大的存储容量。由于采用了SOPC技术,该系统具有设计灵活、集成度高,以及较小的体积和较低的功耗等优点。

关键词:Microblaze;数据采集与存储;SOPC;FPGA;IP核

随着集成电路的不断发展,可编程逻辑器件FPGA因其功能强大,设计灵活,开发周期短等特点,得到越来越广泛的应用。于是片上可编程系统(System On Programmable Chip,SOPC)的设计方法也越来越受到重视。SOPC将微处理器、存储器、定时器、通用I/O接口等系统设计必需的功能模块以及用户设计的有特定功能的模块集成到一片可编程逻辑器件上,构建一个具备软,硬件在系统可编程功能的可编程片上系统。这种非常灵活的电路设计方式使得对整个电路系统的裁减、扩充、升级变的很容易。这样可以缩短电路设计的开发周期,节省开发成本。MicroBlaze作为Xilinx公司开发的32位哈佛结构RISC型软核处理器,适用于其所有现产的FPGA器件。采用这种“微处理器+可编程逻辑”的SOPC系统架构,用户可方便的在系统中加入各种IP核,实现具有特定功能的,易配置、易扩展、易继承的片上系统。

文中提出一种基于SOPC技术的多路数据采集与存储系统的设计方法,利用硬件描述语言设计用户IP核,实现硬件控制数据采集和存储的功能。加上Xilinx公司一些必要的标准IP核可以生成嵌入式系统。这种可以方便地把用户自定义的逻辑加入到系统中的设计,体现了用SOPC设计嵌入式系统的灵活性。

1 系统总体结构

整个系统由Xilinx公司的Spartan3E高性能、低成本的90nm FPGA和一些外围电路组成。主要有AD转换器、FLASH存储器、系统PROM配置电路和电源模块等,其系统总体结构如图1所示。

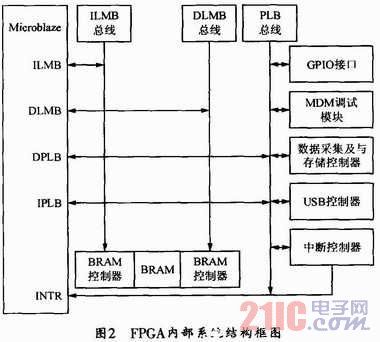

系统核心采用嵌入式技术,在一片芯片上实现,它包含Xilinx公司的一些标准总线IP核如中断控制器,通用输入输出端口等模块和带有PLB总线接口的用户自定义的数据采集与存储IP核。其中用户自定义的IP核是用VHDL语言设计的,它包含AD控制逻辑、FLASH控制逻辑、DMA传输控制逻辑和FIFO缓存模块等。

整个系统设计可以分为硬件设计和软件设计两个部分。利用SOPC技术结合VHDL硬件描述语言,在芯片内部设计硬件控制系统;利用EDK(嵌入式开发套件)为特定硬件配置自动生成的软件包结合C语言,设计基于Microblaze处理器的软件控制程序。

2 系统结构

FPGA的硬件设计先确定要用的外部接口,然后进行IP核设计,将IP核的逻辑功能映射到FPGA芯片上。其系统结构框图如图2所示。

2.1 AD转换芯片

AD转换器采用MAXIM公司的MAXIM1308芯片,它是12位模数转换器(ADC)提供8个独立输入通道,独立的采样保持(T/H)电路为每个通道提供同时采样,提供+5V输入范围,20MHz、12位双向并行数据总线用来提供转换结果,并可接受数字输入来单独配置每一通道的开启和关闭。

2.2 FLASH存储器

FLASH存储器芯片采用8片三星公司的K9XXG08UXA系列的NAND Flash存储器,该存储器是按页进行读写按块擦除,通过I/O管脚分时复用发送命令/地址/数据。每片的存储容量为512MB。存储过程使用流水线方式对数据进行存储。

2.3 FPGA配置电路

Xilinx公司的FPGA器件是基于SRAM的内部结构,掉电后FPGA的内部逻辑丢失,因此外部需要一个配置芯片在每次上电时可以将配置数据加载到FPGA器件的内部SRAM中。配置芯片采用的是XCF04系列PROM串行配置芯片。当系统上电时,芯片以主动配置方式来实现系统中FPGA的硬

件配置。通过高速的串行接口,整个芯片的配置工作可以在很短的时间内完成。

2.4 系统电源模块

电源模块的设计不仅需要为器件提供各种高性能的功率输出,还要包括选择合适的旁路、去耦电容,以滤除各种干扰信号,保证系统的稳定工作。Xilinx公司Spartan-3E XC3S500E FPGA需要三种电压供电才能正常工作:VCCAUX:1.2V±5%,VCCAUX:2.5V±5%,VCCO:3.3V±5%。利用TI公司TPS75003芯片加上必要的外围电路作为该系统的完整的电源解决方案。

2.5 USB接口芯片

USB芯片使用由FTDI公司推出的FT245R,该芯片主要完成USB串行总线和8位并行FIFO接口之间的相互协议转换。整个USB通信协议全部由芯片自动完成,无须考虑底层固件的编程。该芯片可以使用内部集成的时钟电路进行工作,也可以使用外部晶振,本系统中使用外部晶振。完全兼容USB2.0协议。它有256字节的接收缓冲区和128个发送缓冲区,可以进行数据的大吞吐量操作。通过8位并行数据口D[0:7]和4位读写状态/控制口RXF、TXE、RD、WR就可实现与微控制器的数据交换。

3 FPGA系统硬件设计

Xilinx公司EDK(嵌入式开发套件)的XPS(平台工作室)的系统组建面板以展开式的树和表形式显示所有硬件平台IP实例,因此用户可以方便地查看自己的嵌入式设计。在此面板中可以对IP元素、端口、属性以及参数进行配置。

3.1 用户IP核设计

使用XPS进行基于MicroBlaze的用户IP核的开发,该套件集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。

为实现系统功能,需自定义一个IP核实现数据的采集与存储:该IP核包括五部分,分别为PLB总线接口模块、数据采集模块、数据缓存模块、数据存储模块FLASH读写控制逻辑。

(1)数据采集模块:利用FPGA逻辑资源实现A/D采集电路的控制逻辑。在功能上,该AD控制逻辑相当于一个主控制器。该控制过程无需处

理器参与。另外AD控制逻辑与AD数据接口的分离,使得高速采集与发送数据成为可能。它连接两片12位的8通道MAXIM1308转换器,可实现多通道的数据采集。

(2)数据缓存模块:在FPGA内部设计FIFO将AD转换后的数据暂时存放其中。FIFO是Xilinx以FPGA片上Block ram为资源生成,FIFO模块的主要功能是数据缓冲,实现速率匹配。该异步FIFO模块在FIFO读、写控制模块的控制之下进行异步读写,FIFO的读时钟受数据存储模块控制,写时钟受数据采集模块的控制。FPGA内部设计了两片12位的FIFO与上述两片AD转换器相对应。

(3)数据存储模块:对本系统使用VHDL语言专门设一个DMA控制器来连接FIFO缓存和外部FLASH存储阵列。当FIFO缓存容量达到一定的值时可以启动DMA控制器建立一个高速的通道以提供连续的数据传输,存储到FPGA外部FLASH存储器阵列。这个通道使得只要FIFO缓存中的数据达到一定的值时便能迅速地存储到外部FLASH中,主设备不必为了确定从端口是否能够发送或接收数据而不断地访问从外设的状态寄存器。这使得系统的整体效率有了较大的提高,同时避免了自定义外设FIFO中的数据上溢或下溢。并且该过程只需要Microblaze处理器很少的干预即可完成,极大地节省了CPU资源。

(4)FLASH读写控制逻辑:主要实现K9XXG08UXA系列的NAND Flash存储器的读写时序,完成对FLASH的操作。

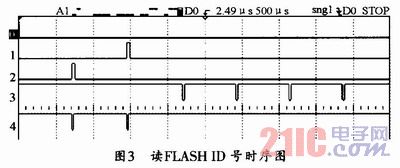

在SOPC硬件系统设计过程中用户IP核的设计是关键,它的设计是否成功决定着整个系统设计是否可行。在用户IP核设计过程中AD控制器、FLASH控制器、DMA控制器的设计都比较成功的,图3是对用户IP核设计的部分验证:示波器捕获的读FLASH存储器ID号时序图,且实验证明读出来的FLASH存储器的ID号是正确的。其中通道0—4分别代表FLASH的CE(片选)、ALE(地址锁存)、CLE(命令锁存)、RE(读)、WE(写)信号。

3.2 设计生成FPGA硬件系统

在XPS嵌入式开发环境中将用户IP核和标准总线核添加到系统中并将它们互相按规则连接起来。XPS提供了一个交互式的开发环境,允许用户对硬件平台各个方面进行设置。其中,XPS在高层对硬件平台描述进行维护,此高层形式即为微处理器硬件规范(MHS)文件。MHS文件作为一个可以编辑的文本文件,是表示用户嵌入式系统硬件部分的主要源文件。XPS将MHS文件综合到硬件描述语言网表中,用于FPGA的布局布线形成FPGA系统的硬件结构,该过程即是生成硬件比特流的阶段,形成后缀名为.bit的文件。

4 结束语

本文介绍了基于SOPC的多通道数据采集系统设计,可以对多种关心的环境参数进行采集并研究其特性。利用MicroBlaze微处理器搭建数据此采集与存储的嵌入式可编程片上系统,可以由单个芯片完成整个系统的主要逻辑功能。便于系统实现小型化,集成化。这种灵活的设计方式可随意扩展系统功能。在此基础上嵌入操作系统,可以进一步开发功能更强大的实时数据采集设备。