关键字:电子技术 FPGA ROM

随着电子技术发展,电子电路的形式趋向复杂化,面对这一状况,人们已经清醒地认识到,要分析和设计复杂的电子系统人工的方法已不适用。依靠传统的实验教学已远不能满足社会对高新技术人才的培养需要。本文就一个综合性的实例“音乐播放控制电路”的设计过程具体说明了FPGA在电子电路设计中所起的作用。

1 总体方案的设计

设计一个具有3个八度音程的电子音乐自动循环播放电路,具体曲目可以由设计者自由编辑,以简谱的二进制编码形式存放在ROM的数据文件中。

设计要求如下:

(1)采用5位二进制码表示音高信息,曲谱码存储器的地址由时值计数器控制,计数频率按乐曲的演奏速度选择,每个脉冲周期是所选曲谱中最短音符的时值。存储器在时值计数脉冲作用下顺序输出音高码控制分频器。

(2)采用20 Hz~20 kHz的音频脉冲信号控制蜂鸣器,可以使其根据控制信号频率发出不同的音调。

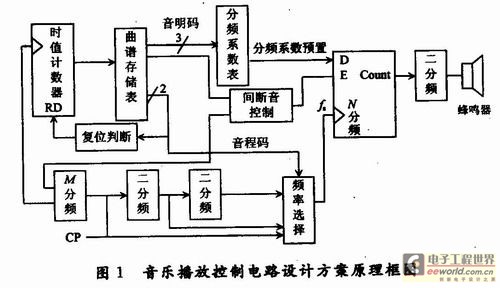

音乐播放控制电路设计方案原理框图如图1所示。

2 设计任务分析

2.1 音高编码和分频控制

计数器模值控制的方法很多,改变预置数控制模值是比较简单的一种。分频计数器的预置数与分频率和计数方式、预置方式有关。当采用减计数器、并以计数器的溢出信号(Carry Out)实现异步预置控制时,计数器的模(分频率)等于预置数。比如,当计数脉冲频率为10 MHz时,若希望产生音高“5”,并考虑占空比整形的二分频作用,分频系数(计数器的模)应该是3 188.9,四舍五入后的计数器预置数应该是3 189。其溢出信号的频率为3 135.8 Hz,控制蜂鸣器的信号频率为1 567.9 Hz,满足音高频率要求。若采用同步预置方式,则计数器的预置数应该是模减1,为3 188。由于计数器的溢出信号可能出现冒险干扰,采用同步预置的方法比较安全。

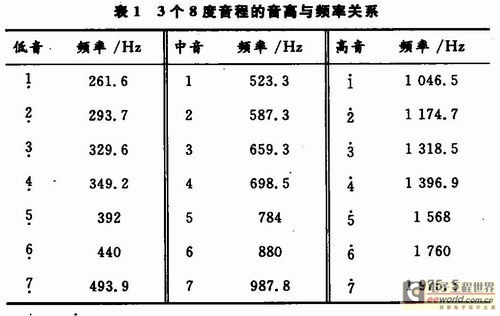

分析表1可见,表中3个不同音程相同音名(同一行)的信号频率都相差一倍。

即音程升、降8度时,频率增加或减小一倍。所以,若分频计数器的计数脉冲频率降低一倍时,蜂鸣器发出的音调降低8度。比如,当分频率仍为3 189,但计数脉冲频率为5 MHz时,控制蜂鸣器的信号频率为784 Hz,为中音“5”。

因此若采用模值和输入脉冲频率都可控的计数器实现信号分频,可根据音程码选择分频计数器的输入脉冲频率fs、根据音名码控制分频计数器的模值N,如图2所示。

这样,分频系数表只需考虑7个音高。由于计数脉冲只能分频降低,所以表中应该存储高音程7个不同音名对应的计数器预置值,其他两个音程可通过降低分频计数器的脉冲频率实现。

3个8度音程的21个音高至少需要5位二进制码表示。为了控制方便,考虑将音名和音程分别编码:7个音名和休止符采用3位二进制码表示,控制分频器计数器的预置数实现模值N修改;3个音程用2位二进制码表示,控制分频器的计数脉冲频率fs。

2.2 音长控制

曲谱存储单元的数据输出时间是时值计数脉冲的一个周期,决定了该单元音符的持续时间。所以,与计数脉冲周期相同时值的音符为音长的度量单位,其音符码占1个存储单元。其他音符根据其时值长短占据不同数量的存储单元。比如,若以8分音符的时值作为存储器地址计数器的脉冲周期,则8分音符码占 1个存储单元,4分音符占2个存储单元,2分音符占4个存储单元,以此类推。

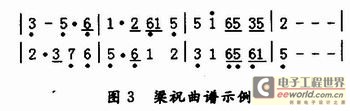

因此,可以所选曲谱的最短音符作为时值的度量单位。比如,图3所示的《梁祝》曲谱中最短的音符为8分音,若其编码存放1个存储单元,则时值计数脉冲周期为一个8分音长时间,可选O.5 s。曲谱中的四分音符码需要存放2个单元,一拍延长音也需要2个单元。该段曲谱有8个音节,每个音节是一个全音(8个8分音),演奏总时值为8×8个8分音。所以,存储曲谱编码的存储器需要64个存储单元。

2.3 音强控制

音的强度也称音的力度,体现了乐曲的情感元素。由于本设计实现的是简单的电子音乐播放,无法表现音强的不同。而且,参考方案还不能区别相同音高的音符连续与否。比如,两个八分音符“11”的总时值与一个四分音符“1”的时值相同,但体现的乐声是不同的。前者是两个强8分音,而后者可以认为是一个强8分音和一个弱8分音构成。为了解决这个问题,可以在连续的相同强音间加一个极短促的间断区别两者的不同,间断时间可以是几个毫秒。这样,在音符编码中应该有一位码控制。

如果间断音码单独占1个存储单元,可设置间断音标志,控制时值计数器状态为间断信息单元地址时计数频率改变,使间断码输出的时间为间断音长;如果间断音码与强音码存放同一单元,可触发数字单稳态电路产生问断控制信号EN。

2.4 乐曲的循环播放控制

为了实现乐曲的循环播放,应该在乐曲结束时使曲谱表的查表地址回到初始值。可在曲谱表的最后一个单元中存放一个结束符,结束符的编码可以利用音程码的冗余码。电路采用逻辑门对音程码进行判断,当出现结束符码时控制时值计数器复位,乐曲重新开始演奏。

2.5 曲谱编码举例

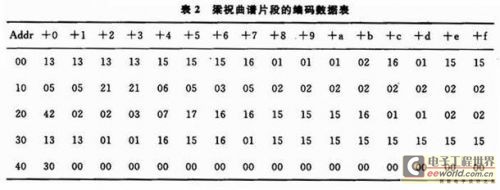

设音符的6位二进制编码中,最高位为间断音控制,中间2位为音程码,最低3位为音名码。每个8分音存放于1个存储单元,四分音符码占2个存储单元。若音名码用其简谱数符对应的二进制码表示,而低、中、高三个音程分别用"01”,“00",“10”三组码表示,“11”为结束符码,则图3曲谱码存储表如表2 所示。表中6位二进制音符码用2位八进制数表示。

3 电路的实现

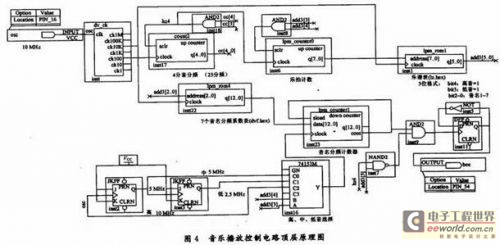

根据设计电路原理框图,曲谱码以分频数编码,音高信号分频由一个可预置的模N计数器实现。分频系数表和曲谱表都存储在ROM中。若希望控制蜂鸣器的信号占空比为50%,分频器的输出信号采用二分频电路实现占空比整形,但注意信号频率被降低一半。电路原理框图中M分频器的作用是产生合适的时值计数脉冲频率。电路的顶层原理图如图4所示。

4 结语

FPGA技术已成为电子系统设计领域现代化的标志。本文将FPGA用于电子技术课程设计,取得了较好的效果。通过本设计激发了学生学习的兴趣,拓宽了学生的思路,为学生今后的毕业设计和从事电子技术方面的科研、开发工作打下了良好的基础。