1 引言

随着微型光谱仪快速发展,CCD和PDA广泛使用,CCD和PDA的种类型号越来越多,每种型号都需要专门的驱动采集板,使得开发产品周期长、费用大。这里提出一种基于FPGA和USB的通用CCD采集系统设计方案。该系统在不改变硬件的情况下可以采集多种CCD,并上传至PC机,使用软件处理采集到的数据。

2 通用CCD采集系统设计

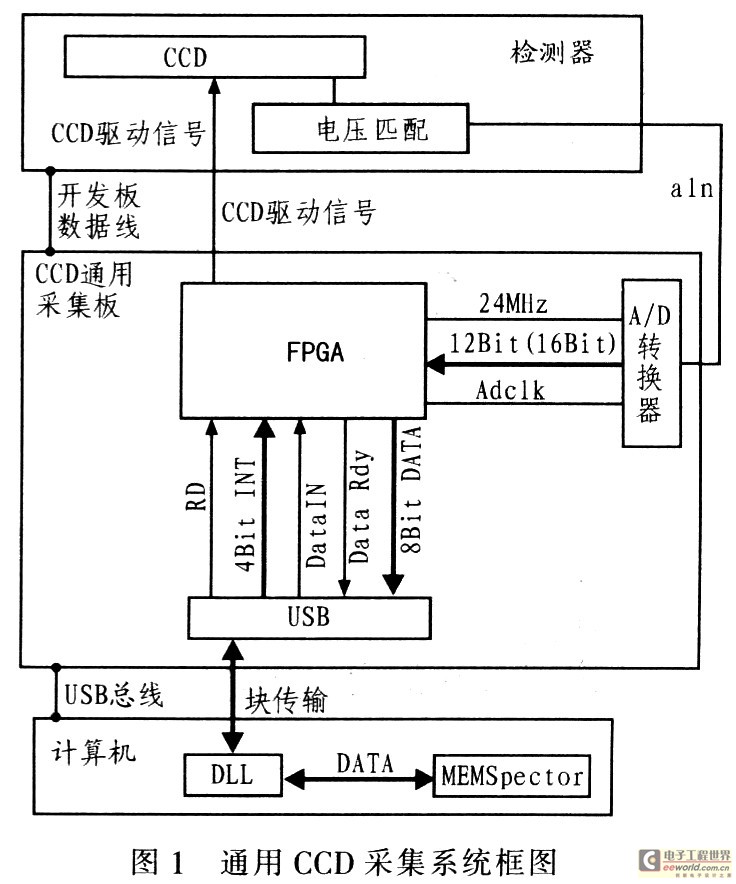

系统部署图如图1所示。系统硬件分为接口板、通用驱动采集板、计算机。接口板匹配驱动信号,将CCD输出视频信号通过前置处理后链接到CCD通用采集板。在CCD通用采集板中,A/D转换器对视频信号进行模数转换后,按帧暂存在FPGA内的FIFO中,通过USB快速块传输模式上传到计算机中.最后计算机软件MEMSpector处理并显示采集到的谱线。

通用性是由通用CCD驱动模块和16In8Out异步FIFO实现的。根据不同类型的CCD编制不同的CCD驱动模块,采用16In8Out异步FIFO,FIFO根据CCD驱动模块提供的FS帧同步来确定暂存A/D转换一帧像元数,实现了采集A/D转换数据与USB传输的分离,在修改或升级CCD驱动时,无需修改采集和数据输出代码,实现了通用性。

2.1 CCD接口板

由于大多数CCD管脚不兼容,视频输出电压也不同。CCD接口板提供CCD插座和转接CCD驱动信号以及输出信号电压匹配。CCD接口板是各种类型CCD链接到通用CCD采集板的纽带。

2.2 通用驱动采集板

通用驱动采集板由A/D转换、FPGA(通用CCD驱动器模块和16In8Out异步FIFO模块)、USB 3部分组成。A/D转换部分完成系统的A/D转换;FPGA部分完成系统的CCD驱动、数据采集、CDS实现;USB部分完成数据的传输。

2.2.1 A/D转换部分

系统需采集多种CCD并实现CDS,而且系统主要由USB供电,这就要求A/D转换速度快,供电电压低,最好参考电压内置。AD9235-40属于12位、40 MS/s模数转换器系列,采用3 V单电源供电,该系列均内置一个高性能采样保持放大器(SHA)和基准电压源。AD923540采用多级差分流水线架构,内置输出纠错逻辑,在40 MSP/S数据速率时可提供12位精度,并保证在整个工作温度范围内无失码。

FPGA中采集信号发生器提供A/D采集时钟,同时也控制FIFO和CCD驱动器。A/D采样速率不再受数据传输和采集制约,采样速率完全和CCD速度匹配。并可实现1帧内1个像元的双采样,从而实现CDS。

2.2.2 FPGA部分的通用CCD驱动器模块

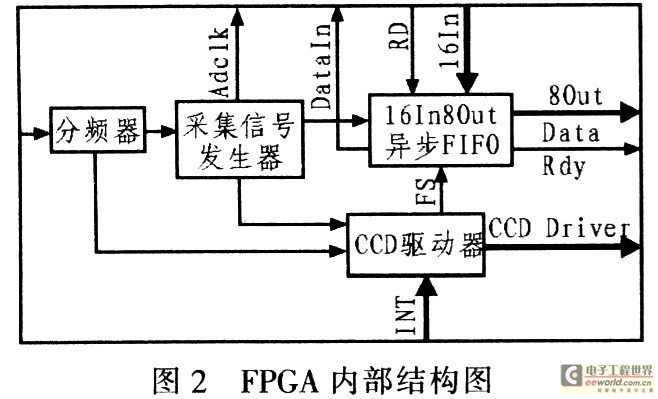

由于不同生产商的CCD器件的驱动时序往往差别很大,因此需针对每种CCD器件编制其CCD驱动器模块。驱动时钟和采集脉冲由分频器和采集信号发生器提供,如图2所示。

CCD驱动器输入信号由两路驱动时钟和积分时间控制信号INT组成;输出信号由帧同步信号FS和CCD Driver信号组成。不同的CCD驱动器模块仅CCD Driver信号有所不同,其他接口一样。在改变CCD时只需替换CCD驱动器模块即可。

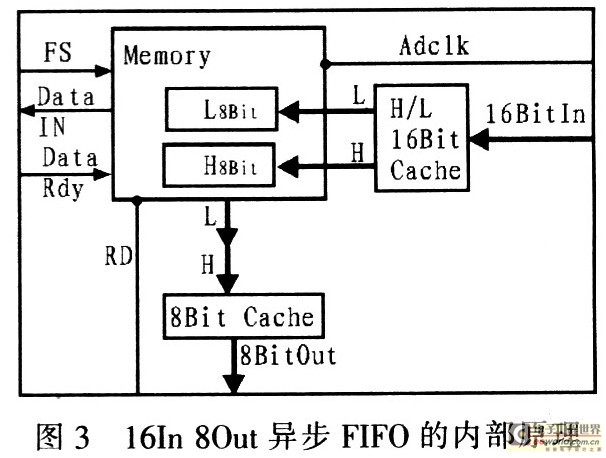

2.2. 3 FPGA部分的16In8Out异步FIFO

FIFO用于暂存A/D转换的信号。待存满1帧并且USB块传输空闲后,将FIFO中的1帧数据通过快速块传输上传至计算机。1帧的像元个数由CCD驱动模块提供的FS信号决定。FIFO内的存储空间为192 Kb。满足线阵CCD和小型面阵CCD的数据存储需求。图3为16In8Out异步FIFO的内部原理图。

图3中,FS是帧同步,在FIFO中重置暂存指针,DataIN是暂存数据采集完毕信号,DataRdy是判断USB是否空闲信号,ADclk是FIFO的写信号,16BitIN是FIFO的读16位入口,读取A/D信号,这里兼容16位,本设计只用12位,其他4位空闲。8BitOUT是FIFO的8位输出口,RD是FIFO的读出时钟信号。在FIFO中读入的16位信号分高低位分别存储在2个8 bit存储器中,在输出时,按先高后低的顺序输出,从而完成16In8Out的转换,部分实现代码如下:

在信号FS的控制下,FIFO不断地对整帧信号进行刷新,当USB传输信号到来时,刷新当前帧完毕后,开始USB快速读入操作。

2.2.4 USB部分

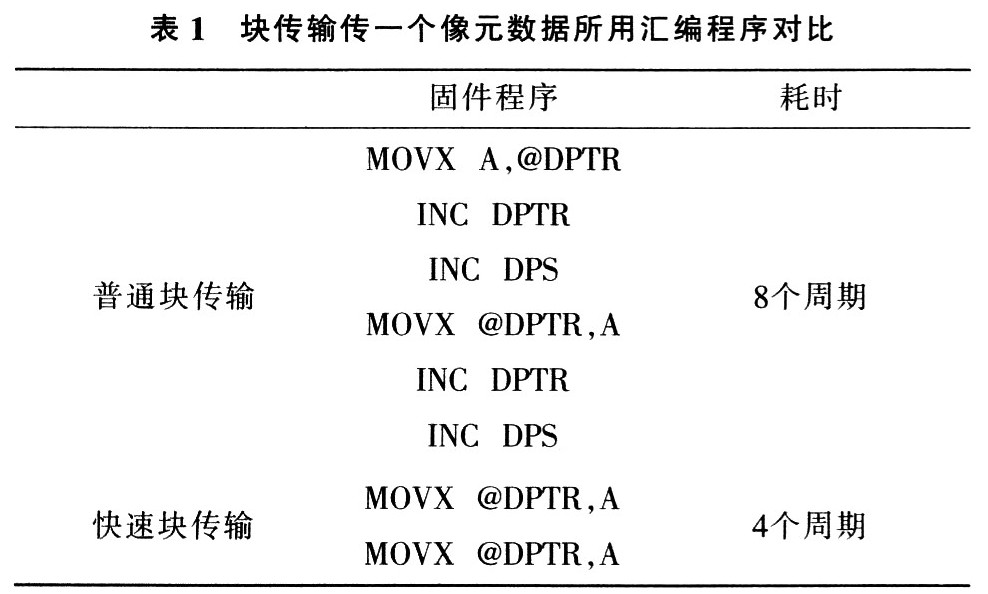

USB采用Cypress公司的AD2131Q,其核提供一种快速传输模式.改进8051的外部逻辑与同步/块端点缓冲器之间的传输速度。将FASTXFR寄存器设置为01010000B,读写选通时序模式为10,提供更宽的脉冲宽度,便于读取FPGA的异步FIFO信号。FIFO存储满1帧数据,由USB器件使用快速块传输上传到计算机,约6 ms完成。表1为块传输传一个像元数据所用汇编程序对比。

2.3 软件设计

软件设计主要包括3方面工作:USB驱动程序设计、动态链接库设计以及应用处理软件设计。

2.3.1 USB驱动程序设计

EZ-USB提供的FPD(通用设备驱动程序)是一个通用的设备驱动程序。利用Microsoft WDM DDK和Visiual C++5.0以上版本就可以修改和编译驱动程序,生成文件ezusb.sys。具体操作如下:①修改驱动程序的PID。在工程里EzUsbDevice.cpp文件中修改PID.VID延用0x0547不变,PID自行设定。②利用hex2c.exe将USB固件Intel HEX记录格式的代码文件转换为C文件,打开该C文件,用其中的firmware[]数组代替在工程里zUsbFirmware.cpp文件中提供的数组。③编译生成ezusb.sys文件并编写相应的INF文件。

2.3.2 动态链接库设计

动态链接库主要是通过I/O控制调用来访问EZ-USBGPD。通过调用CreateFile()来取得访问设备驱动程序的句柄,然后使用DeviceIoControl()提交不同I/O控制码,从而完成USB的控制和输入/输出操作。

2.3.3 应用处理软件设计

应用软件通过访问动态链接库(DLL)获取采集谱线数据,其主要功能有显示、设置积分时间、定格谱线、保存、捕捉、局部放大、添加谱线。

3 测试结果

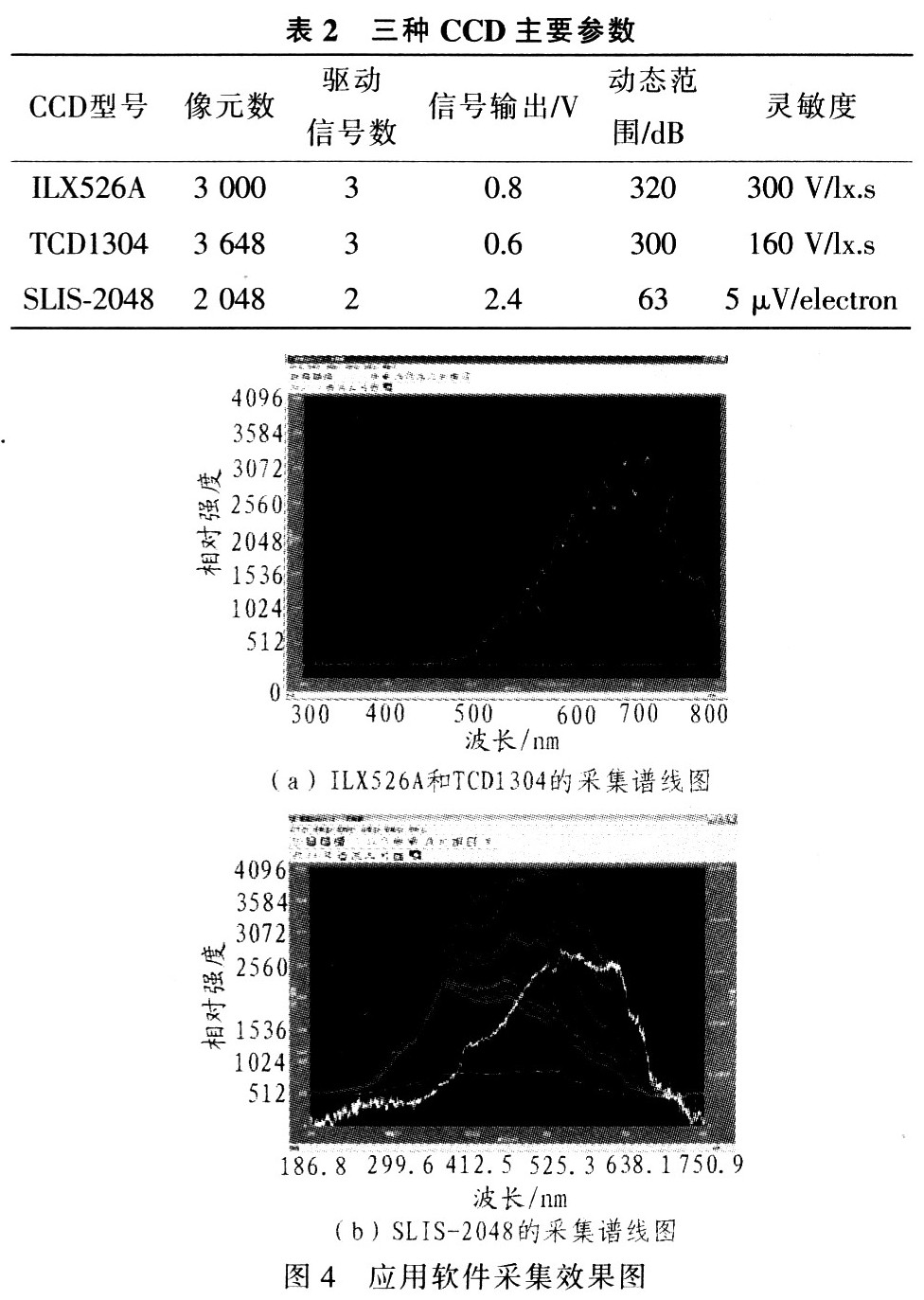

采用通用CCD采集系统分别对3款CCD进行驱动和采集。这3种CCD的参数如表2所示。使用应用软件EMSpectro采集上述CCD谱线,采集效果如图4所示。

4 结束语

采用该系统对3种不同型号CCD成功驱动并采集,测试结果达到了预期的效果。系统体积小、功耗低、兼容性好、可扩展性高。该系统已成功应用于实验室开发CCD相关项目中。