摘要:提出一种基于FPGA技术的多路模拟量、数字量采集与处理系统的设计方案,分析整个系统的结构,并讨论FPGA内部硬件资源的划分和软件的设计方案等。本设计方案外部电路结构简单可靠,特别适用于多路检测系统中,而且可以根据需要容易地对系统进行扩展,对于检测系统来讲具有一定的通用性。

关键词:FPGA;A/D采集;数字量采集;Verilog HDL语言设计

0 引言

在电气测控系统中,常常需要采集各种模拟量信号、数字量信号,并对它们进行相应的处理。一般情况下,测控系统中用普通MCU(如51、196等单片机或控制型DSP)就可以完成系统任务,但当系统中要采集的信号量特别多时(特别是各种信号量、状态量),仅仅靠用普通MCU的资源就往往难以完成任务。本文所提出的一种基于FPGA技术的模拟量、数字量采集与处理系统,利用FPGA的I/O端口多,且可以自由编程支配、定义其功能的特点,能很好地解决采集的信号路数多的问题。

1 系统组成

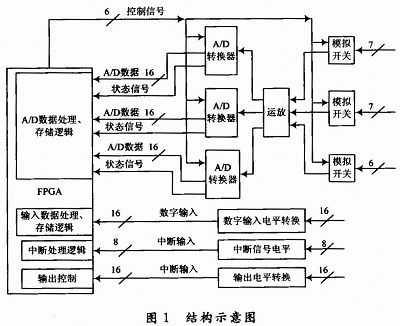

本系统中的外围电路设计相对简单、可靠,且鉴于FPGA自身的特点,系统具有较好的扩展性,在监测和控制系统中也具有一定的通用性。系统主要包括:FPGA芯片区、多路选择与A/D采样电路、时钟电源区、PROM代码下载电路等几部分。结构示意如图1所示。

2 FPGA芯片特点分析及资源分配

本系统中的FPGA是采用Altera公司的EP1C20F400。该系列的内核采用1.5 V供电,I/O端口供电电压为3.3V。

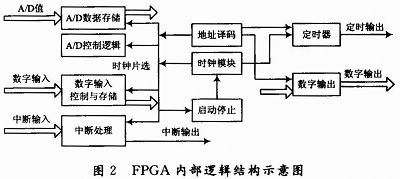

FPGA内部资源划分为四大部分,如图2所示。

(1)FPGA逻辑运算中心。用来接收其他各部分的数据,并按照程序中设定的方案对所收到的数据进行相应的分析和处理。包括:对从MCU接收来的数据指令进行分析,并按其指令要求进行相应操作;接收A/D采样来的数据,对数据进行处理,存储等工作。

(2)A/D控制单元。主要负责控制外部A/D芯片和多路开关的选通时序,以及实现对A/D采要过程的合理控制,利用FPGA实现A/D自动采集与数据存储。

(3)数字量监测控制单元。负责所有要监视和控制的数字量的状态数据的采集和控制命令的输出。这一部分主要实现数字量输出的控制、数字量输入的存储、数字量输入状态变化识别(中断输入)。

(4)FPGA接口逻辑控制单元。在FPGA内部设计了FPGA模块与外界MCU的接口单元,该部分主要用于同CPU的接口,使数据采集系统可以方便的与PCI、ISA及其他总线连接。

3 模拟量采集的控制与管理

在模拟量采集外围电路中,A/D芯片采用的是AD公司的AD976A。多路模拟量是通过AD438的多路开关后输入到AD976A芯片的。

A/D采样部分可分为:寄存器组、时钟发生模块、采样控制状态机、数据存储模块。

3.1 寄存器组

寄存器组用于设置/读取A/D的工作状态,包括:采样频率设置寄存器、工作模式选择寄存器、工作状态寄存器及FIFO中断寄存器。

(1)采样频率设置寄存器Frereg1,Frereg2(R/W):两个16位寄存器,用于设置12路A/D的采样频率,其位含义如下:

频率设置如下:

为保留位。

(2)工作模式选择寄存器modereg(R/W)。176位寄存器,用于设置A/D的工作模式和启动、停止FPGA,各位的定义如下:

(3)FIFO中断寄存器(fifo_int)(R):16位寄存器,用来记录FIFO的状态,各位定义如下:

3.2 时钟发生模块

(1)把时钟分频为1 MHz时钟,作为状态机的工作时钟;

(2)生成20 Hz,50 Hz,100 Hz时钟并结合Frereg的值给出12路A/D启动中断信号。

3.3 采样控制状态机

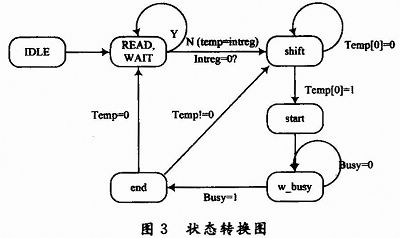

每个A/D用一个采样控制状态机,用于自动控制A/D的数据采集。其状态转换图如图3所示。

IDLE:空闲状态。

READ:temp=intreg,进入下一状态

WAIT:等待中断,如果中断寄存器(intreg)不为0,进入下一状态,否则返回READ。

SHIFT:根据temp[0]的值进行下一步操作,若temp[0]=0则temp>>1,同时通道计数器(counter)加1;若temp[0]=1,则根据counter的值给出通道选择信号,进入下一状态。

START:发出RC=0信号,进入下一状态。

W_BLISY:RC=1,等待A/D转换结束信号,如果结束,temp>>1,发出写FIFO信号,进入下一状态。

END:无效FIFO写信号,若temp=0,表明已无中断,coutnter=0,进入WAIT;否则,counter+1,进入SHIFT。

3.4 数据存储模块

用于存储A/D转换结果,对于每路A/D用一个FIFO。

4 数字采集模块

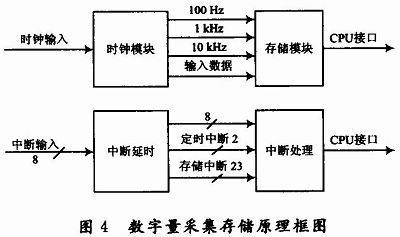

数字采集模块主要完成数字量输入的采集与存储,中断信号状态识别功能。其原理图如图4所示。

5 结论

本文提出了一种基于FPGA技术的多路模拟量、数字量采集与处理系统,设计了相应的外围硬件电路和系统处理软件。在仿真和综合调试成功的基础上,本系统成功用于某重点预研项目的控制系统试验中。试验结果表明,本系统成功地完成了对多路模拟量、数字量的采集处理任务。