将光源、两块长光栅(指示光栅和标尺光栅)、光电检测器件等组合在一起构成的光栅传感器通常称为光栅尺。当两块光栅以微小倾角重叠时,在与光栅刻线大致垂直的方向上就会产生莫尔条纹,在条纹移动的方向上放置光电探测器,可将光信号转换为电信号,这样就可以实现位移信号到电信号的转换。

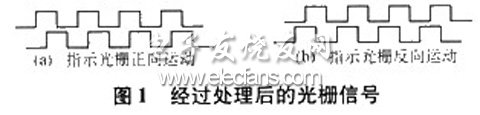

本文针对输出正弦波的传感器进行了讨论,对于输出为正弦信号的光栅尺,需要对输出信号进行整形。光栅尺的输出信号经过整形后如图1所示。

将光栅尺输出的信号进行细分,然后辨向,再送入可逆计数器。由于2路信号周期同为T,相位相差90 °,光栅尺中的指示光栅每移动一个栅距,输出电信号就变化一个周期,如果能够把变化的周期数测量出来,就可以测出相对位移。

2 CPLD的选择

本设计中选择的CPLD(复杂可编程逻辑器件)是Altera公司的EPM 7128SLC84-15,它采用CMOS工艺,是一种基于EPROM的器件。该芯片有84个引脚,其中5个用于ISP(In System Programmable)下载,可以方便地对其进行在系统编程。此器件内集成了6 000门,其中典型可用门为2 500个,有128个逻辑单元,60个可用I/O口,可以单独配置为输入、输出及双向工作方式,2个全局时钟及1个全局使能端和1个全局清除端。EPM 7128SLC284-15支持多电压工作,其中15代表芯片的速度,该芯片传输延时为7.5 ns,最高工作频率为125 MHz,并支持多种编程方式。利用Altera公司的QuartusⅡ5.1软件可以方便地进行仿真、综合和下载。

3 系统实现

本系统中使用的光栅传感器输出的是4路相位差为90°的正弦信号,因此需要对传感器的输出信号进行整形处理。本设计中采用了由运放LM393构成的差分放大器,将光栅传感器输出的4路信号分别送入2个差分放大器的输入端,从差分放大器输出的2路信号其相位差为90°,整个系统框图如图2所示。

将差分后的信号进行整形得到2路方波信号,得到的方波信号不能直接送入计数器中,在本设计中由EPM 7128SIC84-15完成4细分、辨向、计数的功能,在QuartusⅡ5.1中采用原理图的输入方式将上述模块组合成一个软件系统。

3.1 数字滤波电路

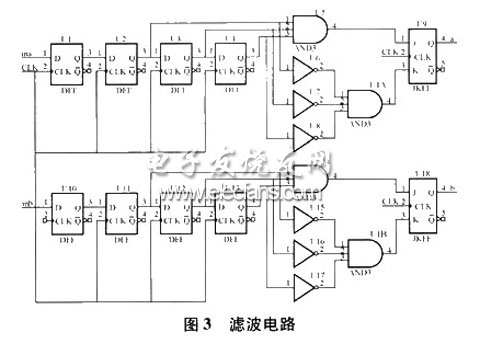

通过多次实验发现,光栅传感器输出的信号虽然经过了前级电路的预处理,但光栅发生抖动或测头被冲击时,仍然会产生噪声信号,从而影响计数的准确性,降低整个测试系统的精度。为了消除噪声信号,在CPLD内部设计了一数字滤波电路模块米滤除抖动脉冲,防止计数器误计数。图3是数字滤波电路图。

该电路的基本原理是用触发器将输入的方波信号通过时钟clk的延迟来克服毛刺和噪声信号,延迟的时钟周期数与毛刺和噪声信号的脉冲宽度有关,需要通过多次实验合理选取。

图4是数字滤波电路的仿真波形图,从图中可以看出,当输入信号ina或inb出现毛刺时,经过数字滤波后,输出波形a和b中已看不到毛刺。在仿真过程中需要注意的足输入信号ina和inb与clk之间的频率设置,如果设置不合适,仿真将会失败。3.2 细分辨向电路

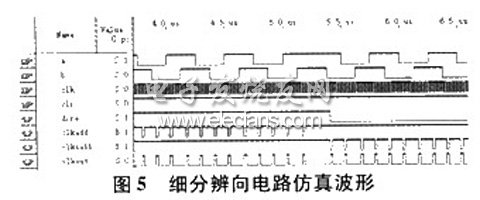

光栅尺信号的细分与辨向足提高光栅尺测量精度的关键性一步,没计者需要综合考虑辨向与细分的复杂性。在辨向时,是对细分后的信号进行辨向,而不是在细分前进行辨向,否则不能提高测量精度。本测量系统中是先细分、后辨向。电路仿真波形如图5所示。

在波形图中:a、b信号足输入波形,clk是系统时钟;clr是系统复位信号;direction是方向信号,通过该信号能够判断出光栅尺中指示光栅的移动方向,如果是高电平,则表示指示光栅作正向运动,反之则作反向运动;clkadd表示指示光栅正向运动时的细分信号;clksubb表示指示光栅反向运动时的细分信号;clkout信号是clkadd和clksubb相"与非"后的结果,该信号作为可逆计数器的时钟信号;当direction为高电平时,叮逆计数器作加运算,当direction为低电平时,可逆计数器作减运算。

3.3 计数电路

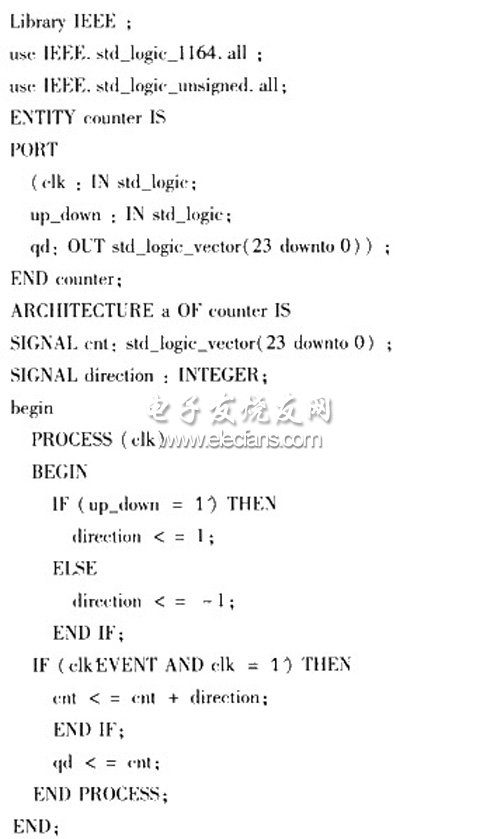

本系统中的计数器采用VHDL进行设计,输入信号定义为时钟信号和方向信号,输出信号定义为24位的计数结果。用VHDL实现的24位可逆计数器功能的原程序如下:

仿真波形如图6所示。

在波形图中:clk信号是上一级电路的clkout信号,作为可逆计数器的时钟;up_down是辨向信号,计数器的加运算和减运算由该信号控制,当up_down为高电平时计数器作加法,否则作减法。

3.4 译码驱动和显示电路

本系统中要正确显示测量结果,需要译码驱动和显示电路模块,泽码电路用于转换24位的计数结果;显示电路需要8个LED显示数据,其中1个LED为符号位。当正向运动时,符号位不显示符号,当反向运动时显示"-"号。

4 结束语

基于EPM 7128SLC84-15构成的位移测量系统具有分辨率高、误差小、电路结构简单、成本低等优点,完全能够满足实际测量的需要。由于采用的是CPLD设计,系统易于升级。