中心议题:

解决方案:

- 建立MOSFET功耗模型

- SR MOSFET关断性能分析

80 PLUS® 计划的推行,要求将开关电源" title="开关电源">开关电源(SMPS)的系统总体能效提高至90%。隔离式电源转换器的次级整流产生的严重的二极管正向损耗是主要的损耗。因此,只有利用同步整流" title="同步整流">同步整流(SR),才可能达到如此高的能效水平。要实现理想的开关性能,必须充分理解SR MOSFET的功耗产生机制。本文分析了SR MOSFET的关断过程,并且提出了一个用于计算功耗以优化系统能效的简单模型。

1. 导言

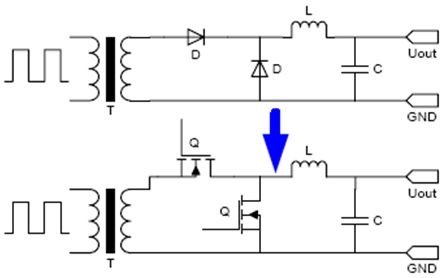

随便看一个开关电源,你都可以在电源转换器的二次侧发现一个整流级。整流级的任务是对经由变压器从SMPS的一次侧转移至二次侧的方波电源信号进行整流。SMPS通常利用功率二极管来实现整流(请参见图1)。但是,功率二极管具有0.5 V乃至更高的正向压降,并且会产生较高输出电流,因此会造成严重的导通损耗,从而大大影响整个电源转换器的能效。为了最大限度地降低这些整流损耗,可以利用最新功率MOSFET来代替二极管。最新的功率MOSFET能够大幅降低导通损耗,特别是在输出电流较高的情况下。在考虑低负载效率时,关注的焦点不是导通损耗,而是开关损耗。因为相比于二极管,MOSFET的开关损耗高得多。对系统能效的其他重要影响来自栅极驱动和旨在遏制关断过程中的过电压尖峰的缓冲网络。这是一个十分复杂的系统,因此,必须深刻理解所有参数相互之间的关系,才能优化系统能效。

图1. 同步整流与二极管整流之比较

2. SR MOSFET关断性能分析

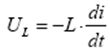

为便于理解SR开关的关断过程,图2所示为几个最重要的波形的示意图。

图2. SR MOSFET的关断性能(按不同开关点分段)

分析首先从开关的导通状态开始:此时,栅极电压很高,漏源电压几乎为零,电流从源极流向漏极。在点1时,栅极被关断。在UDS波形中,这表现为栅极电容CG放电产生的负电压骤降很小。此放电会在MOSFET的源极连接处产生具有大的电流变化(di/dt)的电流峰值。在感应作用下,源极的这种电感会引起UDS波形发生压降。

等式1

等式1

点2时,MOSFET通道关断,然而,在输出扼流圈的驱动下,电流不得不继续流动。这迫使电流转而流向MOSFET的体二极管,使得开关发生负电压降UD。在图2中,这段时间被标记为tD。在点3开启一次侧之后,电流不得不下降。如果一次侧MOSFET的开启速度很快,那么,二次侧的环路电感将限制电流换向,从而形成恒定的di/dt。在这个阶段(tramp),漏源电压波形会出现一个MOSFET的源极电感造成的电压降,并且受负di/dt的影响,漏源电压现在也转为正向。当电流穿过零位线(点4)后,电流不再流经体二极管。因此,二极管上的正向压降也变为零,导致UDS波形再次发生一个值为体二极管正向压降UD的正向压降。穿过零位线后,电流以不变的di/dt保持流动。不过,现在电流的方向为负,正在将体二极管的反向恢复电荷Qrr*移走,并对MOSFET的输出电容Coss充电。在这种情况下,Qrr*仅被视为MOSFET体二极管的反向恢复电荷,而数据手册中的Qrr则是按照JEDEC标准测得的,因此,除体二极管Qrr*之外,还包含部分MOSFET输出电荷Qoss(详细情况请参见第4节)。在对Coss充电的同时,MOSFET的电压也开始朝着变压器电压升高。点5时,达到最高反向电流Irev_peak,也就是说,经过充电现在Coss已经达到变压器电压。在理想状况下,这个系统现在应当处于稳定状态,但是,系统中仍然存在如下电量:

![]() 等式2

等式2

现在,这种感应电量将触发LC振荡电路,并迫使杂散电感Lstray中存储的电量被转移至MOSFET的输出电容,从而产生关断时的过电压尖峰。LC电路的性能取决于变压器的电感、布局、封装和MOSFET Coss,如图3所示。

图3. 电流倍增器SR中的LC关断振荡电路

LC电路的振荡频率为

等式3

等式3

并且,环路的寄生电阻会抑制振荡(Coss = MOSFET的输出电容, Lstray = Lsource + Ldrain + LPCB + Ltransformer)。仅当二次侧的环路电感限制了电流换向时,此处讨论的波形形状才有效。这就意味着,限制di/dt的不是一次侧MOSFET的开启速度,而是电源的二次侧的杂散电感。

3. 建立MOSFET功耗模型

在设计基于SR的高能效电源时,必须准确地知道SR MOSFET中的功耗源自何处。下面,按照理想的MOSFET开关性能,确定了功耗的所有重要来源。

导通损耗取决于MOSFET的RDS(on),可通过如下公式计算得到:

![]() 等式4

等式4

这里,IRMS是流经MOSFET的电流,而不是转换器的输出电流。

为确保两个SR MOSFET之间的互锁,以避免出现直通电流,必须实现一定的死区时间。因此,在开启一次侧之前,必须关断相应的MOSFET。这将导致电流从MOSFET沟道,转而流向MOSFET体二极管,而这又会使漏源极电压发生负电压降(图1)。这段时间被称为体二极管导通时间tD。利用下列参数,即可算出二极管功耗:体二极管的正向压降UD、从源极流向漏极的体二极管电流ISD、体二极管导通时间tD和电源转换器开关频率fsw:

![]() 等式5

等式5

SR MOSFET的栅极驱动损耗取决于栅极电荷Qg、栅极驱动电压Ug和开关频率fsw:

![]() 等式6

等式6

这些损耗是由MOSFET的栅极电荷造成的,而栅极电荷则消散在栅极晶体管和栅极驱动器中。

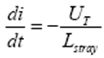

SR MOSFET关断过程中,输出电荷Qoss和反向恢复电荷Qrr*也会产生损耗。其计算公式可从SR MOSFET关断性能的简化模型(图4)推导得到。

图4. SR MOSFET关断的简化模型

通过对电流波形的三角形形状和MOSFET的恒定输出电容的粗略估算,可以计算出MOSFET关断过程产生的电量。如果电流换向受到电感的限制(大多数应用都是这样),则可假定电流波形为三角形形状。要计算在特定变压器电压UT条件下,MOSFET的等效恒定电容Cconst,必须知道时变非线性输出电容coss(t):

等式7

等式7

要计算MOSFET关断过程中的开关损耗,必须首先确定反向电流峰值Irev_peak:

等式8

等式8

根据变压器电压和电流变换环路中的电感,可以计算出di/dt:

等式9

等式9

现在,可以计算出开关电荷Qsw=Qoss+Qrr*:

等式10

等式10

由此推导,可以计算出开关感应电量:

![]() 等式11

等式11

达到电流峰值tIpeak时,杂散电感中会储存感应电量,Coss中也会储存电容电量。因此,可以进行电量比较:

等式12

等式12

然后,这些电量将被转移至MOSFET的输出电容(图4),并在此产生过电压尖峰,继而,这些电量将被LC振荡电路的电阻部分消耗(图1,点6)。于是,可以得出关断过程中的功耗:

![]() 等式13

等式13

计算的准确性取决于MOSFET的开关性能。必须确保不会发生诸如动态开启或雪崩等二次效应。此外,硬开关拓扑可实现最佳结果。任何谐振软开关拓扑均可能导致偏差。在这种情况下,可以对MOSFET进行优化以获得较低RDS(on),因为可以回收利用开关过程产生的部分电量。

4. 体二极管的反向恢复电荷

对于优化能效,MOSFET内部的体二极管具有关键作用。在每个开关循环中,在MOSFET被关断之前,体二极管通常会通电,反向恢复电荷Qrr*也由此积聚起来。在第3节中已经提到,数据手册中所载Qrr与实际Qrr*有所出入。数据手册中的值是按di/dt为100 A/μs测得的,二极管被施以最高漏极电流,并且MOSFET关断前的导通时间长达500 μs左右甚至更长。因此,所测得的值是尽可能最高的Qrr*。此外,JEDEC标准所规定的测定方法不仅包含了Qrr*,而且包含MOSFET的部分输出电荷,因而得到的总值很高,与实际值不相符。需要强调的是,虽然在实际应用中,di/dt可能高达1000 A/μs,并且di/dt越高,Qrr*也越高。但是,Qrr*主要取决于电流和二极管导通时间。由于在实际应用中,电流仅为最高漏极电流的一半甚或更低,并且二极管导通时间仅为50 ns至150 ns,因此实际Qrr*值比数据手册中的值低得多。

图 5. Qrr*与体二极管充电时间的关系

如图5所示,MOSFET栅极定时对实际有效的Qrr*值有很大的影响。在MOSFET关断之前,体二极管通电的时间越长,所积聚的反向恢复电荷就越多。这会降低效率,并且导致更高的关断时过电压尖峰。以图5中所示的第2个解决方案为例。在体二极管导通时间仅为20 ns至140 ns的理想状况下,功耗增加0.5W左右(变压器电压= 40 V,开关频率= 125 kHz),这个功耗会对效率造成显著影响,特别是在低负载条件下。取决于MOSFET技术和体二极管导通时间,Qrr*的影响往往是次要的,因为通常输出电容才是主要的影响因素。另外,数据手册中未提供与应用有关的Qrr值。

5. 优化SR MOSFET以提高效率

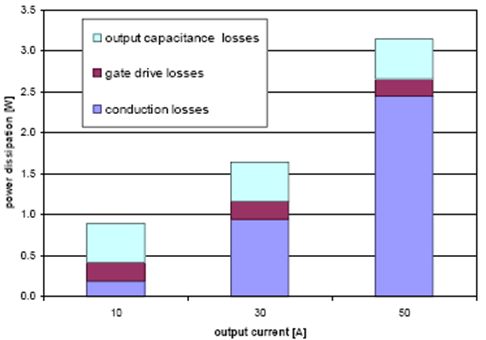

要优化SR MOSFET以提高效率,必须在开关损耗与导通损耗之间找到最佳平衡点。在轻负载条件下,RDS(on)导通损耗的影响微乎其微,因为只有少量电流流经MOSFET。在这种情况下,在整个负载范围内基本保持不变的开关损耗是主要损耗。但是,当输出电流较高时,导通损耗则成为最主要的损耗,其占总功耗的比例也最高,请参见图6。

图6. 不同输出电流条件下的功耗分布(IPP028N08N3 G;fsw = 125 kHz、UT = 40 V)

在选择最适当的MOSFET时,必须特别注意RDS(on)值的范围,如图7所示。当RDS(on)超出最优值时(更高RDS(on)),总功耗将线性增加。而当RDS(on) 降至低于最优值时,总功耗也会急剧上升。此外,在图7中可以看出,可实现最低功耗的RDS(on)值范围相当宽。

图7. 功耗与RDS(on)值的关系(OptiMOS™3 80 V解决方案;VT = 40 V,fsw = 150 kHz,IMOSFET = 20 A,Vgate = 10 V)

当RDS(on)在1毫欧姆至3毫欧姆范围内时,总功耗始终大致相同。但是,在1毫欧姆以下,RDS(on)仅下降0.5毫欧姆,便会令总功耗提高一倍,从而严重降低电源转换器的效率。

图8表明了在实际应用中,不同MOSFET RDS(on) 值范围的影响。图中所示为在服务器电源中分别测得的IPP028N08N3 G和IPP057N08N3 G的值。

图8. 服务器电源中两个SR MOSFET RDS(on) 值范围的实测效率比较

在轻负载条件下,RDS(on) 值较高的MOSFET的效率也更高。这个MOSFET具有较低的输出电容和较低的栅极电荷,因而其开关损耗也更低。另一方面,随着输出电流的提高,其效率将逐渐降低,反而RDS(on) 值较低的MOSFET的性能更好。要在整个输出电流范围内实现最优效率,必须均衡考虑选择最优SR MOSFET。

6. 结束语

本文介绍了一个用于分析开关电源转换器同步整流级的功耗的方法。我们开发了一个简单的分析模型,以用于计算开关损耗。借助这些工具,开发基于同步整流的开关电源的开发人员,可以更有效地选择最优拓扑和MOSFET,可以大致计算SR功耗,能加快设计过程,提高系统能效。