将DDS和PLL技术结合起来,采用DDS直接激励PLL的混合频率合成方案完成了X波段微波变频信号源的设计,一定程度上解决了频率分辨率、频率转换速度和相位噪声的问题,并完成了实机研制、系统联调试验和测试。结果表明,输出信号的频谱和相噪特性良好,达到了预期的要求。

关键词:频率合成;直接数字频率合成;锁相环;相位噪声

0 引言

在雷达型制导导弹的研制和生产过程中,对微波接收机的性能指标进行调试和检测是一个重要环节。为了实现某型雷达制导导弹微波接收机的自动测试,需要一种专用测试系统。X波段微波变频源是该系统的重要组成部分,是决定测试系统性能的关键设备之一。该频率源要能够提供相干的信号源、本振源和镜频源,用来模拟空中目标回波信号,为雷达导引头中微波接收机的技术指标测试以及性能研制提供必要条件。

随着现代电子技术的迅猛发展,低相位噪声、高频谱纯度、高捷变速率和高频率分辨率的频率合成器已经成为频率合成技术发展的主要趋势,直接数字频率合成(DDS)和锁相环频率合成(PLL)技术已成为频率合成技术发展的主流方向。本文提出一种以DDS激励PLL方式实现X波段微波变频源的方案,具有高度的集成性,降低了硬件的复杂程度,提高了系统的整机性能,满足了测试系统的需求。

1 功能和设计要求

1.1 微波源的主要功能

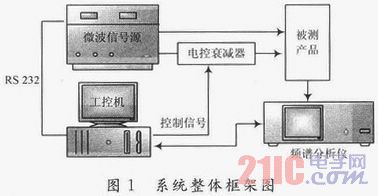

X波段专用微波源主要模拟空中目标回波信号即探测信号、镜频信号和导弹发射机本振信号,能够在控制计算机的控制下,在1 GHz通带内选择201个点频进行变频,微波信号源在测试系统中的构成见图1。

1.2 输出信号要求

微波信号源提供X波段主通道微波前端组件测试所需的相干本振信号、探测信号、镜频信号,每种信号在300 MHz通带内频率可变,具体指标:

频率及带宽相关参数:

(1)信号FS1:f0-fI±150 MHz;

(2)本振fL:f0±150 MHz;

(3)镜频FS2:f0+fI±150 MHz;

(4)中频fI:(28±0.5)MHz;

(5)信号源、本振源、镜频源频率准确度:≤±5 MHz;

(6)信号源、本振源、镜频源频率漂移:≤±5 MHz/4h;

相位噪声:≤-80 dBc/Hz/10 kHz;

杂波抑制:≤-60dB/(300 MHz带宽内);

输出功率:18~22 dBm。

2 设计思路和具体方案

频率合成的实现方法主要有3种,即直接频率合成(DFS)、锁相环频率合成(PLL)和直接数字频率合成(DDS)。其中,DFS技术以其结构复杂,成本高,体积大,而很少使用。DDS具备频率分辨率高,可编程控制特性,并且频率切换速度快,相位噪声低,但是由于其全数字结构,输出频谱质量差,输出频率也较低。PLL具有输出频率高,寄生噪声和杂波低的特点,但是其频率切换速度慢,而且频率分辨率低。为了克服两者的缺点,人们将两种技术结合起来,提出多种DDS和PLL相结合的混合频率合成方案。其中,DDS直接激励PLL方案是最基本的混合频率合成方案,其结构简单,容易实现。所以X波段微波信号源采用了DDS+PLL混合式频率合成方案。

该方案的工作模式是把DDS的输出频率作为PLL的参考频率,通过控制改变DDS的频率控制字或PLL中可编程分频器的分频比,达到系统跳频的目的。它利用高的鉴相频率提高PLL的频率切换速度,并且利用DDS的高频分辨率来保证频率间隔,同时PLL的带通作用可以很好地抑制DDS输出频谱中的部分杂散,实现了DDS和PLL的优势互补。

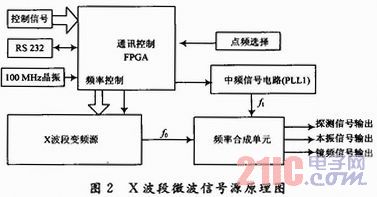

X波段微波信号源包括通信控制单元、中频信号电路、X波段变频源、频率合成单元、供电电源等,微波信号源通过RS 232与工控机通信,信号点频既能手动选择,也能自动控制。X波段微波信号源原理如图2所示。

2.1 通信控制单元

通信控制单元采用现场可编程门阵列(FPGA)编程实现。FPGA具有集成度高,数据处理速度快,系统结构设计灵活等特点,可以根据需要通过布局布线工具对其内部进行编程,将电路集成在一个芯片上,在最短的时间内设计出专用系统。

FPGA通过RS 232与上位机通信,通信接口采用MAX 232实现电平转换,在数据接收端将±10 V电平信号转换为FPGA兼容的TTL电平,在数据发送端将TTL电平转换为±10 V电平信号,满足标准RS 232接口的电平要求。

2.2 中频信号电路

中频信号电路采用数字锁相环实现,100 MHz晶振经过FPGA分频电路生成4 MHz的基准频率作为PLL1的参考频率fPD1,锁相环PLL1的分频比N=7,输出信号滤波后产生项目要求的28 MHz中频。中频信号电路原理如图3所示。

2.3 X波段变频源

X波段变频源采用DDS驱动PLL结构的宽带频率源设计,电路原理如图4所示。

DDS选用AD9854芯片,内置48位相位累加器,并且具有两个内部的高速高性能D/A转换器,通过对外部参考时钟倍频,其内部时钟可达到300 MHz,可以很方便地产生低频的参考信号,并且具有较好的动态性能。

DDS的各种读/写及控制信号由FPGA提供,为了使DDS和FPGA之间的系统时钟同步,它们的外部参考时钟fref由同一个100 MHz的温补晶振提供。DDS输出的信号频率fDDS由FPGA写入的频率控制字控制,锁相环PLL的参考信号由DDS的输出信号驱动,VCO的输出频率由PLL芯片的电荷泵CP输出端控制,通过对VCO输出的信号进行倍频得到X波段f0输出信号。

PLL模块选用ADF4106宽带数字锁相环芯片,ADF4106由低噪声鉴频鉴相器、高精度电荷泵、可编程参考时钟分频器、可编程双模预分频器构成,其带宽可以达到6 GHz,具有较短的频率建立时间和较低的相位噪声,选择低相位噪声的数字锁相环有助于保证整机的低相噪性能。

采用的PLL芯片具有一个双模预置分频器,可产生大分频比,这就使频率综合器在输出较高频率信号的同时仍保持较高的频率分辨率。

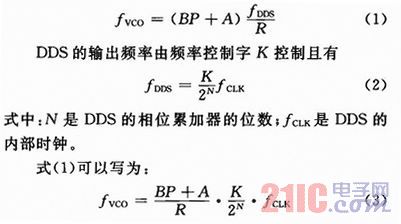

VCO输出信号的频率和DDS输出信号的频率间的关系为:

从式(3)可以看出,采用DDS模块后的输出信号具有比传统结构更高的频率分辨率。

环路滤波器选用AD820运算放大器进行环路滤波器的设计与实现,使用ADISimPLL软件计算环路滤波器各元器件的参数。

2.4 频率合成单元

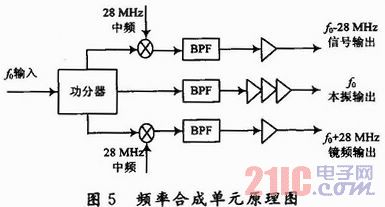

X波段变频源输出的f0信号分为3路,一路经滤波、功率放大后生成本振信号输出,另外两路与PLL1锁相器输出的28 MHz中频信号混频,上变频输出经滤波、功率放大后生成镜频信号,下变频输出经滤波、功率放大后生成探测信号。频率合成单元的X波段功分器、混频器、功率放大器等均采用成熟技术,确保系统稳定可靠地工作,本振、镜频、探测3路输出设计为3个独立的支路,减小信号之间的串扰,采取良好的屏蔽、接地和滤波等措施,以实现高频谱纯度源信号。本振、镜频、探测信号的频率稳定度和频率准确度取决于参考晶振,优于技术指标的要求。频率合成电路原理如图5所示。

2.5 点频选择

微波源频段落在X波段内,提供主通道微波前端组件测试所需的相干本振信号、探测信号、镜频信号,每种信号在1 GHz通带内有201个点频可供选择。所有测试频点参数均由工控机转换为DDS频率控制字通过RS 232下载到FPGA,并存储在FPGA片内RAM的对应地址单元,根据选定的点频,FPGA读取对应的代码,控制DDS输出对应频率的信号。信号点频既能手动选择,也能自动控制。

3 测试结果和分析

根据前面介绍的方案,最终实现了该X波段变频源,图6,图7为该变频源的外观图。

为了测试变频源输出频谱的质量,使用E4440A频谱分析仪测试其输出频谱和相位噪声,频谱和相位噪声测试曲线如图8,图9所示,主要测试指标如下:相位噪声为-86.87 dBc/Hz/10 kHz;杂波抑制小于等于65 dB/(300 MHz带宽内);输出功率为19.05dBm。

测试结果表明,该变频源输出频谱质量优异,完全能满足研制要求的需要。

4 结语

采用本文提出的方案研制出的X波段变频源,体积小,成本低,可靠性高,实现了系统信号的全相参和变频要求,同时输出信号具有低相位噪声、高频谱纯度、高捷变速率的特点,满足了测试系统的需求。