随着人们对高空的兴趣发展和研究需要,越来越多的科学实验被科研人员搬到了空中进行,气球探空和无人机实验是比较典型的方法。这些科学实验往往需要在一定的实验条件到达时触发某特定实验现象,从而对发生时间非常短促且不具备可重复再现性的实验目标数据进行高速采集。日前,笔者参与的项目中需要完成的任务是:通过无线通信实现对高空实验设备进行控制,对整个实验过程进行实时观察分析(其中的实验条件数据通过GPS接收机,红外虚拟逻辑分析仪等设备实时采集),待实验到达触发条件时,通过手动(或自动可选)的方法实施触发,再对触发后的实验目标数据进行采集并传回地面PC进行后续的分析处理。该项目采用ARM和FPGA分别作为主从处理器设计嵌入式采集系统,采用多通道A/D并行采样实验目标数据,系统通过基于串口的无线数传模块与地面实时通信。

1系统硬件设计

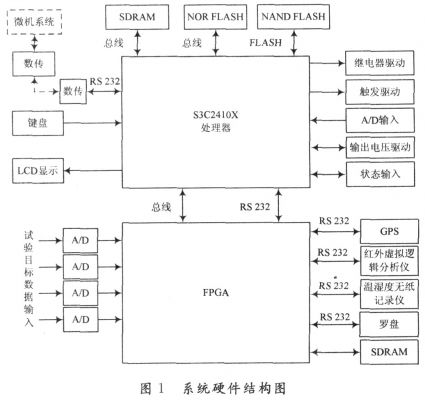

系统的硬件结构原理图如图1所示。

在该系统设计方案中,ARM采用Samsung公司基于ARM920T的S3C2410,其主要技术指标如:支持32bARM指令集和16bThumb指令集;支持32b的高速AMBA总线接口;带有MMU(内存管理单元),可以进行Linux操作系统的移植;MPU支持实时操作系统;采用五级流水线和哈佛结构,独立的16KB指令Cache和16KB数据Cache,具有更高的指令和数据处理能力;支持TFT的LCD控制器、NAND闪存控制器、3路UART、4路带PWM的Timer、8路10位ADC、触摸屏接口、I2C总线接口,以及2个USB主设备接口和1个USB从设备接口等丰富的外围设备和接口。FPGA采用AItera公司StratixⅡ系列的EP2S15器件,EP2S15现场可编程门阵列系列速度快容量高,它采用1.2V,90nm全铜层SRAM工艺和创新的适应逻辑模块(ALM)结构,有最大化的性能,器件密度可达到15600等效逻辑元(LE),能提供419Kb片内TriMatrix存储器,多达12个DSP区块有48(18b×18b)乘法器,用来实现高性能滤波器和其他DSP功能,支持各种高速外接存储器接口,支持各种标准的I/O,高速差分I/O,具有丰富的外部资源以及支持多种高性能标准。

在该系统中,ARM主要负责核心处理和控制,总线实现ARM与FPGA之间的通信,存储器负责程序和数据的存储,其中FLASH存储程序和文件,SDRAM存储系统运行时的程序和数据,ARM通过GPIO连接实验中的相关继电器、触发设备、输出电压控制设备、以及特定设备采样A/D并进行驱动,通过FPGA扩展RS232串口分时控制和读取GPS接收机、红外虚拟逻辑分析仪等设备数据,通过总线连接FPGA并控制FPGA动作来启动和完成数据采集,通过RS232通信接口负责与地面PC的交互。本系统充分发挥了ARM芯片的强大处理能力和FPGA的高速并行能力,成功实现实验目的。

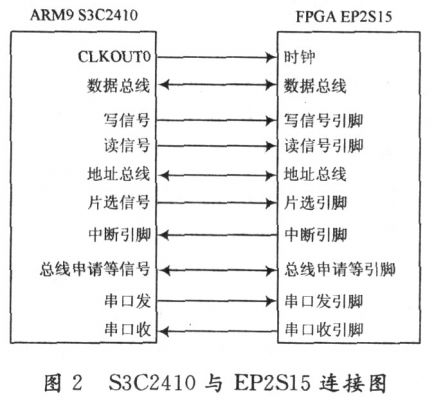

ARM和FPGA的总线接口如图2所示。

S3C2410通过读写总线上的地址来进行指令和数据的传输以控制EP2S15的所有动作。FPGA主要实现通过控制A/D实现数据采集,并保存至SDRAM,对ARM的读写信号进行译码以将实验目标数据读回ARM并传回地面。将EP2S15直接连在S3C2410的存储器总线上,S3C2410可以通过存储器指令访问EP2S15,ARM与FPGA之间的连接除了数据、地址和读写控制外,还有中断信号和DMA控制信号,使ARM可接受FPGA产生的中断和实现DMA数据传输。另外为了扩展S3C2410的串口,将串口连接到FPGA实现对多个设备的分时控制。

2系统软件设计

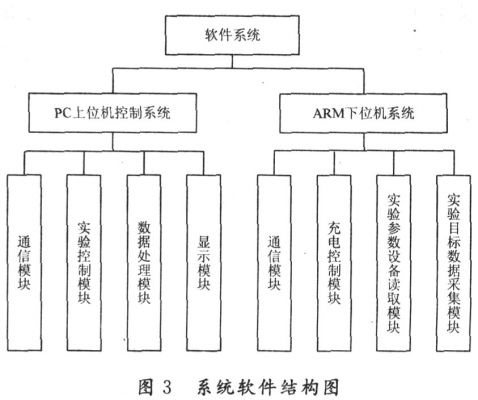

系统的软件结构图如图3所示。

2.1PC机控制程序

(1)通过自定义协议和无线数传模块,对下位机发出各种命令控制实验的进行。

(2)对实时的实验条件数据进行相关处理和显示,以实现对实验运行情况实时监控。

(3)根据实验者要求,定义实验触发条件和方式,并在条件到达时发出警报。

(4)对实验目标数据进行采集和保存,待下一步实验分析使用。

2.2下位机系统程序

下位机程序包括FPGA模块子程序和ARM主体控制程序。

FPGA模块程序又包括对ARM读写指令的译码,对A/D的驱动来采集实验目标数据,对SDRAM驱动以保存实验数据,对中断信号和DMA信号的支持,对串口的设备切换支持。

ARM主体程序包括操作系统和应用程序:为了最大程度利用系统硬件资源,并且保证实时性,在ARM上移植了Linux多任务实时操作系统,内核版本为2.6,完美支持多线程以并行完成实验中的多个控制任务,并且通过修改启动参数以实现控制程序的自动运行;为了方便系统开发调试,该系统移植了基于LinuxUSBGadget的USB从设备驱动,实现了把ARM连接的FLASH当成海量存储设备进行读写,大大提高了开发过程中烧写FLASH的速度,提高了开发效率,并对于地面进行试验性实验的大数据量高速读写提供了支持;设计并实现了用来支持FPGA,A/D设备、相关继电器、触发设备、输出电压控制设备的驱动;并实现了主体应用程序以完成各主要任务。

驱动模块实现中,均采用字符设备方法,对于FPGA的驱动通过IOCTL方法以实现对多端口变长字节数的读写;对A/D设备则通过对连接的GPIO端口(时钟信号和数据引脚)完全按照设备时序进行操作,考虑到实验中特定电压变化并不会骤变,为了数据准确采取多次读取求均值的方法进行;对输出电压控制设备则对内核实现的s3c2410_gpio_set函数进行参考,实现一次调用对多个GPIO端口进行设置,以保证输出电压的精确跳变和控制。

主体应用程序主要包括初始化模块、通信模块、充电控制模块、实验参数设备数据读取模块(GPS等)、实验目标数据采集模块。下面是几个主要模块的实现过程。

(1)通信模块

由于采用基于串口的无线数传与PC机进行通信,项目中采用自定义协议方式,定义了相关的命令字、数据字、参数字的数据格式以及纠错算法和握手协议,对PC机发送的命令进行解析和响应,并启动调用其他实验控制模块,最后将实验所需的数据实时传回地面。

(2)实验参数设备数据读取模块

在初始化模块中把各实验参数设备配置为PUSH模式,以项目中采用的GPS接收机为例,可以配置成以5Hz的速率定时发送符合NMEA协议的GPGGA等数据的模式,每隔一定时间切换串口至GPS接收机读取数据,按照NMEA协议对试验中所需的数据进行解析处理,并保存至指定缓冲区以让通信模块实时发送回地面,其他设备类似操作。

(3)实验目标数据采集模块

在接收到触发命令后,启动FPGA进行采样,通过轮询或中断方式判断FPGA已经采集完毕后,将实验目标数据读至指定缓冲区,进行相关处理后传回地面,为了保证数据准确,可采用重复发方法或较好的纠错方法。

初始化模块主要完成上电后对各实验设备进行初始化,读取PC发送的参数进行设置,其他实验控制模块按照实验规程完成。

3结语

介绍一种采用ARM与FPGA相结合的设计,实现了适用于高空高速实验数据采集的系统,采用S3C2410作为主控芯片,实时地将实验数据传输到地面PC控制平台,地面PC实时控制高空实验过程并进行实验目标数据采集。现场可编程门阵列(FPGA)采用Altera公司StratixⅡ系列的EP2S15器件,在控制4块A/D转换芯片的同时,将数据存贮在SDRAM中,并与S3C2410通过总线传输数据。由于主从处理器都采用功能强大且资源丰富的芯片,为以后的系统升级预留了大量空间。开发过程中可得的丰富资料,减轻了研发任务,提高研发速度,在较短的时间内得到性能优秀的目标系统,目前该系统已投入实际应用,取得了理想的效果。该论文的创新之处在于以新颖的设计结构同时实现了复杂实验过程的控制和高速的数据采集,对S3C2410这款处理器强大的处理能力和丰富的I/O资源充分利用,同时以EP2S15的高速并行处理能力弥补了ARM的不足之处。该系统中的整体设计结构和流程都可以为嵌入式数控行业提供很好的借鉴作用。