1. 引言

说到要求超高性能的前沿应用,就不得不提起ADI公司的SHARC处理器。随着更高动态范围、更高性能和更低成本等市场压力的与日俱增,各种应用对浮点处理器的需求也在不断增加。本文将介绍第一款SHARC处理器背后的历史,并讨论其架构的创新,这使得这款处理器在18年的数字信号处理历史中一直处于领先的地位。

2.SHARC处理器的历史——第一步

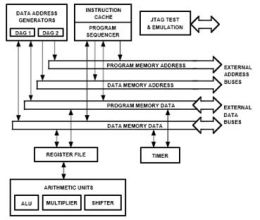

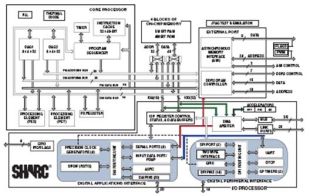

“SHARC”是超级哈佛架构(Super Harvard ARChitecture)的缩写,是ADI公司为他们的浮点处理器起的名字。SHARC处理器在标准哈佛架构基础上作了改进,不仅方便了PM(程序存储器)总线上的数据传送,并通过增加一个指令缓存优化了基于紧密循环的计算过程的吞吐性能。改进后的架构能够同时存取数据和系数,并同时从指令缓存执行所选的指令,从而高效地实现了处理器的三总线操作模式。

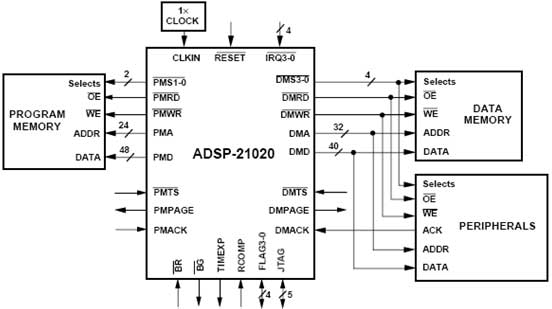

大家知道,SHARC处理器最早起源于ADSP-21020。这个浮点单指令单数据(SISD)DSP实际上是一个不带嵌入式存储器或外设的独立计算内核。PM和DM(数据存储器)存储空间是通过连接到SRAM芯片的外部总线进行访问的,通过JTAG接口对处理器进行编程和调试。

ADSP-21020可以在33MHz时钟频率下工作,执行单周期指令。ADSP-21020可以利用80位累加器完成32位或40位浮点和32位定点运算,是ADI公司在1991年推向市场的突破性产品。这种内核技术是ADI公司对浮点性能和创新做出承诺的起始点。

ADSP-21020架构

ADSP-21020评估系统:注意用于PM和DM空间的外部DIP SRAM组。

集成与创新:SHARC的诞生

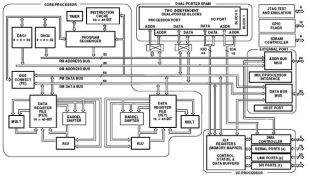

第一款真正的SHARC处理器是ADSP-21060。ADI公司在ADSP-21020内核产品的基础上开发出了一个完全集成的处理器,其中包括了用于控制集成外设的DMA流量的片上SRAM和I/O处理器。

ADSP-21060浮点处理器是1994年进入市场的,当时被认为是DSP性能和创新方面的顶尖水平。

SHARC内核能够在一个周期内以高达40MHz的速度执行计算,并且增加了I/O处理器,能够在不增加任何内核开销的条件下,在外设和双端口4Mb SRAM存储器之间高速传输数据。

为了进一步提高最终用户的系统性能和可扩展性,ADI设计团队着手创建允许多处理器系统能共享数据并且开销很小的机制。在外部端口逻辑中增加了一个簇总线控制器,可以无缝地进行处理器间的并行数据通信,每个簇最多可以有6个处理器。这种突破性技术允许系统架构师以高达240MBps的带宽从主处理器向指定从处理器的内存直接传送大量数据,或使用广播模式向簇中的所有从器件直接发送数据。

使用ADI的链路端口专利技术还能实现处理器间的高速通信。每个ADSP-21060集成了6个独立的链路端口用于点到点通信,因此可以实现额外的240MBps的I/O带宽。

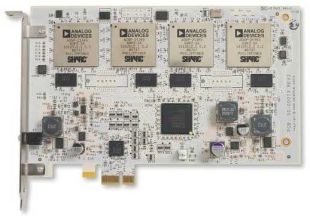

第一代SHARC ADSP-21062评估平台

由于具有这种真正平衡的架构和扩展功能,SHARC处理器被广泛用于运算强度大的应用,如医疗成像、军事雷达和电子游戏机。

也许让人不敢相信,具有这种功能的处理器在15年前就推向市场了,但让许多人更加惊奇的是,这种处理器目前还在继续为用户所用!这是SHARC架构性能的良好扩展性以及ADI公司对质量和用户满意做出承诺的最好证明。

第二代SHARC处理器将处理性能提升到了新的层次,它将内核架构扩展为单指令多数据(SIMD)系统,并将内核时钟频率提高到100MHz。ADSP-2116x系列处理器保持了与ADSP-2106x SISD处理器的源代码的完全兼容性,而且经过少量代码修改就能让用户发挥新增加的并行运算单元(寄存器文件+乘法器+ALU+桶式移位器)的作用,与上一代SHARC相比可以将周期性能指标提高一倍。

为了在不降低周期性能的条件下方便到这个新增加的运算单元的数据传送,内部的PM和DM数据总线宽度都增加到了64位,同时在ADSP-21161上集成了48位宽100MHz SDRAM控制器来增加I/O数据传送带宽,从而能够实现高达600MBps带宽的数据传送能力。

就像上一代SISD SHARC一样,第二代SHARC保留了支持簇总线系统架构的多处理器无胶合连接,以及通过链路端口的点到点连接,使性能升级路线图更加简单清晰。

就像上一代SISD SHARC一样,第二代SHARC系列器件被医疗、工业和军事应用所广泛采用,而且由于额外集成了支持时分复用(TDM)和I2S格式的串行端口(SPORT),专业音响和高端消费/汽车音响设备很快地利用到了该处理器的浮点运算提供的大动态范围优势。

第三代SHARC处理器开始跳出多处理器应用空间,主动迎接新的挑战。由于在音频应用中具有明显的浮点处理优势,SHARC技术开发的重点开始转向以最低系统成本努力增加片上处理功能。

以这个目标开发并推向市场的第一批处理器是ADSP-2126x系列。就像ADSP-2116x一样,ADSP-2126x采用SIMD架构使运算性能最大化。除了将内核性能翻倍达到200MHz外,ADSP-21266处理器还是SHARC系列中首个内置片上掩膜ROM的产品。集成4Mb ROM降低了系统复杂性和成本,将曾经给人们留下“高成本”印象的浮点型DSP推向了消费类音频领域。

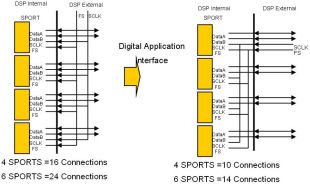

为了进一步降低硬件系统设计的复杂性,ADI公司开发出了名为“数字应用接口”(DAI)的创新性外设。与以前的SHARC和同类竞争性产品将引脚功能固定下来不同,DAI允许用户将任何外设功能分配到他们想要的任意一个外部引脚。对于音频系统来说,这意味着当系统输入输出要求发生改变时,音频时钟域可以随时通过软件分配到引脚并路由到串行端口。这种灵活性可以显着减少为了支持特殊系统规范所需的外部引脚数量,有助于硬件设计的简化,帮助用户进一步降低成本。

第三代SHARC中引入的DAI能显着减少引脚数量和降低成本的例子。

ADSP-2136x继承了ADSP-2126x节省成本的优点,并增加了先进的音频信号链集成方法。内核性能提高了60%以上,达到333MHz,内部SRAM可增加到3Mb。另外还集成了许多针对音频的外设,如高性能异步采样率转换器(ASRC)、SPDIF收发器和DTCP加密引擎,从而进一步优化了可编程性能和音频系统BOM成本,巩固了ADI在音频市场中的领导地位。在这一系列的高性能产品中还集成了工作频率高达166MHz的32位SDRAM接口,以增加I/O带宽,同时有利于数据密集应用使用批量生产的存储器。

基于这种突破性的音频系统集成和性价比领先优势,第三代SHARC系列不仅在专业音频领域,而且在消费音频应用(如家庭影院系统、AV放大器)中得到了广泛应用,为新一代高清音频标准(DTS Master Audio和Dolby Tru-HD)推向市场发挥了重要作用。

基于第三代SHARC ADSP-21369的通用音频处理器模块插件

第四代SHARC系列——ADSP-2146x

第四代SHARC:ADSP-2146x架构框图

第三代SHARC处理器在优化性价比方面取得了成功,推动浮点处理器进入了对成本敏感的消费类应用,而这类应用曾被人们认为是不可能使用昂贵的浮点处理器的。

ADI公司现在面临着一个有意思的挑战:如何进一步改进具备优异性价比的浮点处理器?

在定义第四代处理器时,产品开发团队注重的是核心价值,正是它们使得SHARC一直处于浮点DSP技术的前沿:

· 市场领先性能

· 架构平衡

· 性能可扩展性

· 智能集成

下面将详细介绍上述每个关键的方面。

ADSP-2146x性能增强

在ADSP-2136x系列内核改进的基础上,ADI的SHARC开发团队制定了更高的性能目标,并采用台积电(TSMC)的65nm硅工艺继续优化性能和成本平衡。通过仔细的工程设计和规划,ADI在2008年11月正式发布了ADSP-2146x系列处理器,其内核性能可达450MHz,与最接近的竞争产品相比几乎高出30%。然而,ADI设计团队并不满足于仅仅增强性能,开始寻求创新的方式来大幅度提高运算性能,同时对功耗和成本的影响降至最小。

许多工程师利用浮点处理器提供的宽动态范围实现各种算法,如图案检测、数据压缩/解压缩、加密/解密和自适应滤波。在其中的许多运算密集型算法中,快速傅里叶变换(FFT)、有限冲击响应(FIR)滤波器和无限冲激响应(IIR)滤波器等一些基本的信号处理单元得到了广泛使用,并作为大多数数字信号处理应用的基础。专注于这些内核信号处理构建模块的ADI公司开始将这些功能集成进2146x DMA架构中,以便进一步增强SHARC内核的450MHz性能。

在简单的编程模型基础上,DSP工程师可以将这些“加速器”的每个看作是一个简单的外设。每个加速器配置有自己的本地存储器用于数据和系数存储,从而不会增加内核处理器的开销。另外,还有一组加速器专用寄存器用于设置加速器,包括主存储器中的系数起始地址、计数器等信息。当设置完成后,程序就开始按顺序运行,用户只需简单地等待表示处理结束的中断。

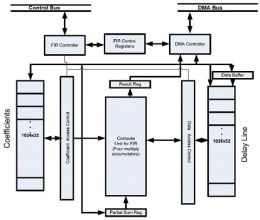

下图是其中一种加速器的例子。

ADSP-2146x系列中的有限冲激响应滤波器加速器

FIR加速器包含一个1K字的本地存储器用于存储系数,另外1K字的存储器用于存储延时线数据。FIR运算单元包括4个并行的MAC(乘法累加)单元,每个单元的工作频率是内核时钟频率的一半。运算单元都能够利用80位精确累加器执行32位浮点或32位定点处理。理论上,除了内核提供的2.7GFlops性能外,这个引擎还能提供1.8Gflops的处理能力。因此与第三代产品相比,第四代产品大体上将可用浮点性能增加了一倍。

FIR加速器可以用于单次迭代模式,这意味着完整的滤波器实现可以适配进本地存储器(滤波器长度<=1024),或者也可以设置FIR加速器以支持多次迭代模式。在多次迭代模式,支持的最大FIR滤波器长度是4096个抽头。为了提高灵活性,用户可用的窗口尺寸变化范围可从1到1024个样本,而针对多速率滤波器(插值/抽取)和多通道滤波器(最多32个信道)的附加模式组成了完整的功能规范。

这种FIR加速器和额外的IIR/FFT加速器为各种信号处理应用提供了创新的低性价比提升方式,再次突出了ADI做出的以最小成本开销实现领先性能的承诺。

ADSP-2146x架构平衡考虑

由于ADSP-2146x系列处理器可以提供2.7GFlops的内核运算性能,存储器密集系统的设计师面临的主要挑战是管理来去各种存储器和外设子系统的数据传送。如果在设计阶段没有考虑这些要求,内核可能由于较慢的大容量存储器而被迫等待新的数据进行处理,或由于多个系统资源存取相同存储区域而导致内核死机。为了尽量减小这些潜在的瓶颈,ADSP-2146x系列内置了最多达67个直接存储器存取(DMA)通道用于外设和内存之间的数据传送。同时集成了工作频率达内核时钟频率一半的16位DDR2接口,使得用于存储密集型应用时的性能最大。这种内核与外部存储器之间的1:1时钟比例极大地促进了数据的快速传送,并且开销很小,还能支持其它功能,比如从外部存储器中直接执行代码。

内部SRAM资源增加到了5Mb,这是所有SHARC处理器中最大的存储器容量。连接内核的带宽仍是7.2GBps,因此保证了内部运算任务的高速执行。这种存储器在架构上被划分为4个不连续模块(模块0-模块3),允许从多个系统资源同时进行零开销访问。

为了进一步优化存储器的使用,ADI开发出了名为VISA(可变指令集架构)的内核增强特性。到第三代处理器为止的所有SHARC用的都是48位的固定指令长度。对于经常使用的指令来说,这会导致非最优的PM代码存储器使用。这些指令经过优化,去除了操作码中的冗余位,产生了新的16位和32位宽指令。程序序列发生器经过更新以识别这些新的优化指令,从而使PM代码效率提高近20%。为了实现后向兼容,VISA模式是源代码编译器的一个选项,这意味着希望保持二进制代码兼容性的用户可以继续使用原来的48位方法学。

所有上述架构增强特性都使系统开发人员能以最佳的、用户友好的方式充分利用ADSP-2146x的高性能资源。

性能可扩展性

ADSP-2146x系列处理器能为系统开发人员选择满足系统成本和性能要求的处理器提供最大的灵活性。这个系列中的所有成员采用相同大小的内部SRAM存储器,允许开发人员保持单一的软件架构,但可以通过选择较少外设或较低性能指标的处理器来优化系统成本。

对于要求的性能超出单个处理器的系统,ADI公司再次引入了链路口技术,以支持可扩展的多处理器平台开发。共有两个链路口可用于处理器间通信,每个端口8位宽,工作频率可达166MHz。这些双向端口可以被编程为发送或接收,不需要外部逻辑,还能用作处理器的引导结构。

智能集成

随着信号处理系统越来越复杂和成本压力的不断增加,处理器开发团队一直在努力利用创新的外设和加速器集成方法提高DSP内核子系统的性能。

如前所述,ADSP-2146x采用领先的创新集成进一步增强了性能,包括FIR/IIR/FFT加速器、高带宽DDR2接口和链路口。

除了已经成为最新SHARC处理器上标准配置的8信道ASRC、SPDIF收发器和串行通信接口(SPORT、UART、SPI、TWI)外,市场关注的一些增强功能也增加进了ADSP-2146x系列产品中。

针对汽车应用,SHARC外设功能组中新增加了媒体局部总线(MLB)接口,以支持汽车下一代的多媒体应用。ADSP-2146x结合了数字传输内容保护(DTCP)协议加速器,可以从MOST系统中的MLB总线接收和发送加密的数字多媒体内容。

针对工业应用,第四代SHARC中还增加了16通道的脉宽调制(PWM)输出。这些PWM模块被安排为4×4输出,可以通过在软件中进行模式编程来支持边缘和中心对齐的波形,并且完全支持停滞时间控制。

第四代SHARC ADSP-2146x评估平台

对于要求在恶劣环境中工作的系统,ADI公司集成了一个热敏二极管以帮助系统设计师直接监视SHARC处理器的硅片温度。通过热敏二极管与ADSP-2146x的可编程PLL功能的配合使用,系统控制器可以监视处理器的温度特性,并且根据要求动态控制处理器的内核时钟频率,从而保持系统规定的温度。

未来的SHARC和浮点处理

在性价比上, SHARC处理器在过去的18年中一直是浮点技术的市场领导者,而ADI公司还在继续投资未来。随着采纳浮点运算的成本门槛的不断降低,上市时间压力的不断增加,浮点的优势(增大的动态范围,自动调整)将继续推动SHARC进军曾经是定点处理器独占的应用市场。

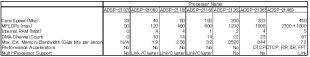

这张表突出表明了SHARC系列处理器的性能和集成演变。

第四代SHARC处理器在不断提升这种成熟架构的性能极限,也充分体现了超级哈佛架构比其它竞争性产品架构更加优越。

作者

Paul Wheeler,GP-DSP部日本区域总监。