随着集成电路设计技术和深亚微米制造技术的发展,集成电路已进入了片上系统时代。由于SoC结构极其复杂,对于设计者而言,数百万门规模的系统级芯片设计不可能一切从头开始,随着集成电路设计技术的发展,IP核的开发己成为不可忽视的发展趋势,它的出现为SoC的实现和发展提供了基础。IP称之为知识产权,它可以认为是封装在硬件设计中的可重复利用的软件,就功能而言,IP核可以定义为SoC的基本电路功能块又称为内核,可由用户或专用IC公司或独立的公司开发而成,IP核的显著特点是具有重用性。鉴于SoC系统设计者很难独自开发、维护和移植所有必须的IP核,所以在Soc设计中必然要用到第3方的IP核,当IP核被转移到用户设计与制造工艺中时,IP核被重复利用了,具有自主知识产权的IP核的复用是Soc设计中解决设计层次、产品成本、设计周期和降低风险的关键环节是SoC设计中的关键技术。IP核重复利用可以提高设计能力,节省设计人员可以缩短上市时间,更好的利用现有的工艺技术,降低成本。基于此笔者设计了基于SoC的音频接口IP模块。

1 APB与IIS总线

APB(Advanced Peripheral Bus)是AMBA(Advanced Microcontrollel Bus Architectrure)组成部分,是用于低功耗和减少接口复杂度而设计的。APB用于带宽,低速,低性能要求,无管线操作的外围设备。APB总线操作包括Setup和Enable两个状态。其中APB读操作只需在Enable状态数据有效,写操作要求写数据在整个写操作期间保持有效。

APB协议规定每个传输只与时钟上升沿相关。这就使APB外围设备很容易被集成在设计之中,特点如下:

(1)在高频操作的性能改进;

(2)独立的脉冲时钟;

(3)静态时钟分析比较简单,因为用单时钟沿触发;

(4)自测试逻辑插入没有特别的条件需要考虑;

(5)在ASIC库中有性能很好的上升沿寄存器;

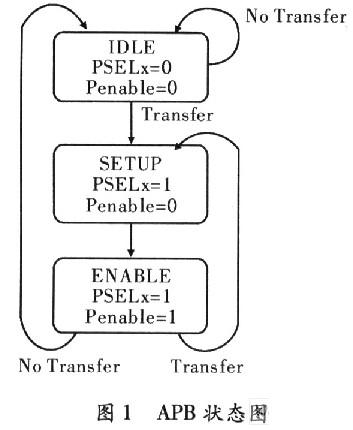

APB状态机,如图1所示。

APB这3个状态描述如下:

IDLE:默认初始状态。

Setup:当有一个传输请求,总线将进入Setup状态,当PSELx,信号被选择。总线只在Setup状态停留一个周期,并将在时钟的上升沿进入Enable状态。

Enable:在Enable状态中,PEnable有效,地址信号,读写信号,选择信号将保持稳定,当状态从Setup到Enable状态。Enable状态仅仅维持一个时钟,如果没有传输发生,系统将回到IDLE,如果有传输发生,系统状态将进入Setup状态。当从Enable状态到Setup状态时允许有短脉冲干扰。

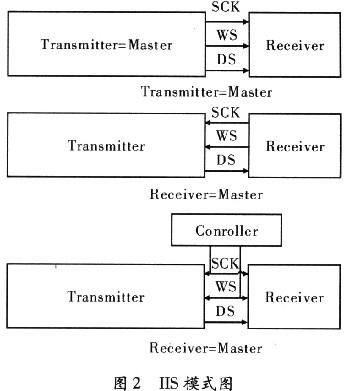

IIS总线:在飞利浦公司的IIS标准中,既规定了硬件接口规范,也规定了数字音频数据的格式。IIS总线拥有3条数据线进行数据传输:数据传输线(DS),选择线(WS),时钟线(SCK)。在数据传输过程中,发送端(Transmitter)和接收端(Receiver)具有相同的时钟信号,发送端作为主导装置(Master)时,产生位时钟信号、命令(声道)选择信号和数据。在综合的系统中,可能具有几个发送端和接收端,使识别发送端比较困难。在这样的系统中,可以设置一个控制器(Controller)来作为系统的主导装置来识别多路的数字音频信号的数据流,此时发送端成为在外部时钟控制下的从属装置(Stave),系统的主导装置也可以与发送端或接收端相结合,这需要通过对硬件或软件的设置来激活。它拥有3种模式,如图2所示。

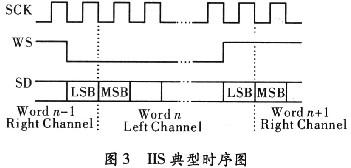

IIS有时序信号图,如下所述。串行时钟信号(SCK):即对应数字音频的每一位数据,SCK对应1个脉冲。SCK的频率=2×采样频率×采样位数。

声道选择信号(WS):用于切换左右声道的数据。WS的频率等于采样频率。

串行数据信号(SD):就是用二进制补码表示的音频数据。

典型时序,如图3所示。

IIS格式的信号无论有多少位有效数据,数据的最高位总是被最先传输,在WS变化,也就是一帧开始后的第2个SCK脉冲处,因此最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。也就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据,如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位(常补足为零)。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。对IIS格式来说数据长度可以不同。

2 音频IP模块设计

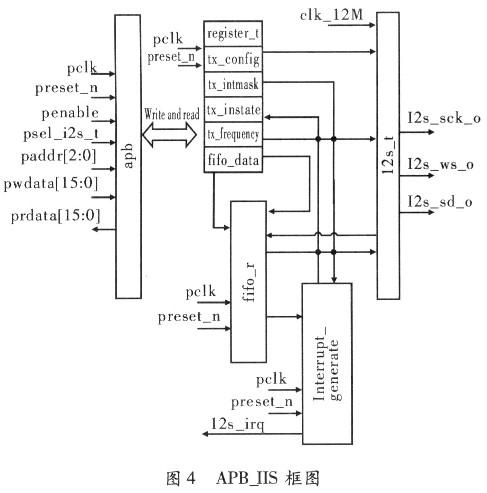

音频IP模块,完成APB总线协议到IIS协议的转换,实现音频的输出,并根据任务要求,设置各种寄存器和中断输出。音频输出模块(APB_IIS)示意框图,如图4所示。

APB_IIS模块由以下5个模块组成:APB接口模块,APB接口模块主要是遵守AMBA协议,完成读写数据的译码。符合APB协议完成寄存器读写,实现寄存器register_t的配置,状态读写。

寄存器模块(register_t),完成各种功能寄存器的设置。register_t模块,包含配置寄存器模块(tx_config),屏蔽寄存器(tx_intmask),状态寄存器(tx_instate),频率配置寄存器模块(tx_frequency),FIFO写数据地址(fifo_data)。

FIFO模块(fifo_t),的功能是从一个高速时钟域到低速时钟域数据的缓冲,并产生标志信号,用于中断产生。

IIS接口模块(i2s_t),i2s_t模块遵守IIS协议,并完成数据的输出。

本模块符合以下功能要求:

(1)传输音频(Transmitter)模块;

(2)主模式,由时钟由外部提供(12 M);

(3)支持时序两种模式音频输出;

(4)分频器实现8/11/12/16/22.059/24./32/44.11/48(kHz)频率数据传输;

(5)内部记数器完成16音频数据的记数;

(6)数据的并串转换。

中断模块(interrupt_generate),中断信号是通过FIFO模块的标志信号和屏蔽寄存器(tx_intmask)信号产生中断信号给系统的中断控制器。

3 仿真结果

图5为APB接口逻辑读写时序和IIS输出时序的局部波形仿真。时序仿真证明符合规范和功能要求。

4 结束语

文中根据协议和实际需求设计一个APB转IIS的模块,具体描述了协议,功能规范,完成RTL代码描述和功能验证,得出正确可移植的音频IP模块。由于模块是有各个分立的模块单元组成,所以再根据实际需求修改模块是非常容易的。